## Data Replication in Hybrid Memory Database Systems

## Dissertation

zur Erlangung des akademischen Grades Doktoringenieur (Dr.-Ing.)

> vorgelegt an der Technischen Universität Dresden Fakultät Informatik

eingereicht von **Mikhail Zarubin, M.Sc.** geboren am 2. November 1988 in Rostow am Don, UdSSR (Russland)

| Gutachter:            | <b>Prof. DrIng. Wolfgang Lehner</b><br>Technische Universität Dresden<br>Fakultät Informatik<br>Institut für Systemarchitektur<br>Lehrstuhl für Datenbanken<br>01062 Dresden |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fachreferent:         | <b>Prof. DrIng. Dirk Habich</b><br>Technische Universität Dresden<br>Fakultät Informatik<br>Institut für Systemarchitektur<br>Lehrstuhl für Datenbanken<br>01062 Dresden     |

| Tag der Verteidigung: | 7. März 2022                                                                                                                                                                 |

Dresden, im Januar 2022

## ABSTRACT

The recent advances in hardware technologies – i.e. highly scalable multi-core NUMA architectures and non-volatile random-access memory (NVRAM) – lead to significant changes in the architecture of in-memory database systems. The novel memory type allows persistent writes while featuring DRAM-like characteristics – byte addressability, high bandwidth, and low access latencies. It is likely to complement or replace the block-based secondary storage (e.g., HDDs or SSDs) for storing the primary data of the DBMS. Therefore, the next generation of highly-performant scalable database systems will rely on single-level hybrid memory (e.g., compound exclusively of DRAM and NVRAM) NUMA architectures and is expected to keep the primary data solely persistent in NVRAM, while query processing could be executed on both mediums. Unfortunately, NVRAM faces certain drawbacks such as a lower write endurance, lower bandwidth, higher latencies, and - most importantly - an increased error-proneness compared to DRAM. Thus, efficient minimal-overhead data protection mechanisms have to be deployed in the underlined architectures to avoid primary data losses.

This thesis provides an analytical overview of such envisioned hybrid memory database systems, gives a survey of reliability techniques that are generally deployed in computing systems, identifies their strengths and weaknesses when used in hybrid memory databases. As a result, this work proposes effective adoption and optimization primitives for the software-managed data replication as the most applicable resilience approach. In particular, research focus is given to runtime and space (and, therefore, NVRAM wearout) reduction of the replication overheads, while preserving strong resilience guaranties and instant recovery opportunities. Subsequently, this thesis proposes a rich set of techniques that leverage data replication for query processing needs to achieve high performance, allocation flexibility and effective hardware utilization in modern scale-up systems. The usefulness of the suggested improvements is thoroughly evaluated and analysed using a variety of low-level and end-to-end benchmarks and proofs-of-concepts.

# CONTENTS

| 1 | ΙΝΤΙ | RODUCTION                                                                                                                                                                                                             | 9                                            |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 1.1  | Motivation                                                                                                                                                                                                            | 10                                           |

|   | 1.2  | Summary of Contributions                                                                                                                                                                                              | 11                                           |

|   | 1.3  | Outline                                                                                                                                                                                                               | 12                                           |

| 2 | BAG  | CKGROUND AND CHALLENGES                                                                                                                                                                                               | 15                                           |

|   | 2.1  | Hybrid Memory Systems2.1.1 Non-volatile random access memory2.1.2 Scale-up hybrid memory architecture on hardware level2.1.3 Scale-up hybrid memory architecture on software level2.1.4 Hybrid memory database system | 16<br>16<br>17<br>19<br>22                   |

|   | 2.2  | Low level performance evaluation of NVRAM2.2.1Socket-local parameters2.2.2Socket-remote parameters2.2.3NVRAM access methods                                                                                           | 23<br>24<br>27<br>28                         |

|   | 2.3  | Vectorized memory accesses in hybrid memory systems                                                                                                                                                                   | 29<br>30<br>30                               |

|   | 2.4  | <ul> <li>Reliability in hybrid memory systems</li></ul>                                                                                                                                                               | 31<br>31<br>32                               |

|   | 2.5  | Survey on existing techniques2.5.1Hardware coding2.5.2Software coding2.5.3OS coding and replication2.5.4Hardware replication2.5.5Software logical replication2.5.6Software physical replication2.5.7Summary           | 33<br>35<br>36<br>37<br>37<br>38<br>39<br>41 |

|   | 2.6  | Observations and challenges                                                                                                                                                                                           | 42                                           |

| 3 | Rep  | LICATION - MINIMIZATION OF OVERHEADS                                                                                                                                                                                  | 45                                           |

|   | 3.1  | State-of-the-art: evaluation and analysis of Intel PMDK replication                                                                                                                                                   | 46                                           |

|    |       | 3.1.1NVRAM-centric data structures3.1.2Pool replication                                                                                                                             | 46<br>48                   |

|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

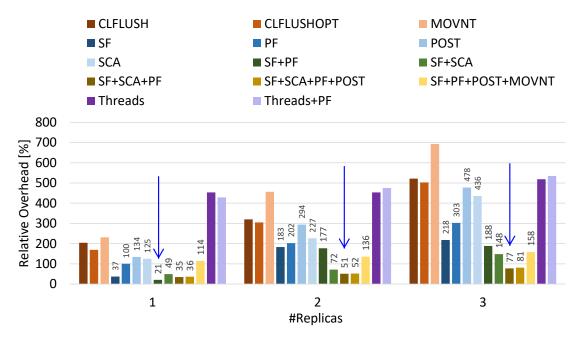

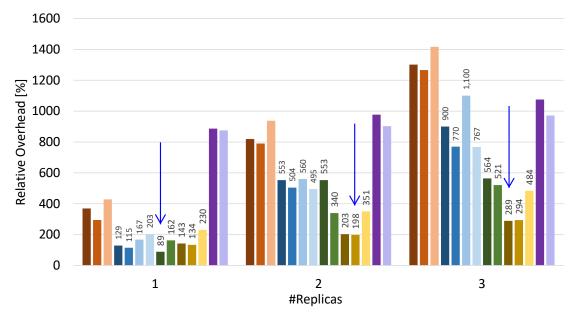

|    | 3.2   | Runtime overhead reduction through adaptive efficient replicationmechanisms3.2.1Optimization of the basic pool replication algorithm.3.2.2Adaptive lightweight switching algorithm. | 51<br>52<br>57             |

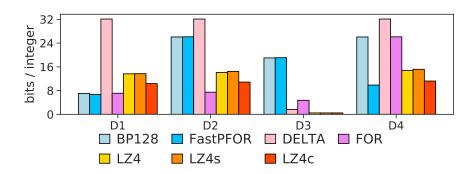

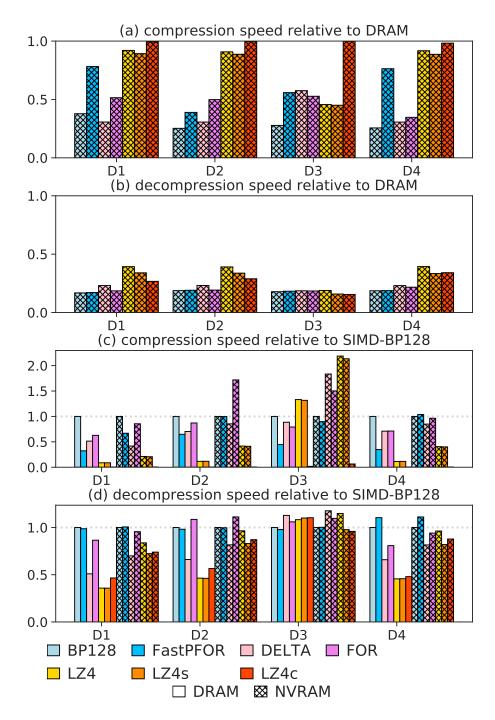

|    | 3.3   | Space overhead and wear-out reduction through data compression3.3.1Integer compression algorithms in hybrid memory databases3.3.2Compressed replication concept                     | 60<br>61<br>67             |

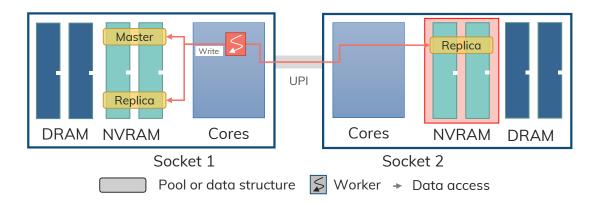

|    | 3.4   | NUMA-aware replica placement as a way to increase resilience                                                                                                                        | 69                         |

|    | 3.5   | Summary                                                                                                                                                                             | 70                         |

| 4  | Rep   | LICATION - QUERY PROCESSING PERSPECTIVE                                                                                                                                             | 71                         |

|    | 4.1   | Underlying system model                                                                                                                                                             | 72                         |

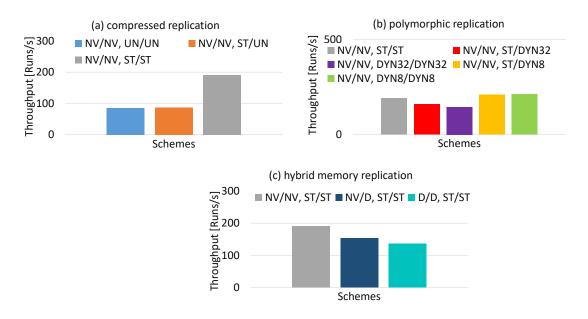

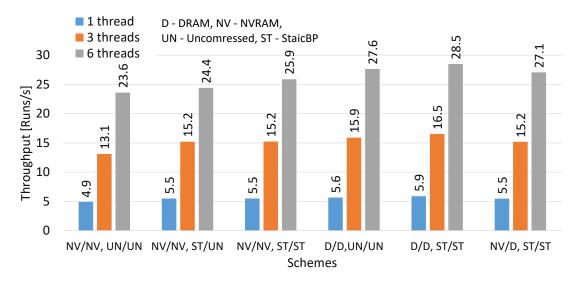

|    | 4.2   | Polymorphic compressed replication mechanism                                                                                                                                        | 74<br>74<br>77<br>80<br>85 |

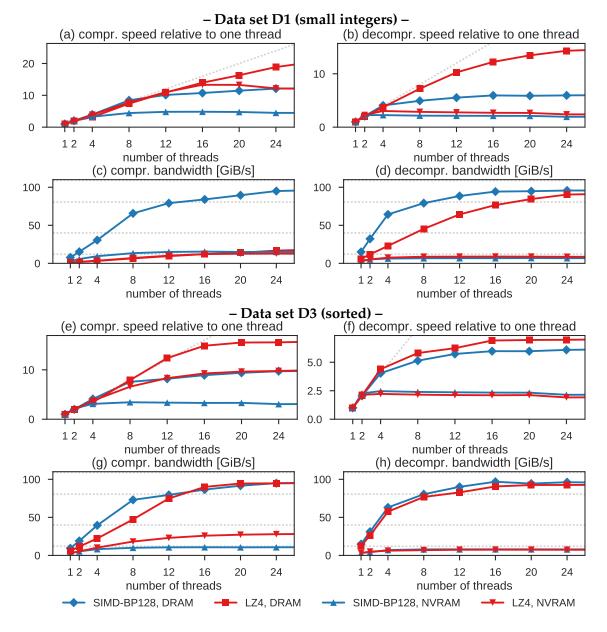

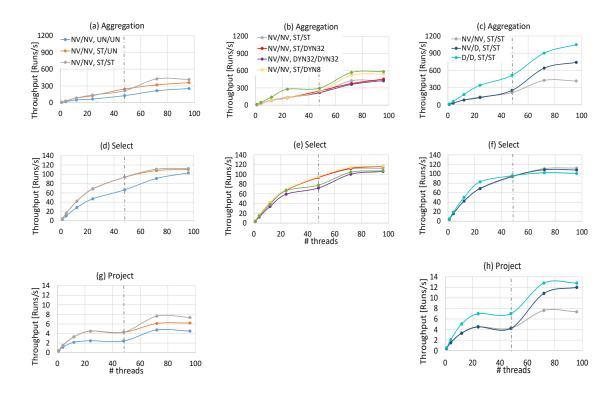

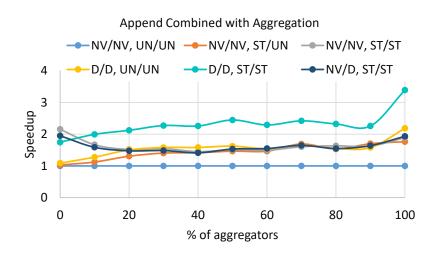

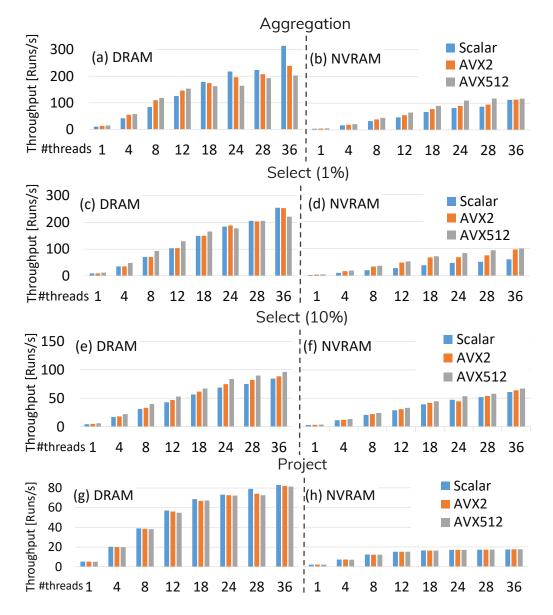

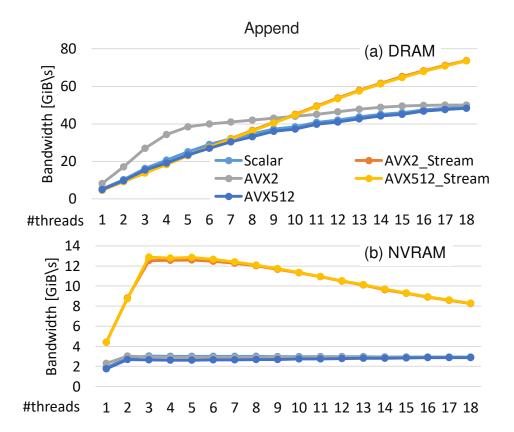

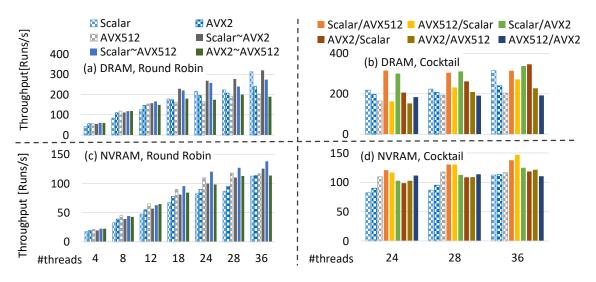

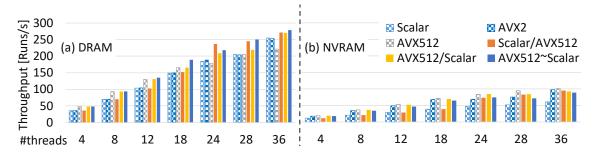

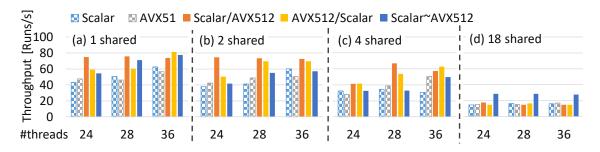

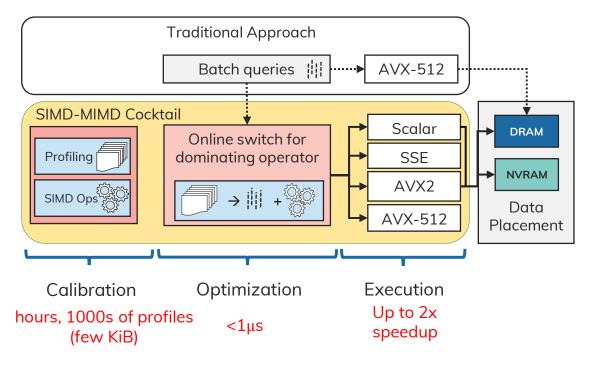

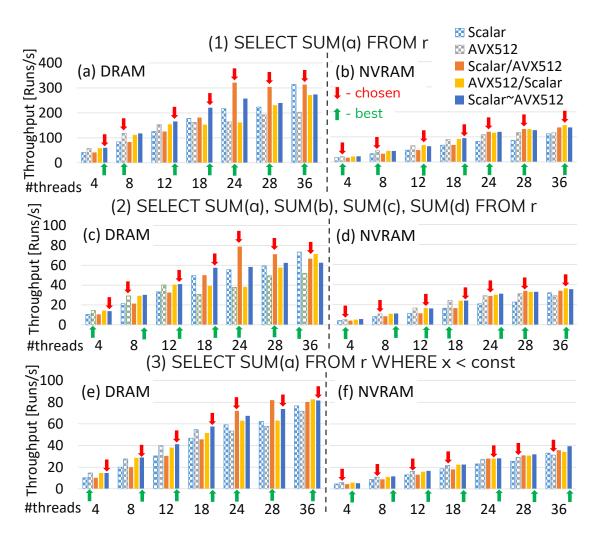

|    | 4.3   | SIMD-MIMD cocktail to speed up query processing4.3.1Motivation for SIMD-MIMD interplay4.3.2Experimental analysis4.3.3Optimizing SIMD-MIMD interplay4.3.4Conclusions                 | 85<br>86<br>87<br>93<br>97 |

|    | 4.4   | Summary                                                                                                                                                                             | 97                         |

| 5  | Co    | NCLUSION                                                                                                                                                                            | 99                         |

|    | 5.1   | Summary                                                                                                                                                                             | 100                        |

|    | 5.2   | Future research directions                                                                                                                                                          | 101                        |

| Bı | BLIO  | GRAPHY                                                                                                                                                                              | 103                        |

| LI | ST OF | FIGURES                                                                                                                                                                             | 113                        |

| LI | ST OF | TABLES                                                                                                                                                                              | 117                        |

# **AKNOWLEDGMENTS**

I would like to thank all my supervisors and colleagues for all their help and advice with this PhD. I would also like to thank all members of my family for all the support I received during the period of doctoral studies.

Mikhail Zarubin January 3, 2022

## INTRODUCTION

- 1.1 Motivation

- 1.2 Summary of Contributions

- 1.3 Outline

## 1.1 MOTIVATION

In modern digitalized world, data is generated in large amounts and is said to be the new oil of the 21<sup>st</sup> century. Thus, in numerous application areas ranging from science to industry, the importance of efficient and scalable data processing increases constantly, whereby traditional *ACID (atomicity, consistency, isolation, durability)* properties of database systems must be taken into account [CDN11]. To speed up the processing of increasing data amounts, the general trend of the last decade is shift towards scalable *in-memory* database architectures [KZZL17, ALR<sup>+</sup>17, Kim15]. Such in-memory databases achieve higher performance compared to those based on traditional disk storage (HDD or SSD). This is due to the fact that they rely on algorithms optimized for main memory, which are normally simpler and faster [KZZL17, KWJP16]. Moreover, processing information that has been stored in byte-addressable memory eliminates the seek time costs when searching and accessing data, compared to block-addressable disk storage.

While being fairly advantageous in many fields that require high-performance or realtime data processing, the in-memory database systems used to suffer two major drawbacks. The first one is the high costs of main memory volumes (e.g., DRAM or SRAM) which are much more expensive than those of disks. The second drawback is a lack of *durability* compliance. This refers to the loss of information in case of power-off. However, over the last years, the cost of DRAM has begun to decline, making the in-memory approaches more affordable and, thus, largely neglecting the first drawback. Furthermore, the recent advance in memory technologies – non-volatile random-access memory (NVRAM) – allows to mitigate the second drawback and provide the full durability compliance within in-memory paradigm.

This novel memory type combines storage-like persistent writes with features of traditional main memory – byte addressability, low latencies and high bandwidth. Due to such advantageous properties, it is likely to complement or replace the block-based secondary storage for storing the primary data of the DBMS. Thus, it is expected that the next generation of highly-performant in-memory database systems will rely on singlelevel hybrid memory (e.g., consisting exclusively of DRAM and NVRAM) scale-up architectures. Besides hybrid memory, scale-up hardware consists of several processing units or sockets interconnected within a single-box compute node [PALG19]. Therefore, targeted applications are potentially able to keep the primary data solely persistent in NVRAM, while query processing could be executed on both mediums. A number of respective changes and adoptions in the architecture of in-memory database systems are already proposed by science and industry [ALR<sup>+</sup>17, Kim15]. Such changes result in a modified in-memory approach, which is further referred by this thesis as a *hybrid memory database architecture*.

On the one hand, NVRAM allows to greatly extend available byte-addressable capacities on affordable prices while still facing certain drawbacks. Those are higher latencies, lower bandwidth, lower write endurance and - most importantly - an increased errorproneness, compared to DRAM or SRAM. On the other hand, the data durability and consistency require to deploy efficient minimal-overhead data protection mechanisms in the underlined architectures.

Thus, the goal of this thesis is to adopt or propose reasonable data protection mechanisms for hybrid memory databases. As at this point in time, respective safety measures (with regard to NVRAM) are not yet well researched. So, the thesis starts with a survey of resilience techniques that are generally used in information processing systems, explores their potential strengths and weaknesses when applied to hybrid memory database systems. And as an outcome, this work proposes effective deployment and optimization primitives for the software-coordinated physical data replication as the most applicable reliability approach. With regard to the data storage model the investigations rely on a columnar data organization [BMK99, BZN05, HDU<sup>+</sup>19, SAB<sup>+</sup>05] as the most efficient state-of-the-art format in analytical in-memory processing systems.

The emphasis is given to the compute node-local (e.g., addressed within single-box scaleup machine) minimization of runtime and space overheads of the data replication process, while preserving strong resilience guaranties and instant recovery opportunities. Subsequently, this thesis suggests a rich set of techniques that leverage data replication (particularly in compressed data formats [AMF06, GRS98]) for query processing needs to achieve high performance, allocation flexibility and effective hardware utilization in modern scale-up systems (e.g., via deployment of multiple sockets). Additional attention is paid to the single instruction multiple data vectorization as performance optimization opportunity for physical replication and other in-memory database operations [PRR15, ZR02, DUP<sup>+</sup>20]. The applicability of the proposed improvements is thoroughly evaluated using a variety of benchmarks and proofs-of-concepts.

## 1.2 SUMMARY OF CONTRIBUTIONS

This thesis targets concepts and low-overhead mechanisms for provision of data reliability guaranties in hybrid memory databases, being run on scale-up hardware architectures. Furthermore, the deployment opportunities of redundant data copies for query processing needs are precisely researched. In addition, several benchmarks and proofof-concept prototypes are used to evaluate proposed solutions. The contributions can be summarized as follows:

- 1. First, the thesis details on the foundations of both envisioned hybrid memory database systems and targeted scale-up hardware architectures. Because of the novelty of NVRAM memory within modern hardware landscape particular attention is given to the low-level evaluation of its performance characteristics to make a foundation for the efficient scale-up system level integration.

- 2. Based on the initial explorations, the principles of how the data reliability could be ensured for such novel data processing applications are revised, compared to traditional architectures. This is done via the discussion and qualitative analysis of resilience approaches that are generally deployed in computing systems. As a result, that survey concludes that the software-managed data replication is the most applicable reliability technique. Further, a number of important research challenges are drawn when attempting to integrate respective protection mechanism in hybrid memory database systems.

- 3. The ultimate goal is to minimize the *runtime* overhead of the data replication process as thorough evaluation of the state-of-the-art implementation demonstrates prohibitively low performance for the targeted domain of high-speed hybrid memory databases. Thus, the detailed insights on sources of the runtime replication overhead are provided. Furthermore, this thesis suggests a rich set of optimization primitives to reduce the performance penalty of replication for typical database workloads. These optimizations are subsequently automated using a template-based approach to adapt for current workload conditions.

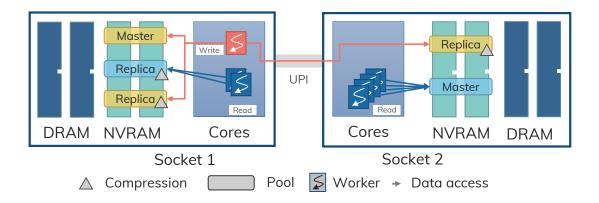

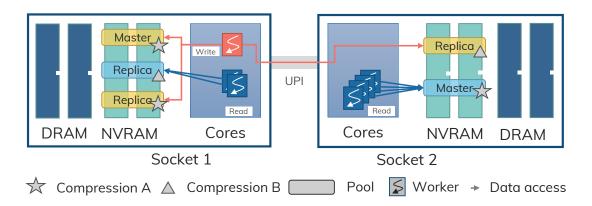

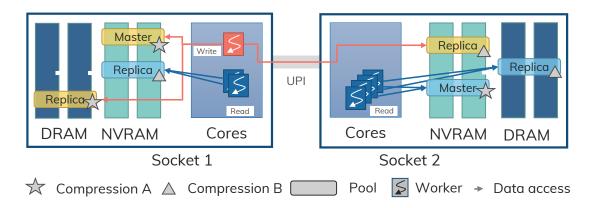

- 4. To reduce the *space* overhead of the replication (which normally implies at least 100% of additional storage per replica), this thesis investigates the opportunities of data compression in NVRAM-centric data stores focusing on lightweight integer compression techniques. Such algorithms are widely used in DRAM-backed columnar processing systems. Subsequently, a *polymorphic compressed replication* concept is suggested to store replicas using a variety of compressed data formats and, therefore, to average possible space reductions.

- 5. The scale-up hybrid memory database systems are able to persistently store and to efficiently process data exclusively in main memory. These specific properties enable the *immediate* on-demand usage of replicas for other than reliability purposes. Thus, this thesis derives a conceptual vision on how compute node-local physical replication, while efficiently facilitating the primary data protection, could be leveraged for query processing needs as well. In particular, it suggests to allow data processing operations on (possibly compressed) replicas flexibly allocated over the sockets of scale-up server. As evaluated, that allows to significantly speed up concurrent workloads and improve hardware utilization.

- 6. As all the data (including replicas) processed by the database operators in targeted systems is stored on byte-addressable mediums it is directly exposed to the available CPU instructions. Thus, the data level parallelism or *single instruction multiple data (SIMD)* vectorization could be deployed for optimization of NVRAM-centric operations similarly to DRAM-backed in-memory databases. The usefulness of SIMD instructions is researched by this thesis not only for physical data replication, but also for query processing on persistent replicas. Furthermore, a novel concurrent SIMD-heterogeneous query execution model (SIMD-MIMD cocktail) is proposed to outpace the traditional SIMD-homogeneous performance.

- 7. The usefulness of the suggested improvements is thoroughly evaluated and analyzed using a variety of low-level and end-to-end benchmarks and proofs-ofconcepts. In particular, the suggested *polymorphic compressed replication* and *SIMD-MIMD cocktail* approaches are evaluated within the MorphStore<sup>1</sup> – a prototype of an in-memory query processing system for columnar data developed at the Chair of Databases of the TU Dresden.

## 1.3 OUTLINE

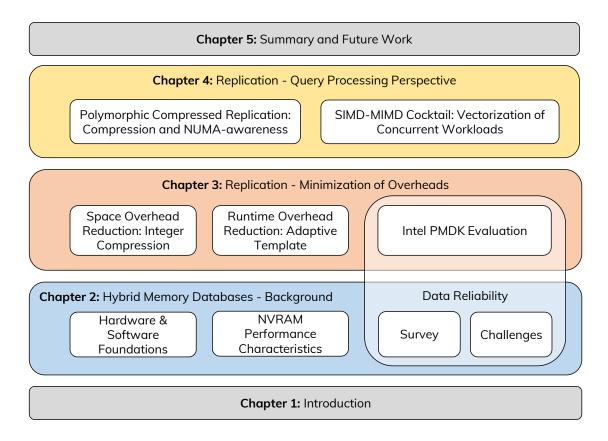

Figure 1.1 visualizes an abstract outline of this thesis. The corresponding structure matches in part with the previously presented summary of contributions. Introduction aside, the remaining part of the thesis is compound of the following blocks. Chapter 2 provides the necessary background on the key technologies and architectures addressed in the thesis. In particular, it presents the non-volatile random access memory technology and its influence on modern hardware architectures. Further, it discusses the deployment challenges from the user software point of view and expected integration advantages in the database domain. As a conclusion, this chapter stresses the need for effective protection of NVRAM-resident data and draws the respective research challenges tackled further in the thesis.

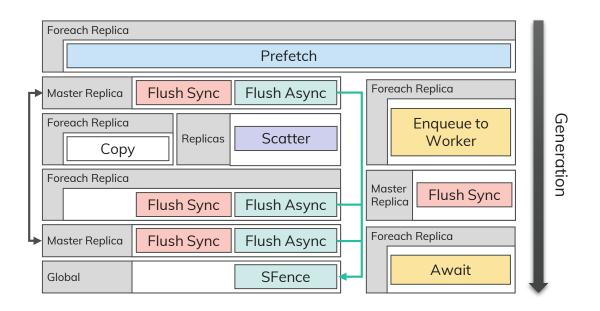

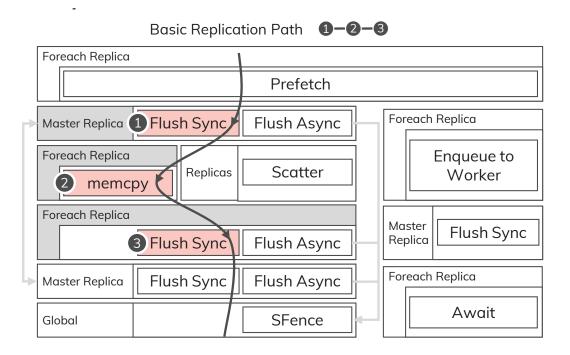

Chapter 3 focuses on a compute node-local synchronous physical replication as the most reasonable for hybrid memory systems resilience approach. Namely, it evaluates the

<sup>&</sup>lt;sup>1</sup>https://github.com/MorphStore

Figure 1.1: Thesis structure and outline.

state-of-the-art implementation and presents the compute node-local mechanisms to provide the foundation for an efficient NVRAM replication with a low latency and throughput penalty. Further, the evaluation and adoption of the lightweight integer compression techniques are provided to ensure the space footprint-minimized replication. Finally, this chapter proposes flexible NUMA-aware allocation for stronger protection of persistent base data against all possible NVRAM failures. The evaluation of the proposed in this chapter ideas is embedded in respective sections for better integrity and consistency.

Chapter 4 describes a conceptual vision on how the compute node-local physical replication, while efficiently providing the base data protection, could be deployed for query processing purposes as well. The research starts with the discussion of the underlying system model, and then proposes and evaluates two options for the replicationrelated query processing optimizations. First option (polymorphic compressed replication) leverages the *storage* component (via diversity in data layouts), while second (SIMD-MIMD cocktail) proposes to rely on *compute* counterpart (via diversity in available vectorized instruction set extensions). The evaluation of the suggested in this chapter ideas is integrated in respective sections as well.

Chapter 5 concludes the thesis with a summary of this manuscript. Finally, an outlook for the most promising future research directions, that could complement or expand the contents of this thesis is provided.

## BACKGROUND AND CHALLENGES

- 2.1 Hybrid Memory Systems

- 2.2 Low level performance evaluation of NVRAM

- 2.3 Vectorized memory accesses in hybrid memory systems

- 2.4 Reliability in hybrid memory systems

- 2.5 Survey on existing techniques

- 2.6 Observations and challenges

This chapter<sup>1</sup> gives the necessary introduction to the key technologies and system architectures addressed in the thesis. Particularly, it presents the novel persistent memory technology, its impact on modern hardware architectures, deployment challenges from user software point of view, and expected integration advantages in the database domain. As a conclusion, this chapter stresses the motivation and research challenges tackled further in the thesis.

## 2.1 HYBRID MEMORY SYSTEMS

This part provides the necessary background regarding the non-volatile random access memory as a key enabler for the hybrid memory systems, which are presented subsequently from both hardware and software perspectives.

#### 2.1.1 Non-volatile random access memory

This section is devoted to the description of the recent <sup>2</sup> storage/memory hardware advance – non-volatile random access memory (also known as persistent memory, storage class memory or non-volatile main memory). Further in the thesis, the term *non-volatile random access memory* is used to address a set of underlined hardware technologies that provide byte-addressable access to the persistent devices attached directly to CPU memory bus.

A general trend, currently observable in many memory-based data intensive applications like in-memory databases, key-value stores, data warehousing, and analytical processing tools is the growing demand for hardware platforms with increasingly larger memory volumes [MMNLM20]. This need reflects the general processing style of such systems, as they tend to constantly have most of the data in main memory, in contrast to disk-centric architectures. On the other hand, the technological process used to scale the frequency or capacity of modern volatile main memory devices is facing its physical limitations [Loh08, QSR09]. To tackle this challenge, industry is intensively researching and integrating new memory technologies. One of the most notable recent developments is non-volatile random access memory (NVRAM).

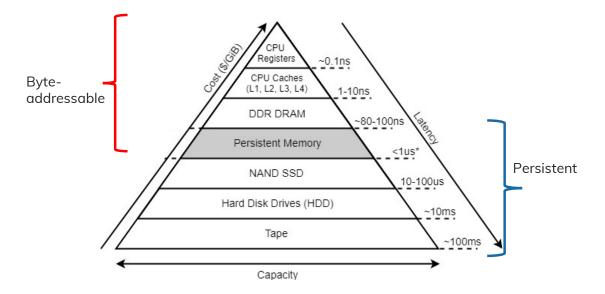

In essence, NVRAM is a random-access memory that retains data without applied power. Such durability is a novel feature compared to dynamic random-access memory (DRAM) and static random-access memory (SRAM), which have been dominating volatile random access memory technologies over the last decades, as both maintain data only for as long as power is applied. The term *random access* means that the access latency is equal for all internally stored bytes. To complement such volatile memories and provide persistency property the computing systems conventionally used block-addressable (accessed over the slow I/O bus) storage devices such as solid state drives (SSDs), hard disk drives (HDDs) or magnetic tapes. Therefore, nowadays, NVRAM is able to close the gap between persistent and volatile memory classes and transforms the traditional memory hierarchy pyramid of Von Neumann architecture [GH93] as illustrated in Figure 2.1. Namely, NVRAM combines features of both – byte-addressability, low access latencies,

<sup>&</sup>lt;sup>1</sup>Parts of the material in this chapter have been developed jointly with Thomas Kissinger, Dirk Habich, Thomas Willhalm, and Wolfgang Lehner. Namely, Section 2.2 is based on [ZKH<sup>+</sup>19]. The copyright of [ZKH<sup>+</sup>19] is held by Springer-Verlag GmbH Germany, part of Springer Nature; the electronic version of the article is available at https://link.springer.com/article/10.1007%2Fs00778-019-00549-w.

<sup>&</sup>lt;sup>2</sup>as of year 2021

Figure 2.1: Memory hierarchy pyramid indicating the place of persistent memory (adopted from [Sca20]).

durability, and high capacities. Such combination is particularly interesting and promising in several domains of science and industry (e.g., data processing applications, high performance computing). The goal of this thesis is to examine it from database systems point of view taking into account not only its advantageous features, but also drawbacks such as limited endurance and increased, compared to DRAM, error-proneness.

There is a variety of actively developed hardware technologies which goal is to provide NVRAM-required properties. Those include Ferroelectric RAM [BAKS16], Magnetoresistive RAM [Hei14], FeFET [PLH21], Spin-transfer Torque [FKV<sup>+</sup>16] and others. However, the most stable and already applied in real hardware technology is Phase Change Memory (PCM) [WRK<sup>+</sup>10]. PCM is an NVRAM, mainly based on chalcogenide glass, and is sometimes referred to as CRAM. Such chemical substances fills up the memory cells and are able to change the phase state. This state switching in PCM is based on the presence of two different solid-state phases, i.e., crystalline and amorphous with different electrical resistivity. The information-storing ability in phase change cells is provided by the transition between the low resistive crystalline phases to high resistive amorphous phase [GS20]. The transition is induced by the high temperature, and can hold several intermediate states representing up to four bits per memory cell.

#### 2.1.2 Scale-up hybrid memory architecture on hardware level

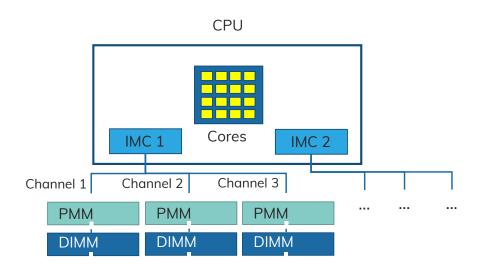

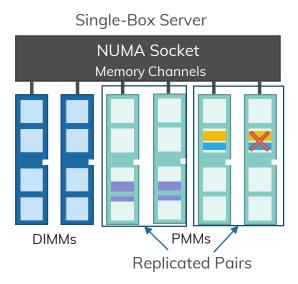

In the next sections this work relies on the Phase Change RAM devices from Intel named *Optane DC Persistent Memory* as a physical ready-to-use implementation of NVRAM hardware. These devices are currently shipped using the *non-volatile dual in-line memory module (NVDIMM)* packaging also known as *persistent memory module (PMM)*. The NVDIMMs mostly follow the traditional DRAM DIMMs hardware interface [Dim21]. Therefore, they are directly attached to the memory buses similarly to DRAM as illustrated by Figure 2.2. Precisely, this example denotes the current state-of-the-art (though, not the only possible) attachment scheme of persistent memory modules to the integrated memory controllers (IMCs) while using the shared connection to memory channels. Thus, each channel serves a pair of DRAM and NVRAM units. In such a machine

Figure 2.2: Typical attachment scheme of NVDIMMs in a single socket machine.

the CPU is equipped with 2 identical IMCs enabling 6 memory channels in total. The coexistence of the two byte-addressable memory types within a single architecture makes it actually *a hybrid memory system*. And in the considered example NVRAM is placed next to DRAM (or at a same level of memory hierarchy) that reflects a *single-level* hybrid memory approach.

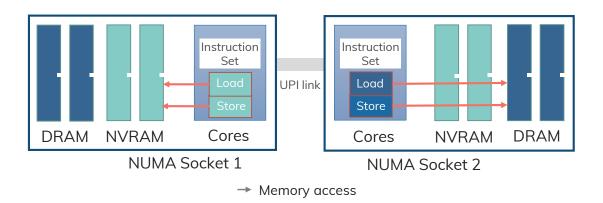

One of the fundamental requirements for the modern high performance server systems is *scalability*. The scalability is the property of a system to handle a growing amount of work by adding resources to the system [Bon00]. The state-of-the-art method applied in practice for scaling up hardware in terms of compute cores and memory resources is known as as non-uniform memory access architecture (NUMA). This approach (also referred as *scale-up multiprocessor system*) physically partitions compute cores and assigns local hardware memory resources to each partition or socket [PALG19]. Thus, the NUMA architectures implicitly assume that higher performance is enabled in combination with a certain *parallelism* paradigm that make use of such partitions [PRR15]. There are three sources of parallelism provided by modern scale-up hardware: thread parallelism [Pac11], instruction-level parallelism [PM13], and data parallelism (discussed further in Section 2.3).

The NUMA processors or sockets are connected using an interconnect network (e.g., Unified Pair Interface [Int09]) that typically increases the response time when accessing memory of a remote socket. Such increases are referred to as a non-uniform memory access behavior. Several previous works prove that considering the NUMA effect is crucial for competitive data processing performance [KZZL17, PJHA, KKS<sup>+</sup>14b]. In principle, NUMA-oriented scale-up systems behave like distributed systems, but feature a faster communication due to cache coherency facilities and the close proximity of processors. Thus, the near-memory processing paradigm (NMP) is state-of-the-art on such platforms [KZZL17, PJHA, KKS<sup>+</sup>14b]. That means, NMP restricts data access to memory-local compute resources and only the unavoidable communication is performed via interconnects.

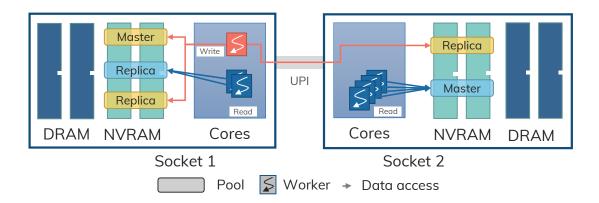

In such scale-up systems, which are now becoming a standard in the field of high performance server architectures, each local memory domain consists of DRAM and NVRAM at the same hierarchy level [DKK<sup>+</sup>14] making them actually *hybrid memory* systems. As a conclusion, both mediums are directly exposed to the multi-core CPUs, whereby every

Figure 2.3: Schematic view of 2-socket hybrid memory system.

core may feature a full set of available instructions (e.g., load, store, vectorized extensions, etc..). Such placement enables a unified memory access style on both mediums as shown in Figure 2.3.

For completeness it is important to notice that, in principle, NVRAM could be mounted as a slow extension of DRAM capacity [Nvr20] (violating its persistency property), intermediate cache level between DRAM and I/O storage [CB18], or just as a fast blockaddressable device similarly to flash memory devices (sacrificing its byte-addressability). However, these are not mainstream options and obviously may hurt the advantages of using NVRAM in the field of highly-performant database management systems. Therefore, in the following this thesis relies on the *single-level hybrid memory approach*.

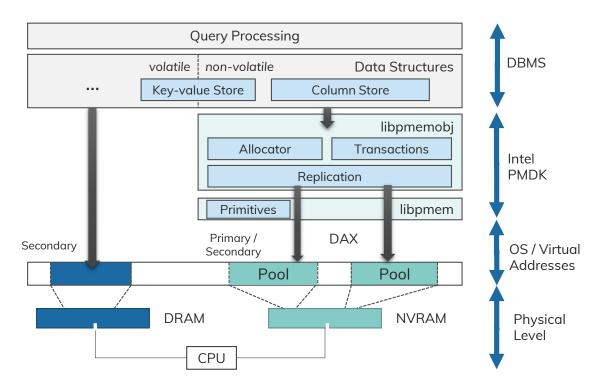

### 2.1.3 Scale-up hybrid memory architecture on software level

To enable the effective exploitation of the described above hardware architectures in a variety of application domains, the software counterpart needs certain support or modifications compared to traditional (DRAM for processing, disk for persistency) approach. That applies to both operating system and user program levels. The basic requirements for such conversion, as well as main adoption principles are provided by Storage and Network Interfaces Association (SNIA) NVRAM programming model [Sni17]. The most important and relevant concepts are discussed below, while the actual focus is given to NVRAM-related issues within hybrid memory systems, as DRAM counterpart basically mimics the in-memory processing paradigm.

**Access Methods.** As already mentioned above, there is a number of alternatives in a way how NVRAM can be architectured in the system. The most important softwaredefined options are shown in Figure 2.4. Under Linux, the NVRAM resources are provided in the system through specialized *NVDIMM driver*, while OS-level administration is done via the *ndctl* command line utility [ndc21]. Further, the deployment of persistent memory as a storage would require an application to use either standard raw device access [ndc21] or standard file-based API via conventional or persistent memory-aware file system [XZM<sup>+</sup>17]. However, to efficiently access physical NVRAM as a main memory in byte-addressable way (using *load/store* semantics), current Linux kernels (as well as Windows and MacOS) implement the *Direct Access* (*DAX*) functionality. This feature maps physical NVRAM regions into the virtual address space of an application while bypassing kernel page and block-level caches. The following three specific ways of accessing NVRAM in byte-addressable mode are available in Linux-like OS:

| Mgmt.              | St                               | orage                | File Memo               | ory              |

|--------------------|----------------------------------|----------------------|-------------------------|------------------|

| Management UI      | Application                      | Application          | Application             |                  |

| Management Library | Standard<br>Raw Device<br>Access | Standard<br>File API | Standard<br>File API    | User<br>Space    |

| 2N                 | 10                               | File System          | PM-Aware<br>File System | Mitig<br>Megonga |

|                    | NVD                              | IMM Driver           | <u>م</u> ش              | Kerne<br>Spac    |

|                    |                                  | 12                   |                         | _                |

|                    |                                  | Persistent Me        | mory                    |                  |

DAX – Direct Access

Figure 2.4: SNIA-recommended NVRAM deployment methods (adopted from [Sca20]).

- **DAXDEV.** A DAX device is similar to a raw disk access. In this case, the complete region of the device is designated to one persistent pool. The pages of the NVRAM region are contiguously mapped into the address space of the application without any intervening file system.

- **DAXFS.** The DAXFS access method requires the region of NVRAM to be formatted with a DAX-enabled file system (e.g., EXT4 or XFS) and individual files are mapped into the virtual address space of the application without intervening kernel page caches. Similar to the DAX device, this access method requires the NVRAM to be configured in *AppDirect* mode [Nvr20] whereby it is made explicitly visible as main memory to the operating system.

- **SHM.** While the previous access methods require a specific physical memory region to be defined as NVRAM at boot time, the *shared memory (SHM)* access method uses arbitrary DRAM memory pages (via tmpfs file system) and is thus solely meant for DRAM-based NVRAM emulation.

**Persistency Mechanisms.** Because of the *DAX* feature, virtual memory pages are directly mapped to physical NVRAM pages and thus, no system calls are required to persist modified data to the NVRAM. However, the presence of volatile CPU caches requires explicit cache line write backs to ensure the persistency of a modification. Moreover, to implement such persistent flush mechanism in a consistent way, the cache line eviction has to be strongly ordered via fence commands to prevent possible out-of-order execution of store instructions. There are several alternatives to ensure consistent persistent flushing on current x86 processors:

- **CLFLUSH.** This instruction writes back a specific cache line and evicts it from the cache hierarchy in the coherency domain.

- **CLFLUSHOPT.** This instruction was introduced to support weakly-ordered higher performance flushes as optimized version of CLFLUSH, which is synchronized by previously issued CLFLUSH commands. The advantage is that multiple cache lines can be flushed concurrently, thus, exploiting instruction-level parallelism. Nevertheless,

this command requires an additional SFENCE or MFENCE instruction to ensure the completion of all previously issued CLFLUSHOPT instructions, and, therefore, prevent write reorderings. However, this requirement plays a protective role and does not specify an exact number of CLFLUSHOPT operations served by a single fence.

- **CLWB.** This instruction asynchronously writes back a specific cache line *without* explicit eviction. CLWB also requires an SFENCE or MFENCE to ensure its completion.

- **WBNOINVD.** The instructions of this family are only executable in kernel mode (or privileged OS mode) and write back all modified cache lines either with or without eviction. The WBNOINVD instruction is currently available on the Icelake server CPU generation.

- **MOVNT.** The non-temporal MOV instruction bypasses the caches and stores data directly to the memory. MOVNT is a single instruction multiple data extension (SSE2, AVX, AVX2 or AVX-512) that is also executed out-of-order and thus requires an SFENCE or MFENCE to ensure its completion.

- **PAT.** *Page Attribute Tables* (PAT) are used to control the caching behavior of memory pages and have been originally implemented for writing to device memory (e.g., frame buffers). PATs can be leveraged to automatically write back certain memory locations without the need of explicit cache line flush instructions. However, this mechanism exhibits a poor performance according to the measurements using a patched Linux kernel supporting PAT configuration for NVRAM mappings.

**Persistent Memory Allocation.** The volatile memory allocation is a well-understood and thoroughly-studied research topic. The variety of general purpose industrial and tuned-up scientific allocators are available. However, there are several reasons making DRAM allocators invalid for straight use in combination with NVRAM. Those are the following:

- **Recoverability.** Unlike to the data stored in the volatile memory, where the virtual pointers addresses are preserved only while the program is running, NVRAM-resident objects are supposed to survive the application termination or crashes. That calls for a recoverable addressing space when providing persistent memory volumes. Such a recoverability could be provided via specialized allocation schemes that extends traditional pointers (e.g., returned by *malloc()* call) with durable fixed anchors (e.g., pool starting address) via memory mapped files (attached using *mmap()* call).

- **Leakage.** As mentioned above, NVRAM-allocated chunks has to survive all termination scenarios. That implies to the fact that if memory leaks (independently of the actual reason) it will retain durably inaccessible, as there is no OS garbage collection mechanism for persistent volume. Therefore, additional measures have to be implemented on both allocator and application sides to monitor actual state of the allocated chunks and release leaked pointers.

- Atomic Updates. The persistent memory leakage could result from the incorrect programming but also from the power loss or OS-induced crashes. These reasons could also leave the user content of persistent memory in an inconsistent state if an update operation was terminated. On Intel hardware, the atomic persistent store is 8 bytes. That means if the program or system crashes while an aligned 8-byte store to persistent memory is in operation, on recovery those 8 bytes will either contain the old contents or the new contents. Thus, another important issue within NVRAM-related programming is to ensure the atomicity of persistent updates. That is normally solved applying transactional style in modifications (e.g., complete or nothing). Such transactions could be supported on allocator level deploying 8-byte atomic instructions.

The discussed above challenges of persistent memory allocation, access and management are addressed in specialized allocators [MAK<sup>+</sup>13, SBF<sup>+</sup>15, YXD<sup>+</sup>17, YXD<sup>+</sup>15, BCB16, AvR18, DBY<sup>+</sup>19], tool-kits [Rud15], as well as on the data structure level [OLN<sup>+</sup>16, OL17a, VTRC11, Vig14, CGN11, CJ15, YWW<sup>+</sup>16, KSKN18].

**Scale-Up Deployment.** Previous paragraph described the NVRAM-relevant issues in software adaptation and development. To fully exploit NUMA resources of *scale-up* hybrid memory systems it is also required to support usage of multiple sockets in terms of both memories and multi-core CPUs. These challenges are already addressed in DRAM-baked NUMA-aware applications [KKS<sup>+</sup>14a]. Thus, due to the byte-addressability property of persistent memory, it is natural to extend the existing concepts and solutions (e.g., NMP and *libnuma*-like NUMA-aware memory management [lib20]) for NVRAM domain.

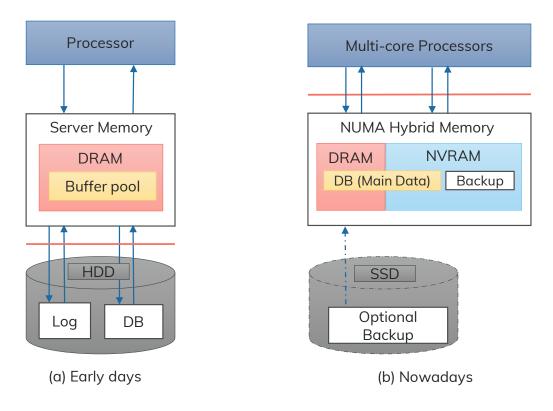

#### 2.1.4 Hybrid memory database system

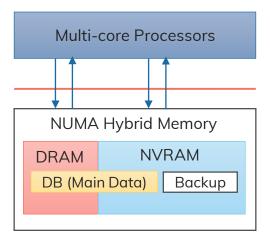

After presentation of the necessary background on hybrid memory systems, it is finally possible to introduce the respective DBMS applications that are expected to be accommodated by such systems. The high-level vision is given by Figure 2.5. Here, the main conceptual difference from classical DB architecture is that there is assumed no blockaddressable persistent storage device. So, all the primary data including back-ups is placed in byte-addressable NVRAM, that replaces the traditional storage elements. Further, similarly to DRAM-backed in-memory DBMS applications [KKS<sup>+</sup>14a], the data processing and query execution can be done in fast volatile memory (that would require moving or copying of certain amount of persistent primary content to DRAM pool) or, novelly, directly in persistent domain as it is now byte-addressable [Kim15, ALR+17]. The latter approach, however, calls for more careful data processing procedures as there could be no further safe copy of base data. Therefore, not only medium failures but also errors during query execution (independently of their origins) may lead to the corruption of primary data. Nevertheless, such innovative "completely in-memory" architectures offer a great potential for highly-performant data accesses and instant recovery opportunities (especially if the DBMS state variables are also accommodated by NVRAM) and, thus, are the subject for further investigations in this thesis.

Data and Processing Model. With regard to the data organization model it is envisioned that such hybrid memory database systems, similarly to most of the modern in-memory applications, would favor columnar format [ABH<sup>+</sup>13, AMF06, DKB<sup>+</sup>19, LMF<sup>+</sup>16, RAB<sup>+</sup>13, ZHNB06, KD18]. Here, the relational data is maintained using the decomposition storage model (DSM) [CK85], where each column of a table is stored separately as a fixed-width dense array [ABH<sup>+</sup>13]. To allow easy reconstruction of the tuples of a relational table, each column record is stored in the same (array) position across all columns of a table [ABH<sup>+</sup>13]. Column-stores typically support a fixed set of basic data types, including integers, fixed-, or floating-point numbers, and strings. For fixed-width data types (e.g., integer, fixed-, and floating-point), column stores utilize basic arrays of the respective type for the values of a column. However, floating-point numbers are usually mapped to integers [ABH<sup>+</sup>13] as well. Variable-width data types like strings are generally dictionary encoded and represented as integers, which enables their storage into fixed-width columns, too [ABH<sup>+</sup>13, BHF09]. In the simplest case, a dictionary consists of the distinct values of a column, sorted by frequency, and each value is represented as its integer position on the dictionary [ABH<sup>+</sup>13]. Consequently, all base columns consist of a sequence of fixed-width integers.

For an efficient processing of these integer sequences, the column-at-a-time model is heavily applied in such systems [ABH<sup>+</sup>13, BKM08]. Here, an SQL query is translated into a query execution plan (QEP) consisting of multiple operators. Typical query operators include select, project, aggregate, join, group-by, and set-operations featuring a mixture of sequential and random memory accesses for reads and writes. Each operator consumes one or two input columns and produces an output column called intermediate. The column-at-a-time processing model explicitly materializes these intermediates, because each operator within a QEP is evaluated to completion over its entire input, before subsequent data-dependent operators are invoked. Such intermediates are volatile columns and thrown away during or right after the query execution. Thus, the application distinguishes between persistent *base data* and ephemeral *intermediates* in this system model. However, the DBMS still has the flexibility to place any column either to DRAM or NVRAM arbitrary, thanks to hybrid memory concept. Nevertheless, on scale-up platforms such placement is expected to follow the NMP paradigm (cf. Section 2.1.2).

## 2.2 LOW LEVEL PERFORMANCE EVALUATION OF NVRAM

Because of the novelty of NVRAM devices within modern hardware landscape – it is important to acquire a good understanding of its performance characteristics to make a foundation for the efficient scale-up system level integration. This section, therefore, thoroughly examines basic socket-local and -remote behavior of persistent memory and compares it with the volatile counterpart for clarity.

**Hardware Setup.** All experiments in this section are executed on a dual-socket system featuring Intel Xeon Scalable (codenamed Cascade Lake) processors clocked at 2600 MHz, 384 GiB DDR4 DRAM memory and 1.5 TiB Intel Optane DC Persistent Memory. Each processor has 24 physical cores (48 w/ HyperThreading). The PMMs are plugged into the system in accordance to the "2-2-2" scheme meaning that each of the three channels of an integrated memory controller (IMC) is attached to a DRAM and NVRAM memory module as shown in Figure 2.2. Each processor features two IMCs and thus all 6 channels can be operated in an interleaved mode to achieve the maximum NVRAM and DRAM bandwidth. As operating system this experimental setup runs a Fedora 27 with kernel version 4.15. While the binaries are compiled using g++ 7.1.3 with enabled "-O3" optimization flag.

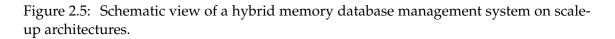

Figure 2.6: DRAM and NVRAM read bandwidth for a sequential and random (8 Bytes) access pattern. The results show the maximum bandwidth measured by multiple threads in parallel.

### 2.2.1 Socket-local parameters

**Local Read Bandwidth.** Figure 2.6 shows the maximum read bandwidth achieved by multiple threads (count of 48) on the local socket using a sequential and a random (8 Bytes accesses) memory access pattern each for DRAM and NVRAM. It is observed that the sequential as well as random access DRAM bandwidth is about 3x higher compared to the NVRAM bandwidth. Moreover, workloads using a random access pattern with an 8 Byte access granularity (amount of data accessed in a single read) are only able to achieve 2% of the sequential access bandwidth in the NVRAM as well as DRAM case. The cause of this huge difference is that (i) hardware threads face the full memory latency between the accesses, because the next cache line can not be prefetched, (ii) the internal block-size for data transfers between CPU and memory is an entire cache line (64 Bytes) for DRAM as well as NVRAM, and (iii) the *adjacent cache line prefetch* feature automatically loads the subsequent cache line resulting in a 128 Bytes (two cache lines) data transfer for an 8 Bytes access.

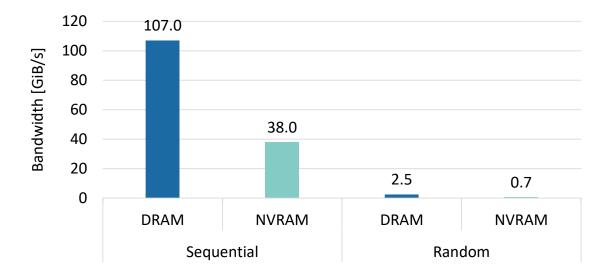

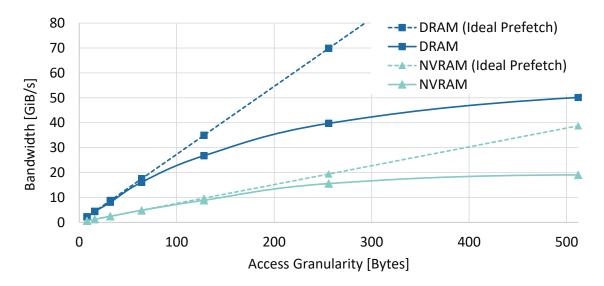

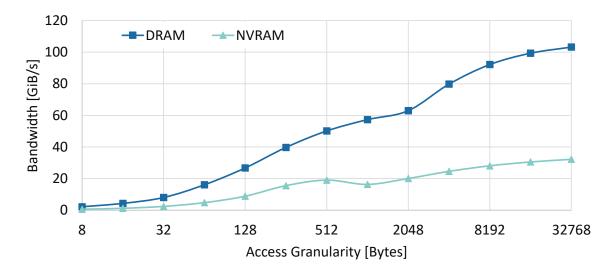

Those effects are further demonstrated in the measurements shown in Figure 2.7. This experiment varies the access granularity for cache line-aligned random accesses (48 threads) on DRAM and NVRAM. The measurements reveal that the effective bandwidth scales up with an increasing access granularity until the cache line size of 64 Bytes is reached. Afterwards, a certain scalability is still given due to the adjacent cache line prefetching until the bandwidth of both DRAM and NVRAM start to converge to their maximal values. Figure 2.8 shows the same experiment for larger access granularities and reveals that hardware prefetchers recognize a sequential access pattern at a 2 KiB access granularity allowing the bandwidth to scale up to its maximum for both memory technologies.

Figure 2.7: DRAM and NVRAM bandwidth for cache line-aligned random memory accesses using access granularities from 8 Bytes to 512 Bytes.

Figure 2.8: DRAM and NVRAM bandwidth for cache line-aligned random memory accesses using access granularities from 8 Bytes to 32 KiB.

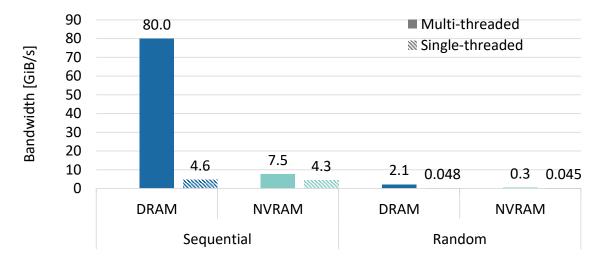

**Local Write Bandwidth.** Figure 2.9 shows the write bandwidth for a sequential and random (8 Bytes) access pattern for DRAM and NVRAM measurements. Similar to the read workload, the peak bandwidth for both memory types is reached using a multi-threaded sequential access pattern (with counts of 48 and 24 threads for DRAM and NVRAM workloads, respectively). While the DRAM write throughput is about 75% of the peak read throughput, this asymmetry mounts up to a 5x lower write bandwidth on NVRAM compared to the read measurements. Interestingly, this asymmetry stays the same for random access patterns on DRAM, but improves from 20% to 42% on NVRAM. Nevertheless, the writing random access workload only reaches 2.5% (DRAM) and 5% (NVRAM) of the sequential writing bandwidth, respectively. With regard to single-threaded performance, only a few percent difference is measured between DRAM and NVRAM.

Figure 2.9: DRAM and NVRAM write bandwidth for a sequential and random (8 Bytes) access pattern. The measurements are given for single-threaded and multi-threaded (best number of threads) executions on the local socket.

Figure 2.10: Shared DRAM and NVRAM read and write bandwidth for a sequential access pattern.

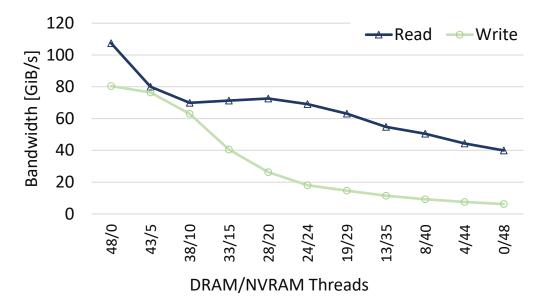

**Concurrent DRAM-NVRAM Access.** To figure out whether the two memory types can be used simultaneously with the same maximum performance, the measurements reflected for the 48-threaded case by Figure 2.10 are performed. This experiment revealed that concurrent accesses to both memories are not able to exceed the maximum reachable bandwidth (independently of the NVRAM thread count) of stand-alone DRAM workloads and actually hurt the performance of both involved components compared to separate results. However, this is expected since both medium types in hybrid platform share the same memory controllers and channels (cf. Figure 2.2).

Figure 2.11: Local and remote read bandwidth for sequential and random (8 Bytes) DRAM and NVRAM accesses. The results show the maximum bandwidth measured by executing multiple threads in parallel.

**Conclusions.** From the read and write bandwidth experiments it could be concluded that NVRAM is 3x (read) to 10x (write) slower compared to DRAM and exhibits a high read-write asymmetry of up to 5x. Moreover, NVRAM is accessed at the granularity of a cache line – or two cache lines with activated adjacent cache line prefetching – similar to DRAM and prefers a sequential access pattern. Interestingly, single-threaded measurements show only a small difference in case of writes. From the concurrent DRAM-NVRAM access experiments it could be inferred that intensive simultaneous usage of both memories is not favored by the shared IMCs.

#### 2.2.2 Socket-remote parameters

As already discussed in Section 2.1.2 – non-uniform memory access is the common case in current scale-up server systems usually consisting of 2, 4, 8, or (in certain cases) even more sockets. The NUMA sockets within such hardware architectures are usually connect via an interconnect network (e.g., Intel Ultra Path Interconnect (UPI) [Int09]) that allows access to remote DRAM and NVRAM and ensures cache coherency. However, accessing remote memory induces certain costs in terms of bandwidth limitation and increased latency, which has already been heavily researched within the context of inmemory database systems [KKS<sup>+</sup>14a, Kim15]. Hence, this section extends the DRAM-NVRAM comparison to NUMA aspects, since UPI performance impacts the data access behavior in case of socket-remote memory allocation.

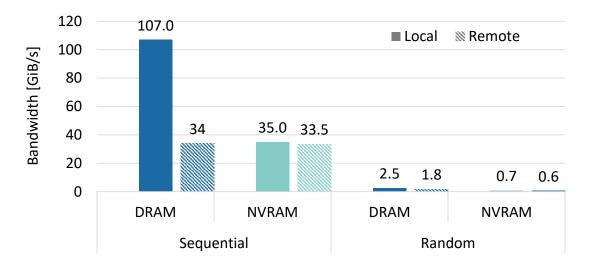

**Remote Bandwidth and Latency.** Figure 2.11 shows the read bandwidth for local and remote memory accesses on the evaluation platform. The measurements are conducted for sequential and random access patterns as well as for DRAM and NVRAM memories. The sequential bandwidth is mainly bound by the UPI interconnect bandwidth of the system. While the sequential remote DRAM accesses face a high throughput penalty, the NVRAM and UPI bandwidth is balanced and almost no throughput loss is experienced here. Moreover, the UPI link is full-duplex such that the full NVRAM bandwidth

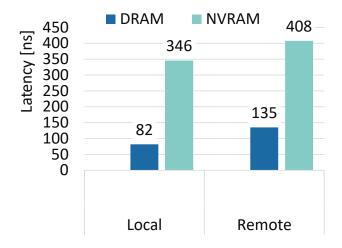

Figure 2.12: Local and remote random read latencies for DRAM and NVRAM. Results are obtained using the Intel Memory Latency Checker.

can be achieved for both sockets accessing remote memory simultaneously. Those results suggest that it makes no difference on which socket data is placed, which is not the case because (i) local memory controllers need to be evenly utilized to achieve the full bandwidth of the system and (ii) occupying the UPI link significantly increases the latency of reading or writing random remote accesses. While sequential remote accesses are bandwidth-bound, random accesses are bound by the latency of the UPI link. The latency overhead is visualized in Figure 2.12 showing the local and remote latencies for accessing DRAM and NVRAM, respectively. The measurements reveal that the relative latency penalty is higher for DRAM (about 60 %) than for NVRAM (about 20 %) as it is reflected in the random memory access bandwidth results.

#### 2.2.3 NVRAM access methods

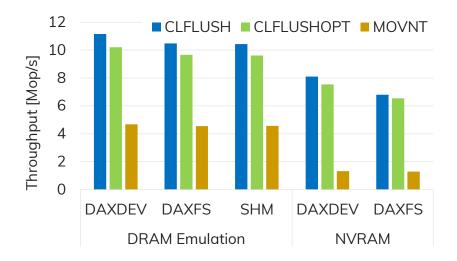

Since there is a number of alternatives in a way how NVRAM can be accessed by the software (cf. Figure 2.4), this part gives an overview of their respective performance. For completeness the DRAM-backed emulation (additionally considering SHM or shared memory access method) of persistent memory is also included. Furthermore, the three major options of persistent flushes are considered (cf. Section 2.1.3). As shown by Figure 2.13, the performance numbers (in terms of throughput) of the access methods do not vary significantly in case of a challenging random column store update workload on DRAM-emulated persistent memory. Here, the column store is represented by a contiguous 1 GiB-sized NVRAM chunk filled with 4 B integers. The real NVRAM hardware features slightly larger throughput gap between DAXFS and DAXDEV. Nevertheless, further in the thesis the DAXFS provider is used as the most flexible and convenient method from the maintenance point of view. The relatively small performance difference between DRAM emulation and real NVRAM of about 24% is explained by the singlethreaded execution of this particular experiment. For that reason the workload is not able to reach the full bandwidth of the NVRAM. Moreover, the executed updates do not depend on each other and thus the DRAM and NVRAM latency respectively, is not the limiting factor here.

Figure 2.13: Column store update throughput w/o replication for different write back options and access methods each for DRAM-emulated NVRAM and Intel Optane DC NVRAM.

**Persistent Flushing.** As shown further in Section 3.1, the cache flushing component can heavily affect the data modification behavior. Therefore, this paragraph also compares performance of write back instructions that are available to user mode applications on the test system (Figure 2.13). As mentioned, the random column store update workload is employed for the experiments on both emulated and real persistent memory. Note that CLWB is not considered since it behaves the same as CLFLUSHOPT on the test platform. As it is observed, CLFLUSH and CLFLUSHOPT performance numbers are close to each other with a slight advantage for CLFLUSH, because it does not require an additional SFENCE. The performance of the *MOVNT* is significantly lower, with considerably larger gap in the case of NVRAM accesses.

### 2.3 VECTORIZED MEMORY ACCESSES IN HYBRID MEMORY SYS-TEMS

The optimized CPU instructions designed to directly operate on byte-addressable memory regions are of a particular interest in the field of hybrid memory systems. This is due to the fact that they determine the respective data processing performance and application capabilities. In particular, the advanced vectorization extensions are addressed by this section.

Since decade, computing performance that can be achieved by increasing the clock frequency of a microprocessor is reaching its physical limits thus making the architectural solutions more promising [PRR15]. In accordance to this trend important data parallelism features of Flynn's taxonomy [Fly72] have been added to commodity CPUs – single instruction multiple data (SIMD) extensions. Essentially, these are sets of instructions that can increase an application performance by allowing the basic processing operation to be executed over multiple data elements (i.e., vector) in parallel. Typical SIMD instruction set provides two extensions to the basic instruction set: (i) vector registers which are larger than traditional scalar registers being currently 32 or 64 bits wide, and (ii) tuned vector instructions working on such registers. The vector here is an instruction operand constituted of a set of data elements grouped into a one-dimensional array, while the elements can be normally integer or floating-point values originally stored on medium (e.g., DRAM or NVRAM). Thus, such data-level parallelism is able to transform a vector of elements within single instruction of the processing unit.

### 2.3.1 Overview of common instructions sets

As already mentioned, in the past years, hardware vendors of common CPU architectures (e.g, x86, ARM) have regularly introduced new SIMD instruction set extensions operating on increasingly wider registers. For instance, Intel's Advanced Vector Extensions (AVX2) operates on 256-bit vector registers and Intel's AVX-512 uses even 512-bit vector registers. Wider vector registers allow processing of more data elements at the same time. For example, an Intel SSE 128-bit vector register can store two 64-bit data elements, an AVX 256-bit vector can store four (2x) and AVX-512 512-bit vector can store eight (4x) of such data elements. Besides wider vector registers, hardware vendors are regularly introducing more complex vector instructions (tuned for specific operations or even application areas) as well.

Recently, Ungethüm et al. [UPD<sup>+</sup>20] introduced a specific SIMD abstraction layer called *Template Vector Library (TVL)* for column-stores to tackle the SIMD diversity in a unified way. On the one hand, the *TVL* offers hardware-oblivious vector primitives. On the other hand, the *TVL* also provides an extensible set of hardware-conscious implementations for the hardware-oblivious primitives. Thus, this approach could be used to realize hardware-oblivious vector primitives which can be easily mapped to specific hardware-conscious implementations.

#### 2.3.2 Deployment in database scenarios

SIMD (also called vectorization) is a state-of-the-art optimization technique in inmemory databases that is most heavily deployed for columnar data organization and typically applied to isolated query operators [AMF06, PRR15, ZR02, DUP<sup>+</sup>20, RAB<sup>+</sup>13, MPM17, LMF<sup>+</sup>16]. Many vectorized implementations for joins [BTAÖ15, BLP11] and sorting [PR14] have been proposed. Moreover, linear access operators such as scans [WPB<sup>+</sup>09] and integer compression techniques [AMF06, LB15] are wellinvestigated. Thus, some query engines are being even fully vectorized [PR20]. Normally, these systems focus on a single SIMD extension (usually AVX-512), i.e., and do not compare efectiveness of alternatives and do not decide at runtime which extension to use.

Since thread-concurrent execution is a natural feature of the hybrid memory system equipped with multi-core computational units – it is important to understand how SIMD vectorized behavoir of database queries is affected by such *multiple instruction multiple data (MIMD)* parallel setting. There is a known issue called *downclocking* [GBB20] that appears in case when large SIMD registers are used by concurrent threads and may lead to the overall performance degradation. To mitigate this problem some works propose separating threads employing AVX-512 and from those executing only scalar instructions by scheduling them on different physical cores to limit the slow-down incurred by AVX-512 on concurrent scalar code. Kumar et al. [KMG14] propose to de-vectorize short vectorized code sections using JIT compilation techniques to avoid the negative impact on scalar code.

From hybrid memory databases point of view SIMD vectorization offers a great opportunity to optimize not only query processing on DRAM-resident data, but also operations involving persistent memory (e.g., replication of primary data) as both mediums are directly exposed to the variety of available CPU instructions as shown in Figure 2.3. Thus, further in the thesis particular attention is given to the opportunities of beneficial SIMD deployment for such purposes.

## 2.4 RELIABILITY IN HYBRID MEMORY SYSTEMS

As already mentioned in the previous sections, the goal of this chapter is to examine NVRAM and respective hybrid memory architectures from database systems point of view. Since the data reliability is one of the key requirements for most data processing applications, this section starts with an overview of failure processing in envisioned hybrid memory database systems (where NVRAM replaces the storage medium). Subsequently, next section gives a survey of reliability techniques that are generally deployed in computing systems, identifies their strengths and weaknesses when used in hybrid memory databases.

#### 2.4.1 Impact on general database failure processing

Traditionally, database management systems classify failures into three main categories depending on where the problem has occurred [GM09]:

- **1. Transaction Failure.** The transaction failure appears when it fails to execute or when it reaches a position from where it can not proceed any further. This class covers also failures of multiple transactions. Generally, the reasons for a transaction failure could be logical (occur if a transaction is not able to complete due to some code error or an internal error condition) or system (occur if the DBMS itself terminates an active transaction because the database system is not able to execute it e.g., because of the transaction abort, deadlock or resource unavailability) errors.

- **2. System Crash.** The system failure may happen due to the power loss or other hardware or software failure (e.g., operating system error) which lead to the loss of volatile content or DBMS state. In such crash scenarios the non-volatile storage and, therefore, accommodated base data are assumed not to be corrupted.

- **3. Medium Failure.** The medium failure occurs when storage devices are not able to provide requested data or return it in inconsistent state. For instance, if the HDD is used as persistent medium this failure may occur due to the formation of bad sectors, disk head crash or any other failure, which destroy all or part of disk storage volume.

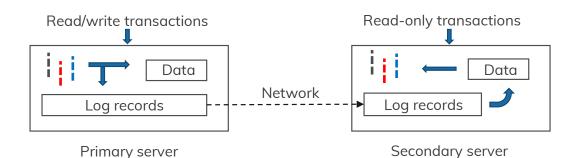

The failures belonging to these three classes could be tolerated using a set of well-known error prevention and correction techniques when running the "early days" DBMS architecture, illustrated by Figure 2.14-(a). Here, logging and recovery manager[GM09] of DBMS are used to handle the transaction failures, OS means and recovery manager address system crashes, while medium failures are mostly handled using hardware level reliability approaches. However, with the advent of previously discussed hybrid memory database architectures (depicted by Figure 2.14-(b)) the failure processing approaches need a refinement due to specific innovative properties of such systems. Namely, such architectures offer a great opportunity to persistently store and to efficiently process huge amounts of data exclusively in byte-addressable memory without touching any slow block-accessible non-volatile medium. Thus, the recovery log and important DBMS state information could be now placed entirely in persistent memory [ZLL<sup>+</sup>15]. Then, the problem of system crashes (e.g., due to the power loss) could be largely mitigated on such systems using consistency-aware persistent programming techniques (cf. Section 2.1.3) and logging data structures [ZLL<sup>+</sup>15]. Since the transactional failures are not affected by the storage medium – traditional solutions still could be employed for hybrid memory architectures to tolerate them as well. Hence, the only failure class that requires further refinement and detailed investigations is the medium failures. As NVRAM devices are byte-addressable and could be physically distributed over several NUMA sockets on targeted platforms – the possible failure scenarios may have unique features (compared to conventional HDD/SSD devices) described in the next section.

Figure 2.14: Evolution of database architectures.

### 2.4.2 NVRAM failure scenarios and consequences for the primary data

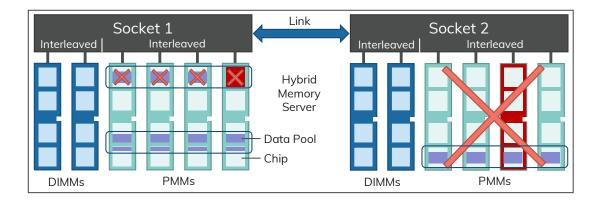

Actively developed hybrid memory database systems are likely to keep the primary data solely persistent in the NVRAM [ALR<sup>+</sup>17]. Therefore, efficient data protection mechanisms need to be considered to prevent data losses and to guarantee high availability in case of PMM failures. Such PMM failures may range from single data cell failures to region, chip, or entire PMM failures and can logically be divided in two classes.

- **Partial PMM Failure.** A partial PMM failure occurs if a soft (temporal) or hard (static) error at cell, region, or chip level happens. In such a case, the remaining PMM is still functional and data in this healthy part of the PMM is able to survive the failure.

- **Full PMM or Socket Failure.** A full PMM failure causes the whole NVRAM of the local socket to become inoperative if channel interleaving is configured as it is common to reach the full bandwidth of the NVRAM. In case of multiple PMMs per channel, portions of the local NVRAM are still usable and the error is covered by the previous failure class. If the entire local NVRAM or even the full CPU/IMC fails, this failure still allows to use data placed on a remote socket on the same machine. That may require migration of the execution threads to the cores of remote socket as well. Then system can still work resiliently, while one of the sockets fails.

Although, at this point in time the statistical data on PMM failures is not yet publicly available, the corresponding studies on DRAM DIMMs reliability [SDB<sup>+</sup>15] and principles of underlying NVRAM technologies [ZLL<sup>+</sup>15] justify the assumption that NVRAM suffers both from analogous to DRAM issues and non-volatile memory specific problems (e.g., due to high temperatures applied to phase-change memory cells).

Figure 2.15: Schematic view of a 2-socket hybrid DRAM-NVRAM system. Exemplary visualization of a chip (Socket 1) and full PMM failure (Socket 2) showing the respective consequences for the DBMS.

Figure 2.15 schematically visualizes a hybrid DRAM-NVRAM platform consisting of two sockets, each running the DRAM DIMMs and PMMs, while channel interleaving mode is used for best performance. Hence, the logical non-volatile memory regions are physically stored in an interleaved way across the local PMMs of a single socket. As discussed above, in case of a *partial* PMM failure, e.g., a chip (shown for socket 1), the data of all horizontally adjacent chips becomes unavailable too and in case of a *full* PMM failure (shown for socket 2), the entire NVRAM of the affected socket becomes unavailable.

## 2.5 SURVEY ON EXISTING TECHNIQUES

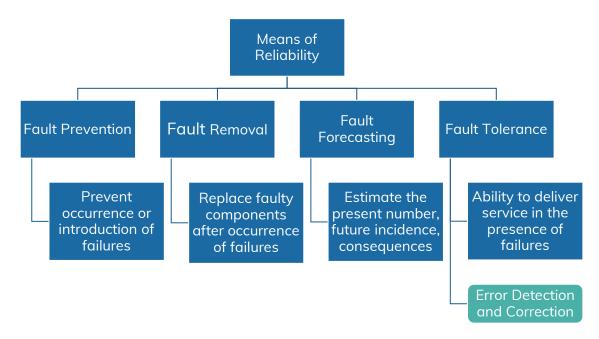

The problems of reliability and high availability in computing systems are wellunderstood and thoroughly studied for a variety of software and hardware architectures. However, the specific properties of hybrid memory systems and discussed above possible NVRAM-induced failure scenarios necessitate a complete rethink of data protection approaches being applied in traditional database architectures. For instance, diskbacked DBMS use block-optimized data replication techniques [Fuj18] that would sacrifice the performance advantage of NVRAM-backed systems. Thus, this section surveys the reliability techniques that are generally used in computing systems and identifies their strengths and weaknesses when used in hybrid memory databases. The related research [ALRL04] suggests the following classification of the reliability means (schematically reflected in Figure 2.16):

**Fault Prevention.** This approach aims to prevent the occurrence or introduction of failures. The fault prevention is a part of general engineering and is mostly used during the development process of both software (e.g., information hiding, modularization, use of strongly-typed programming languages) and hardware (e.g., design rules). The prevention of development faults is a goal for design methodologies and could be designated to hardware manufacturing side when applied in the area of hybrid memory systems. However, the data reliability issues have to be addressed also during the system functioning and data processing. Thus, means of this approach could not be selected to fully provide the data reliability within challenging field of hybrid memory databases.

Figure 2.16: Means of reliability deployed in computing systems.

- **Fault Removal.** This mean not only targets the problems that can appear during the development, but also during the use of a system via corrective or preventive maintenance. The first type of maintenance aims to remove the faulty components that have been detected, while the goal of the preventive maintenance is to remove faults before they might cause errors during the normal operation. Since the interruption of the service delivery even for short time may be unacceptable for many types of databases both techniques are not applicable when addressing NVRAM failures. Precisely, any type of NVRAM failure (introduced in the previous section) would require a complete replacement of the affected memory module that can lead to the significant downtime of the service (e.g., several hours). Moreover, such replacement of the PMM will not recover the corrupted data making the whole approach oblivious to the primary data losses.

- **Fault Forecasting.** The goal of this technique is to estimate the present number, future incidence and likely consequences of failures. The estimation methods could be subdivided into qualitative (e.g., failure mode and effect analysis), quantitative (e.g., Markov chains and stochastic Petri nets [Zar14]) and mixed (e.g., reliability block diagrams and fault-trees). The stochastic nature of NVRAM failures (e.g., due to the device wear-out or cosmic rays influence) makes the precise fault forecasting almost impossible for hybrid memory systems. And, therefore, such forecasting could only be used to recommend the data placement or reshuffling within NVRAM volume but not actually to fully protect the stored data.

- **Fault Tolerance.** Fault tolerance is an ability of a system to deliver service in the presence of failures. Precisely, this technique is aimed at the failure avoidance and normally is carried out via the error detection and system recovery. The error detection component performs internal checks and maintenance during the system operation. Whilst the recovery counterpart is triggered reactively to the revealed failures with the goal to compensate or remove their impact. Thus, the fault tolerance approach is a most promising candidate to ensure the data reliability in highly-performant hybrid memory database systems, as it is expected to deliver strong data protection guaranties in presence of NVRAM failures without significant system downtimes.

Further, this section gives its focus to the *fault tolerance* reliability approach that is based on online error correction and detection. Essentially, its functioning relies on the redundant system components either compute or storage to ensure protection against respective failures. Since NVRAM replaces the storage in hybrid memory systems - the overview in the following is limited to two traditional storage redundancy techniques: *coding* and *replication*. Both are distinguished based on the underlined principles – former normally transforms, reshuffles or extends the protected data, while the latter is supposed to maintain a certain number of full copies of the same data set. The stateof-the-art implementations of these two flavors applicable for hybrid memory database systems are discussed below.

#### 2.5.1 Hardware coding

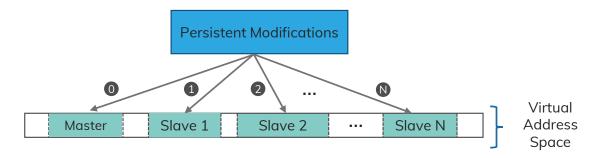

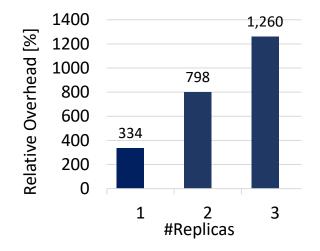

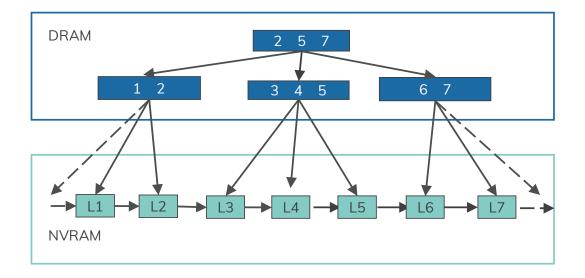

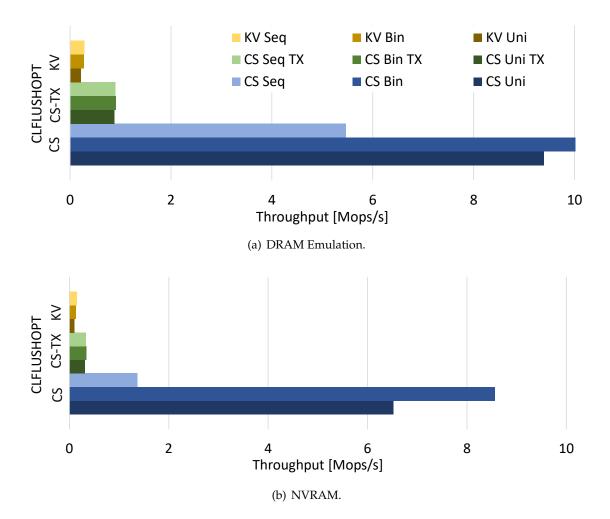

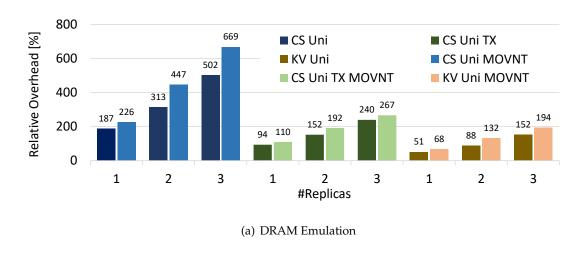

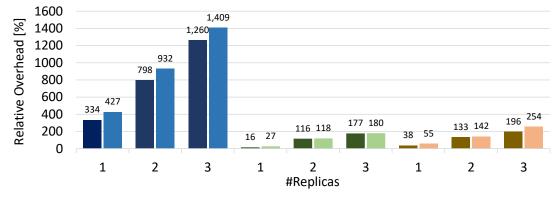

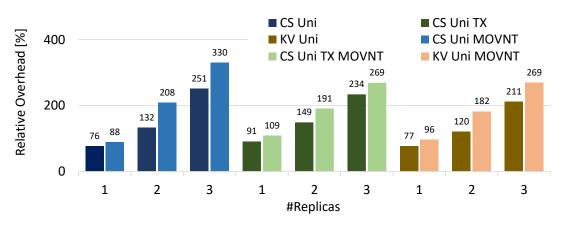

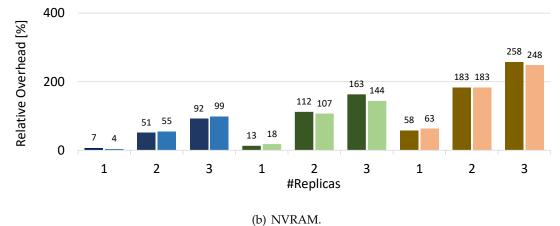

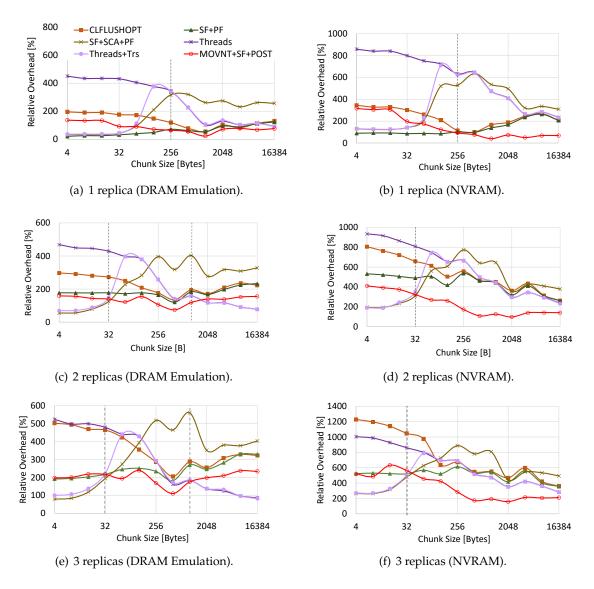

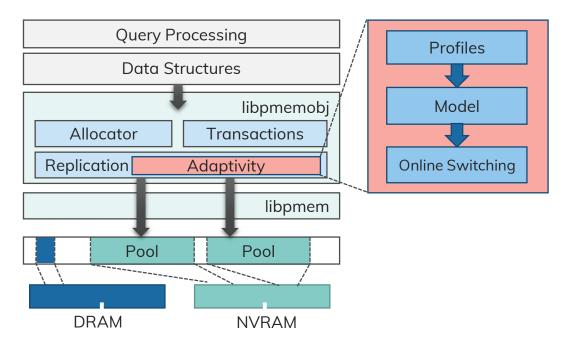

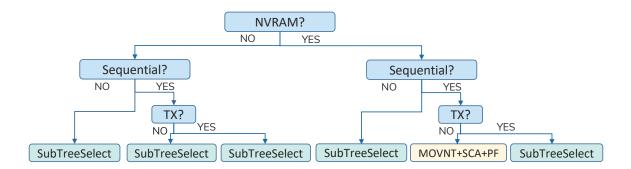

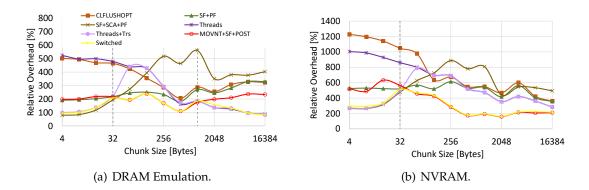

The hardware coding is a reliability mean applied in error correction code memory (ECC memory). This is a kind of volatile digital data storage that deploys an error correction codes (ECC) to detect and correct n-bit data corruption which may occur in the memory [YMC<sup>+</sup>11]. Most of the modern DRAM DIMMs belong to ECC memory class that is capable to detect double error and correct single error (abbreviated as SECDEC) [CLX<sup>+</sup>13]. Thus, such devices are mounted in most machines where the data corruption cannot be tolerated under any circumstances, including critical in-memory databases. However, it is important to concern the respective correction limits regarding the amount of damaged memory cells. As mentioned above, the basic ECC-enabled DRAM DIMMs guarantee the single-bit error tolerance. This means that the data retrieved from each memory word is always the same as data that had been stored, even in case of a single cell corruption (e.g., stuck at 0 or 1 values) or a bit-flip [HKHL18]. There also exists non-ECC memory that uses bit parity checks to support the error detection but not correction, making it necessary to deploy additional reliability mechanisms to actually protect the stored information. Both, the ECC and parity approaches rely on extra memory bits and memory controllers that maintain those bits. Therefore, the redundant bits are used to store the error-correcting code or parity. The parity enables guaranteed detection of all single-cell errors and potentially can discover up to any odd number of bit-flips. While the most frequently used error correcting scheme, the SECDEC Hamming code [CLX<sup>+</sup>13], allows a single-bit error to be corrected and double-bit errors to be detected. To protect the memory modules against more severe failures (e.g., region or chip) some vendors provide uncommon *Chipkill ECC* – typically more reliable approach that is capable of correcting multiple bit errors, including the crash of an entire chip. However, that approach sacrifices one of the chips of the module for redundancy purposes.