# Analytical Query Processing Using Heterogeneous SIMD Instruction Sets

#### **Dissertation**

zur Erlangung des akademischen Grades Doktoringenieur (Dr.-Ing.)

> vorgelegt an der Technischen Universität Dresden Fakultät Informatik

> > eingereicht von

**Dipl.-Medien-Inf. Annett Ungethüm** geboren am 26. September 1985 in Rochlitz

Gutachter: Prof. Dr.-Ing. Wolfgang Lehner

Technische Universität Dresden

Fakultät Informatik

Institut für Systemarchitektur Lehrstuhl für Datenbanken

01062 Dresden

Prof. Dr. Viktor Leis

Friedrich Schiller Universität Jena

Fakultät für Mathematik und Informatik

Institut für Informatik Praktische Informatik

Professur Datenbanken und Informationssysteme

Ernst-Abbe-Platz 2

07743 Jena

Tag der Verteidigung: 05. Oktober 2020

Dresden, im August 2020

## **ABSTRACT**

Numerous applications gather increasing amounts of data, which have to be managed and queried. Different hardware developments help to meet this challenge. The growing capacity of main memory enables database systems to keep all their data in memory. Additionally, the hardware landscape is becoming more diverse. A plethora of homogeneous and heterogeneous co-processors is available, where heterogeneity refers not only to a different computing power, but also to different instruction set architectures. For instance, modern Intel<sup>®</sup> CPUs offer different instruction sets supporting the Single Instruction Multiple Data (SIMD) paradigm, e.g. SSE, AVX, and AVX512.

Database systems have started to exploit SIMD to increase performance. However, this is still a challenging task, because existing algorithms were mainly developed for scalar processing and because there is a huge variety of different instruction sets, which were never standardized and have no unified interface. This requires to completely rewrite the source code for porting a system to another hardware architecture, even if those architectures are not fundamentally different and designed by the same company. Moreover, operations on large registers, which are the core principle of SIMD processing, behave counter-intuitively in several cases. This is especially true for analytical query processing, where different memory access patterns and data dependencies caused by the compression of data, challenge the limits of the SIMD principle. Finally, there are physical constraints to the use of such instructions affecting the CPU frequency scaling, which is further influenced by the use of multiple cores. This is because the supply power of a CPU is limited, such that not all transistors can be powered at the same time. Hence, there is a complex relationship between performance and power, and therefore also between performance and energy consumption.

This thesis addresses the specific challenges, which are introduced by the application of SIMD in general, and the heterogeneity of SIMD ISAs in particular. Hence, the goal of this thesis is to exploit the potential of heterogeneous SIMD ISAs for increasing the performance as well as the energy-efficiency.

# **CONTENTS**

| 1 | INT | RODUCTION                                               | 9                                |

|---|-----|---------------------------------------------------------|----------------------------------|

|   | 1.1 | Motivation                                              | 10                               |

|   | 1.2 | Contributions                                           | 12                               |

|   | 1.3 | Outline                                                 | 13                               |

| 2 | Ov  | ERVIEW AND CHALLENGES OF VECTORIZED QUERY PROCESSING    | 15                               |

|   | 2.1 | In-Memory Column-Store Engines                          | 16                               |

|   | 2.2 | State-of-the-art Vectorization in Column-Stores         | 17<br>18<br>22<br>24<br>26       |

|   | 2.3 | Hardware Trends and Effects on Query Processing         | 27<br>28<br>31<br>33             |

| 3 | TEM | IPLATE VECTOR LIBRARY                                   | 35                               |

|   | 3.1 | Special Instruction Set Integration                     | 36<br>36<br>40<br>49             |

|   | 3.2 | Hardware-Oblivious Vectorization                        | 50<br>50<br>51<br>55<br>58<br>60 |

|   | 3.3 | Related Work                                            | 61                               |

|   | 3.4 | Summary                                                 | 63                               |

| 4 |     | ANCING PERFORMANCE AND ENERGY FOR VECTORIZED QUERY PRO- | 65                               |

| g                | 59<br>70<br>71<br>73<br>77<br>33<br>84<br>89<br>90<br>96<br>96<br>97<br>98 |

|------------------|----------------------------------------------------------------------------|

| Query Processing | 84<br>89<br>90<br>96<br>96                                                 |

|                  | 96<br>97                                                                   |

|                  |                                                                            |

|                  | 99                                                                         |

| 10               | 01                                                                         |

| 10               | )3                                                                         |

| 10               | )4                                                                         |

| 10               | 05<br>06<br>07                                                             |

|                  | 38                                                                         |

|                  | 14                                                                         |

|                  |                                                                            |

| 1                | 16                                                                         |

|                  | 16<br>1 <b>7</b>                                                           |

|                  | 16<br>1 <b>7</b><br>18                                                     |

|                  | 16<br>1 <b>7</b><br>18                                                     |

|                  | 16<br>1 <b>7</b><br>18<br>19                                               |

|                  | 16<br>17<br>18<br>19<br>24<br>27                                           |

|                  | 10                                                                         |

### **AKNOWLEDGMENTS**

When I started working at the chair as a research assistant, it never crossed my mind, that I would stay longer than a year and even write a thesis. However, the encouraging work atmosphere and the unexpectedly wide area of research topics convinced me to take my chance in research. First, I would like to thank Wolfgang Lehner for giving me this opportunity to write a thesis, and for trusting in my ability to finish this, although I have not attended any of his lectures past my elementary studies. Second, I owe my gratitude to Dirk Habich, who helped me not only with his wealth of knowledge, but also found the time to discuss new ideas, and the occasional deadlock some of these ideas were leading to. I would also like to thank Viktor Leis for agreeing to be the external reviewer of this thesis.

Further, I would like to thank all my colleagues for the discussions in the office and in the coffee kitchen, the countless KuKs, for sharing joy and sorrow, and for just being a great team. I especially thank the core MorphStore team, the colleagues from other chairs, who I had the pleasure to work with, and the current and former coffee kitchen regulars (in alphabetical order): Alex K., Bene, Claudio, Johannes L., Juliana, Kai, Lisa, Lucas, Maik, Nils, Martin, Patrick, Sebastian, Tobi, Tomas, and everybody I forgot to mention. From time to time, there are also a few motivated students, who help to test new ideas and breathe new life into side projects, which would otherwise not have been realized: André, Eric, Felicita, Johannes P., and Lennart - I wish you all the best for your own master- and phd-theses.

Finally, I thank my family and friends, who always supported me. Elisa, Anne, Romy, and Alex M. taught me, that friendships can last, even if you cannot see each other for months or even years. My parents always believed in me, and the week-ends at my father's cozy home office thirty years ago were the time when I learned, that research must be fun. Most importantly, I want to thank my husband Stefan, who encouraged me to take this path, spent countless hours to explain the principles of electrical engineering to me, and had my back when times were stressful.

Annett Ungethüm Dresden, October 6, 2020

# INTRODUCTION

- 1.1 Motivation

- 1.2 Contributions

- 1.3 Outline

#### 1.1 **MOTIVATION**

In our increasingly digitalized world, applications and servers have to manage rapidly growing amounts of data. Applications analyzing this data use Online Analytical Processing (OLAP) for this task. They have to process these large amounts of data while maintaining performance and latency constraints. This includes but is not limited to data gathered for and from digital health, digital assistants, e-commerce, smart homes and cities, and industry 4.0. The recent trend for home office and limitations in social life due to the spread of Covid-19 has fueled the use of cloud services<sup>1</sup>, online shops<sup>2</sup>, telehealth<sup>3</sup>, and PCs in general<sup>4</sup> even further. The analysis of this data is retrieved by Online Analytical Processing (OLAP), which typically includes the access and evaluation of only a small selection of attributes.

To satisfy the demand for performance and low latency, hardware development has established a few trends. One of these trends is the growing amount of main memory, which is available at relatively constant prices. This enables applications to keep all of their operational data in main memory, which is faster than accessing data on disk. Another trend is the introduction of Co-Processors. While GPUs have been common for more than 20 years now, other accelerators have only become available and affordable to the general public during the past few years, e.g. dedicated vector processors, FP-GAs, and multi-socket systems. This growing heterogeneity also causes a diversity of instruction sets, because each system offers one or more instruction sets tailored to the hardware. A third development is the increasing density of transistors, which enables multiple cores and different specialized instructions on the same CPU. However, not all of these transistors can be powered at the same time. Hence, only a part of the available chip can be used at a time. This phenomenon is called Dark Silicon [EBA+11]. Thus, it is necessary to use the right transistors, i.e. the right instructions in order to achieve the requested performance.

"Unfortunately, improving performance of applications has now become much more difficult than in the good old days of frequency scaling. This is also affecting databases and data processing applications in general[..]" - Jens Teubner and Louis Woods [Teu17]

At the same time, the importance of energy-efficiency as an optimization goal is increasing [HSMR09]. This has different reasons. The cost of powering large-scale data centers is just one of them. There are also physical constraints like the already mentioned power limits. Another reason is that energy dissipation is released as heat, which requires cooling, which requires even more energy and limits the ongoing miniaturization of circuits. It is not hard to guess that this cycle cannot be upheld endlessly. Hence, energy consumption is not only an optimization goal, but also a limiting factor. There are numerous

<sup>1</sup> https://www.handelsblatt.com/25813516.html, accessed 23/07/2020

<sup>&</sup>lt;sup>2</sup>https://de.statista.com/statistik/daten/studie/579708/umfrage/monatlicheumsatzentwicklung-im-versand-und-internet-einzelhandel/, accessed 24/07/2020 https://www.nytimes.com/interactive/2020/05/13/technology/online-shopping-buying-salescoronavirus.html, accessed 24/07/2020

$<sup>^3</sup>$ https://www.gruenderszene.de/health/coronakrise-telemedizin-durchbruch, accessed 24/07/2020

https://www.hessenschau.de/gesellschaft/wie-die-corona-krise-die-telemedizin-voranbringt, digitale-sprechstunde-100.html, accessed 24/07/2020

<sup>4</sup>https://www.cnbc.com/2020/05/04/pc-sales-usage-rise-during-coronavirus-lockdown.html, accessed 23/07/2020

approaches for energy-efficient data processing, which aim to also keep the performance at an acceptable level, like ERIS [Kis17], E²DBMS [TWZX14], an extension of HyPer for heterogeneous ARM® systems [MRS+14], and even methods to optimize DRAM power consumption [AOA15]. These approaches rely on the setting of hardware knobs, e.g. the CPU or DRAM frequency, and the number and affinity of active threads.

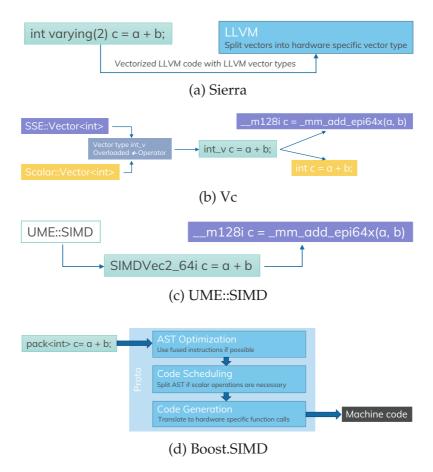

A method, which is promising to boost performance and energy-efficiency likewise, is the use of data-parallelism additionally to the parallelism of instructions. While instructionlevel parallelism is reached by multi-threading, data-level parallelism follows the Single Instruction (stream) Multiple Data (stream) paradigm, abbreviated as SIMD, where multiple data elements are processed with one instruction. Hardware support for SIMD is provided by different instruction sets, e.g. ARM® NEON, ARM® SVE, Intel® SSE, and Intel® AVX512. These instruction sets offer so-called vector registers, which can store multiple elements, and instructions to process the data in these vector registers. Therefore, the use of SIMD is also referred to as vectorized processing. However, a meaningful use of SIMD is not always trivial, especially when there are dependencies between the elements in the same vector register. A prominent example, where this situation occurs is compression. To keep the memory footprint small and to reduce memory I/O, it is common to compress data. This can be done in different ways, e.g. by saving only the differences between values instead of the actual value. Thus, values cannot be treated as independent objects of a vector. Branching, typically realized as masked operations, is another aspect, which is not supported by all instruction sets. Moreover, technically it can break the SIMD paradigm, e.g. if only one bit of the mask is set, such that only a single value is processed. Some of these difficulties have already been identified in the 70s [Fly72] and the growing size of vector registers today increases their significance. In some cases, it might even be more useful to use scalar processing over vectorized processing, which breaks down to the already mentioned choice of the right instructions, i.e. scalar or vectorized. Additionally, there is no standard for SIMD instruction sets. Therefore, different manufacturers develop different instruction sets and different versions of these instruction sets, which do not necessarily show a consistent naming scheme or function range. For instance, the degree to which intra-register dependencies can be processed is different. This degree ranges from not possible, e.g. with SSE, to the detection of conflicts between all vector elements with AVX512. Wherever an instruction set is not offering the appropriate operations, workarounds are necessary, which typically include a scalar processing part affecting the performance negatively. Moreover, different vector register sizes and instruction sets can be present on the same system. Especially Intel<sup>®</sup> CPUs are equipped with different SIMD instruction sets. Hence, these CPUs provide a heterogeneous Instruction Set Architecture (ISA). Previous approaches to provide a unified interface for different instruction sets focus mainly on sequential memory access and element-wise arithmetic computation, e.g. Sierra [L+14], VC [KL12a], boost.SIMD [EFGL14], and UME::SIMD [KM17].

"A number of difficulties can be anticipated for the SIMD organization."

- Michael J. Flynn [Fly72]

However, if used appropriately and with a powerful instruction set, substantial performance gains over scalar execution can be achieved in query processing  $[P^+19b]$ . For this reason, it is worth to analyze and overcome the specific challenges, which are introduced by the application of SIMD in general, and the heterogeneity of SIMD ISAs in particular. The goal of this thesis is to exploit the potential of heterogeneous SIMD ISAs for increasing the performance as well as the energy-efficiency.

#### 1.2 CONTRIBUTIONS

Tweaking the use of different SIMD instruction sets requires a deep understanding of the specific challenges created by large registers and the growing heterogeneity of instruction sets. In this thesis, we provide an insight into these challenges and present according solutions, which are a prerequisite for our optimization approach. The main contributions of this thesis can be summarized as follows:

- 1. We provide a thorough analysis of the challenges created by the introduction of wide vector registers. The growing size of vector registers creates inherent and algorithmic challenges, which must be overcome to be of use for data intensive workloads. Additionally, the diversity of instruction sets on different hardware platforms complicates the port of existing solutions and a fine-grained selection of vector register sizes.

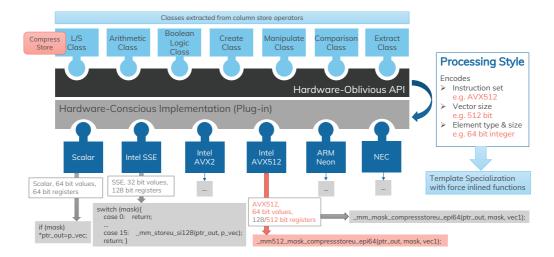

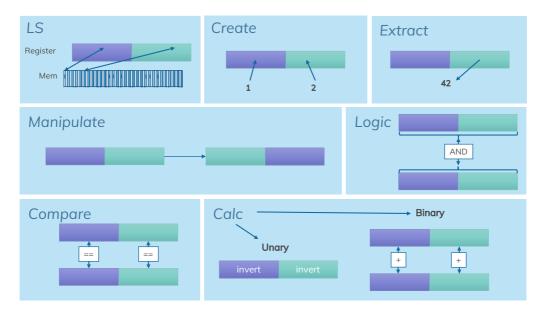

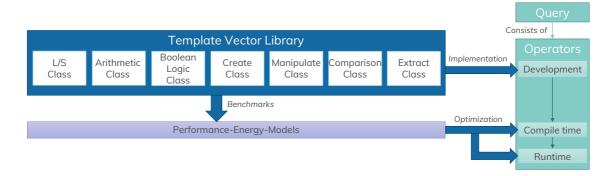

- 2. We present a Template Vector Library, which abstracts from heterogeneous instruction sets while enforcing explicit vectorization. This enables a hardware-oblivious implementation of portable solutions, which tackle the specific challenges of large vector registers. The range of functions, which our library provides, so-called primitives, was chosen to work for memory intensive workloads with different memory access patterns as opposed to existing solutions, which are mainly made for computational workloads, e.g. for scientific simulations.

- 3. Our Template Vector Library enables a fine-grained choice of the register size and the instruction set without changing the underlying source code. This offers the possibility to explore and to use the optimization potential of combining different instruction sets in the same query. We develop a benchmark-based model, which we use for the optimization of performance as well as for the optimization of energyefficiency. We call this model *Work-Energy-Profile*.

- 4. To minimize the number of required benchmarks, we present a method, which combines several primitive Work-Energy-Profiles into profiles for more complex usecases, e.g. for operators.

- 5. We introduce approaches of applying *Work-Energy-Profiles* in different scenarios, e.g. for continuous workloads or for individual queries.

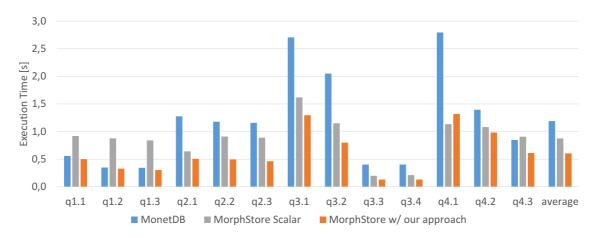

- 6. An end-to-end evaluation using the popular Star Schema Benchmark [OOC07] shows the applicability of our optimization approach for analytical queries. To apply our approach, we use MorphStore [DUP+20], an in-memory query execution engine, which implements all its operators and compression algorithms using our template vector library. We also compare our results to MonetDB [IGN+12], a stateof-the-art column-store.

Additionally to our main contributions, we provide an overview of related work for each individual topic and a discussion of selected results. Most of our contributions have already been published in international conferences and large parts of the source code are available online, which we will reference in the appropriate sections of this thesis. Although our approach is software-based, we also give a short insight into the hardwarebased approaches for performance and energy-efficiency optimization using instruction set extensions. As we will show, hardware design does not have to be a one-sided process, but in a collaborative environment, software requirements can serve input for the development of hardware, which fits the applications they are made for.

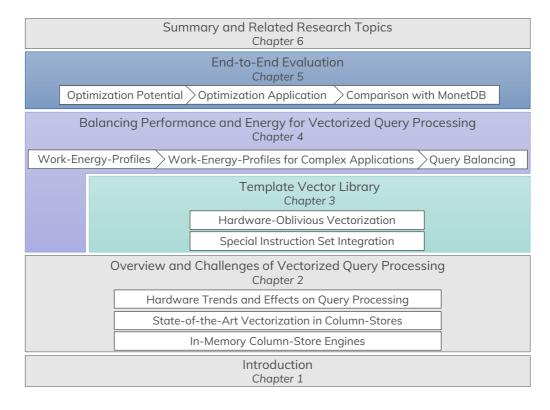

Figure 1.1: Overview of the structure of this thesis

#### 1.3 OUTLINE

Figure 1.1 provides an overview of the topics of this thesis, which roughly reflects our main contributions. In Chapter 2, we recapitulate the state-of-the-art in column-store engines and their application of vectorization. We also discuss the effects of vectorization on query performance and its physical constraints, which come with instruction set extensions. Chapter 3 shows why the integration of vector instruction sets into query execution engines is not trivial. There are reasons following directly from the size of the vector registers, and there are reasons following from the fact that many existing algorithms were designed for scalar processing. Moreover, the variety of instruction sets between different hardware systems requires different implementations, which can vary heavily in their complexity and performance. Therefore, we present a Template Vector Library, which enables hardware-oblivious explicit vectorization. In Chapter 4, we present our Work-Energy-Profiles as a model used to optimize for performance and for energyefficiency. By using our library, different instruction sets integrate seamlessly into this approach. We also provide a benchmark concept to create such Work-Energy-Profiles and a method to create Work-Energy-Profiles for use-cases which were not individually benchmarked. Then, we apply our optimization approach to complex analytical queries in Chapter 5. Finally, we provide a summary in Chapter 6. Additionally, we show how our optimization goals are tackled from the hardware side and which potential future research topics arise from our work.

# OVERVIEW AND CHALLENGES OF VECTORIZED QUERY PROCESSING

- 2.1 In-Memory Column-Store Engines

- **2.2** State-of-the-art Vectorization in Column-Stores

- 2.3 Hardware Trends and Effects on Query Processing

The state-of-the-art in analytical query processing are in-memory column-store engines [Pla09]. In this chapter, we will give an outline of the characteristics of such systems in Section 2.1 and present two widely adopted optimizations: vectorization and compression in Section 2.2. These optimizations are often used in a combination, i.e. vectorization is used to enhance the compression speed ([D+19, L+15, SGL10]), which improves the overall performance. However, the use of vectorization in an ever-changing hardware landscape presents the query execution engine with some challenges, which we will discuss in section 2.3.

#### 2.1 IN-MEMORY COLUMN-STORE ENGINES

Efficient analytical query processing heavily relies on fast data access. In the memory hierarchy, disk access has a higher latency and lower bandwidth than the volatile memory in the lower layers. For this reason, it makes sense to keep data in other layers of the memory hierarchy, e.g. in main memory. The increasing density of main memory at relatively low prices allows for the development of in-memory database systems, which reduce the use of disk to a minimum or completely eliminate it, e.g. HyPer [KN11] or MonetDB [ $IGN^+12$ ].

Further, analytical queries are characterized by the access of few columns but many rows, e.g. a simple scan reads all rows of a column. Thus, memory access is not only optimized by moving the data into main memory, but also by reorganizing it in a so-called columnstore. This means, that data is partitioned vertically, such that columns are stored sequentially, where each element has an ID identifying the tuple it belongs to. To reconstruct a tuple, a projection on the other columns is done with this ID. A project operator reads the IDs of a result set and gathers the values of another column, which share the same ID. For an efficient memory access and evaluation, values and IDs are typically represented by a numerical data type with a fixed size, i.e. as integer data types. In MonetDB such a collection of (ID, value)-tuples is called Binary Association Table (BAT), where the valuepart is a memory mapped simple array. A column-store enables linear memory access during scans and aggregations of columns, because only the column, which is evaluated has to be read. There are no other attributes of the tuple, which have to be skipped or read without being used. This increases the performance compared to the random access required for accessing selected columns in horizontally fragmented relations. A further optimization is to omit the ID and just use the position in an array instead. This is done in the read-optimized store of the system C-Store, which shows significant speed-ups compared to row-stores, which use horizontal fragmentation [SAB+18]. Later, the idea was also adopted by MonetDB, such that only a base value per column is stored now and the other IDs can be reconstructed from this base value<sup>1</sup>.

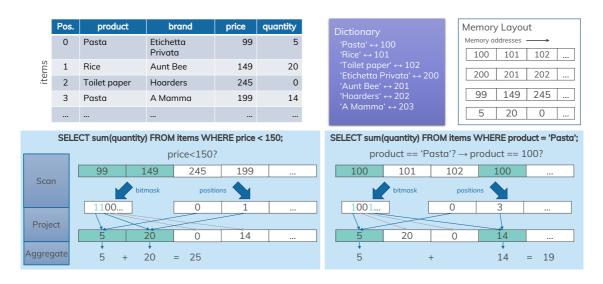

The execution engine of such column-stores requires special operators working on columnar data instead of the traditional rows, e.g. [BMK+99, BHC12]. Figure 2.1(a) illustrates this using a simple warehouse example query. This query assumes a relation items with at least 2 attributes product and price. The requested result is the number of stocked items, which cost less than 150 cents. The data is stored column-wise. To evaluate the example query, at first a scan on the *price* column is executed. Each value is read and checked for the condition less than 150. The result of this check can be represented in two different ways. One way is a bitmask, where each set bit indicates that the corresponding element satisfies the condition. The second way is to store the position of the matching elements in an intermediate column. Both ways can be used to do a projection on the *quantity* column in the second step. With the bitmask, each bit of the mask is read.

https://www.monetdb.org/blog/monetdb-goes-headless,accessed 08/04/2020

Figure 2.1: A relation (items) and examples illustrating the query execution on data in columnar layout. (a) A query reading columns with integer data. (b) Data is dictionary encoded before being processed.

If the current bit is set, the position of this bit is the position of a result element in the quantity column. The values at these positions are then written sequentially into an intermediate column. All values of this intermediate column are then summed up by the aggregation operator. In this scenario, the columnar layout enables a maximum of linear memory access. The scan in the first step reads the price column sequentially and writes the intermediate result sequentially, i.e. the bitmask or the positions. The projection in the second step sequentially reads the intermediate result. Only the *quantity* column is accessed randomly during the projection to gather its values. The result of the projection is again stored in an intermediate column, which resides sequentially in memory. Finally, the aggregation reads this second intermediate result sequentially. Some systems fuse operators whenever possible, e.g. they do the projection and the aggregation in one step without writing an intermediate result, but the sequential memory access is preserved. Such in-memory column-stores have become the most common approach for analytical query processing because they perform better on modern CPUs than the traditional row-store [Pla09]. Additionally, they are perfectly suited for further optimizations like vectorization or compression, which we will discuss in the following sections.

#### 2.2 STATE-OF-THE-ART VECTORIZATION IN COLUMN-STORES

Vectorization allows to process a number of values with a single instruction and in a single register, the so-called vector register. Hence, vectorization is also called SIMD (single instruction multiple data). Recent CPUs are equipped with instruction sets for vectorized processing. A SIMD instruction set offers two extensions to the basic instruction set: (1) Vector registers, which are larger than the traditional scalar register, and (2) Special instructions working on the vector registers, usually wrapped by a handy library for a higher level programming language, e.g. for C/C++. From server-grade Intel CPUs (SSE, AVX, AVX512) to mobile devices (e.g. NEON on Arm CPUs), vectorization is ubiquitously available. Hence, SIMD is also naturally applied in query processing. For more than a decade, using SIMD has been state-of-the-art when it comes to optimizing columnstore query engines. In this context, vectorization is a tool for single-query optimization, and the design of the operators is a key aspect to reach this goal.

Column-stores provide their column data as a sequence of values with the same data type, which enables fast sequential access by the operators. By vectorizing operators, data parallelism is added, which can speed up query performance. Moreover, sequential data access can be vectorized trivially from a programmer's perspective, because loading a vector register from sequential data in memory is a basic functionality found in all SIMD instruction sets. The memory access is then still linear or strided, i.e. the memory address, from which the data is read, moves only forward and in well-defined steps. However, for an efficient evaluation in vector registers, all values need to have a fixed size. For this reason, data with a variable length, e.g. strings, are dictionary encoded. This means that each value is encoded with an integer. These integers are then used during query processing instead of the actual values. The mapping between the values and integers is stored in a separate dictionary. For example, the product and brand columns of the warehouse example from Section 2.1 are not given with IDs but with names, which are strings. Figure 2.1(b) shows a dictionary, which maps each value of the product and brand columns to an integer. These integer values are stored sequentially as shown in the Figure. A query can now be evaluated on integers instead of strings. This is shown with an example, which queries the amount of stocked pasta. The scan on the *product* column in the first step does only integer comparisons and stores the intermediate result. Although the dictionary can be used to reconstruct the original values, this is not necessary in this query.

Finally, operators and compression do not make a working system. A processing technique is required to actually evaluate queries with vectorized operators on compressed data. In the following, we will explain the mentioned aspects in more detail.

#### 2.2.1 Vectorized Operators

Since in-memory column-store engines assume that all of their data resides in main memory, fast memory access is the key to performance optimization. From this perspective, physical operators can roughly be categorized into two groups: (1) Operators with sequential memory access, e.g. scan, and (2) Operators with random memory access, e.g. lookup.

#### **Linear Memory Access**

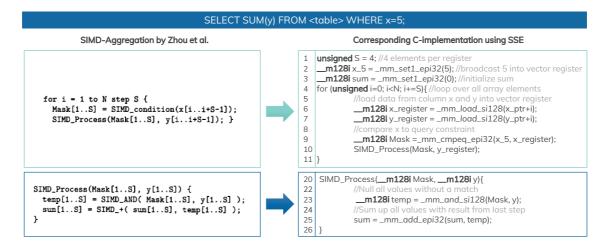

For column stores, this first group can often be vectorized with a very basic SIMD instruction set, which offers only generic load and store functions. Hence, first approaches for vectorized operators using only linear memory access have already been proposed almost two decades ago. For instance, in 2002, Zhou et al. present SIMD algorithms for scans, aggregations, nested loop joins, and for building selected index structures [ZR02]. These operators require the data to be stored column-wise, such that multiple values of a column can be loaded into a vector register with one instruction and then be evaluated with another instruction. An example operator proposed in [ZR02] is shown in Figure 2.2 on the left side. Since the SSE instruction set with 128 bit registers on 32-bit systems was common when the work was proposed, we decided to show a corresponding example implementation using SSE and 32-bit data types on the right side of the figure. The example sums up all values in a column y, where column x equals 5. For simplicity, this implementation hard-codes the element count of the vector register (S in line 1) and the constant 5 ( $x_5$  in line 2). The columns are given as raw data pointers  $x_ptr$  and  $y_ptr$ . The first part, i.e. the for-loop, is used in all operators, which are linearly reading data.

Figure 2.2: A SIMD aggregation as proposed by Zhou et al. [ZR02] and a corresponding implementation for C/C++ using the Intel SSE instruction set. Note that the final aggregation of the four elements in the *sum* register are not pictured.

In this loop, the function SIMD\_condition checks whether a condition is met by the elements of a vector and returns the result as a bitmask. In our example, this is a check for equality with the number 5. The second part, i.e. the function SIMD\_Process, is specific to the aggregation-operator. Note that the authors use a 1-based index, while our implementation uses a 0-based index. Apart from this difference, we exchanged the generic functions and data types with the according SSE intrinsics and types, and added some initializations and explicit vector load operations. All in all, the translation into a real programming language is straight forward. After some initializations in line 1-3, the for-loop starts. In this loop, two vector registers are loaded from linear data in the two columns x and y (line 6-7). The comparison for equality with 5 is done in line 9. The result is another vector Mask, which stores either 32 set bits for a match or 32 unset bits if there was no match for each vector element. This result and the register loaded in line 7 are the parameters for the function SIMD\_Process (line 10). Finally, SIMD\_Process (line 20-26) performs the actual aggregation. At first all elements without a match are nulled using *Mask* and a logical AND (line 23). Then, the values are added to the values of the preceding iteration (line 25). The final aggregation of the elements in the resulting register after the last iteration is done linearly, introduces a minor overhead, and is not shown in the code.

#### **Random Memory Access**

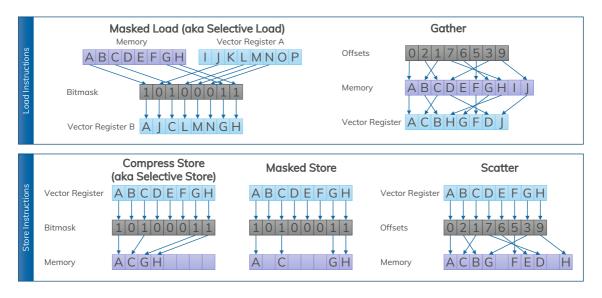

The operators from the second group require at least one of the following vector instructions: gather, scatter, masked load, masked store, or compress store. Figure 2.3 illustrates these instructions. A gather loads a vector register with values from various memory addresses. A scatter operation is the store equivalent of the gather. It stores values from a vector register to various, non-linear, memory addresses. A selective load, also called a masked load, uses a bitmask to load only selected values from memory into a register (B). The elements at positions, which are not loaded, are either zeroed or filled from another vector register (A). The masked store works the other way round. The bitmask is not used for loading, but for storing selected elements from a vector register into memory. The existing values at addresses, which are not written, do not change, i.e. they are not

Figure 2.3: Different instructions for random memory access. Often, this also involves selective vector lane access.

zeroed. In contrast to this, a compress store does store all selected values linearly into memory without any gaps for the not selected elements. If the compress store is called in a loop, the new memory address has to be computed after each iteration, i.e. the new address is only known at runtime. For this reason, memory access cannot be scheduled as efficiently as with a common store instruction, where the address offset equals a whole vector width in every iteration. In literature, the compress store is also called selective store. However, it is not the store equivalent for a selective load. For a clear distinction of the instructions, we will call it compress store in the remainder of this thesis. There is no dedicated compress load, because it is just a special case of the gather instruction, but there are combinations of the presented instructions, e.g. masked gather. If these instructions are not supported by the CPU, data has to be moved before it can be loaded into vector registers, which is another expensive operation. Hence, operators requiring random memory access have only been vectorized, when newer instruction sets, e.g. AVX2 on intel CPUs, were widely available.

Polychroniou et al. present a collection of vectorized operators, which use these instructions [P+15]. Their work includes not only the building of index structures, but also using them, e.g. the build and probe phase of Cuckoo hashing. This can then be used to realize more sophisticated physical operators, e.g. hash joins. However, this is only beneficial for the performance, because the required random memory access instructions are natively supported by the CPU used by the authors.

Despite this hardware support for random memory access, the best performance is still shown when linear memory access is used. In some cases, the advantages of linear access outweighs the cost of moving data to enable this access, especially if the data is read multiple times. Schlegel et al. exemplarily show the impact of linear memory access compared to random memory access for a vectorized k-ary search [SGL09]. In one scenario, they calculate the addresses of the separators in each step. Hence, the separators are not loaded from sequential addresses. In the other scenario, the separators are written linearly to a dedicated memory region before executing the search. Compared to a linear binary search, the k-ary search with random memory access reached a speed-up of up to 1.8, while with linear memory access, it reached a speed-up of up to 2.5 on an Intel i7 CPU.

Figure 2.4: The vectorized linear probing as proposed in [P+15] introduces the highlighted random memory access instructions.

Kim et al. [KKL<sup>+</sup>09] consider a sort-merge join to exploit data-parallelism and to avoid random memory access as far as possible. They report a comparable performance with a hash join when using 256-bit registers and a higher performance when using 512-bit registers. Unlike a hash join, a sort-merge join using a bitonic sort avoids gather and scatter instructions by using linear load and store instructions as well as shuffle instructions.

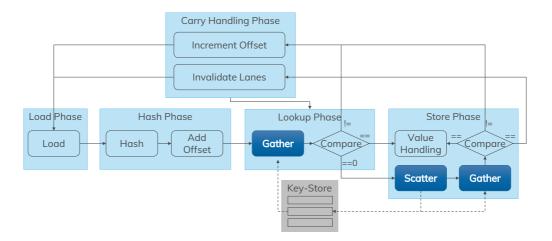

The case of random memory access in hash joins, specifically during linear probing, has been investigated in [P+19a]. Generally, linear probing is a way to find an empty slot in a hash table to insert a key, when a hash collision occurs, i.e. when a hash function maps two different keys to the same bucket. In these cases, the next best free slot is used to insert a new bucket with the second key. Vectorizing this approach introduces the challenge to find such collisions between the keys or hash values, which are loaded into the same register. Figure 2.4 shows the control flow of the vectorized linear probing as proposed in [P+15]. In the load phase, keys are loaded into a register. In the hash phase, a bucket is computed for each key and an offset is added, which is initially zero. The lookup phase loads the keys currently stored in the computed buckets and compares them to the keys loaded in the register. If a bucket is empty (==0), the corresponding keys in the register are stored with a scatter operation in the store phase. However, to avoid storing potential equal hash values, which might exist in the same register, to the same bucket, another gather operation is used to load the active keys again and compare them. If the comparison is successful, the lanes (bits holding a vector element) of these keys in the register are invalidated in the carry handling phase. For all keys, where the comparison is not successful, the lanes are not invalidated, and they are not stored. If the keys are equal, there is nothing to be stored and the vector lane containing the key is also invalidated. If the bucket is not empty but the keys are not equal, a new bucket has to be found. In this case, the lane is not invalidated and the key cannot be stored in the current iteration. All invalidated lanes can be reloaded with new keys in the next iteration, while all other lanes stay in the vector register and an offset is added for the next hash phase. Thus, there are several random memory access instructions in vectorized linear probing. Specifically, the lookup phase contains a gather, and the store phase even contains a scatter and a gather.

#### 2.2.2 Lightweight Integer Compression

The use of vectorization in operators introduces data parallelism, which increases the performance. This performance can even further be increased, when more elements fit into one vector register. This cannot only be achieved by wider vector registers, but also by smaller data elements. For instance, if only 16 or 8 bit are used per value instead of 32, a 128 bit register can fit not only 4, but 8 resp. 16 values. Hence, the data parallelism is increased because more values can be loaded and evaluated at once. Moreover, bandwidth is saved if the data required for query evaluation is smaller. To reach this goal, compression is used. Consequently, compression itself is also vectorized to enable the compression of multiple values at once [SGL10, L+15]. Since a user is usually interested in correct results, lossless compression is used in database systems, e.g. the aggregated payroll costs of a company should be calculated exactly instead of approximately, not only for the tax declaration. A challenge for compression in in-memory database systems is that the bandwidth savings must outweigh the costs of compression and decompression. This is a major difference to the compression used for archives on disks or on tape, where the compression rate is the most important optimization goal. That is why in-memory database systems typically use lightweight compression as opposed to heavyweight compression. In lightweight compression, the compression and decompression performance is higher than in heavyweight compression, potentially on the cost of the compression rate.

#### Abstraction Levels

As described in [D<sup>+</sup>19], there are different lightweight compression techniques, algorithms, and implementations, which address different levels of abstraction.

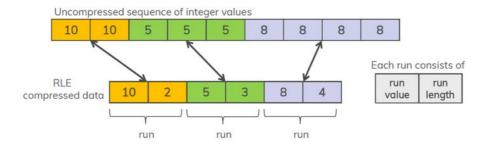

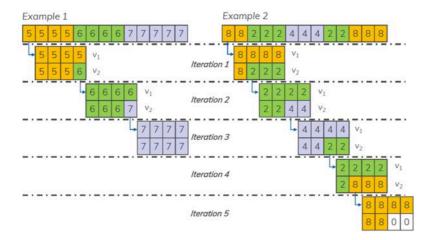

**Techniques** describe the basic idea for a compression. Techniques can work on two different levels: The physical level or the logical level. On the physical level, the number of used bits per value is reduced, while the logical level reduces the number of values. The physical level compression technique works on either bit-, byte-, or word-granularity and reduces the number of existing but unused bits. This is why it is called Null Suppression (NS). On the logical level, there are different techniques. The already mentioned Dictionary Encoding (DICT) encodes values as integers. While not necessarily reducing the required space, it can be used to encode strings or random data types as integers, which can then be further compressed with a different technique. Frame-of-Reference (FOR), Delta Coding (DELTA), and Run-Length-Encoding (RLE) work on integers. FOR encodes values as the difference to a given reference value, while DELTA stores the difference to a predecessor. FOR or DELTA can cause a later Null Suppression to reach a higher compression ratio. RLE detects sequences of the same value and stores this value only once, together with the length of the sequence.

**Algorithms** are concrete descriptions of the binary data layout of one or more techniques. Thus, an algorithm explains how to realize a technique or a cascade of techniques. For example, there are NS-algorithms, which try to store as many values as possible within one processor word, while others try to store each value with a minimum number of bits or bytes [ZZL+15]. These three groups are referred to as bit-, byte-, or word-aligned. A fourth group of NS-algorithms clusters sequences of integers with the same bitwidth into frames. These frame-aligned codes can be regarded as a special case of bit-aligned codes. An example for an algorithm using a cascade of techniques is PFOR,

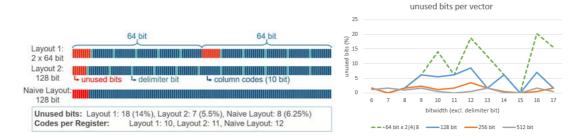

Figure 2.5: Different layouts for storing codes into vector registers and the number of unused bits depending on the register size and the code size

which combines FOR with a bit-aligned NS algorithm. PDICT works similarly but with Dictionary Encoding instead of FOR. PFOR-DELTA additionally does DELTA Coding before applying PFOR [ZHNB06]. As already mentioned, if data is not already present in an integer format, DICT must even be applied before being able to use any other algorithm, which also results in a cascade of techniques. While a compression technique only describes an abstract idea, compression algorithms describe concrete data layouts, which can be optimized for vectorized processing. For instance, Bitpacking (BP) is a bit-aligned NS compression algorithm, which exists in different variants, e.g. SIMD-BP128 is optimized for 128-bit wide vector registers. SIMD-FastPFOR is a vector-optimized variant of an advanced PFOR algorithm [L+15]. There are also vectorized algorithms for DELTA, FOR, and RLE  $[D^+19]$ .

**Implementations** are the hardware-specific code of algorithms. This code can differ depending on the instruction set offered by the CPU, especially when vectorization is used.

This shows, that there is a huge variety in lightweight compression. There are various algorithms for each compression technique and each algorithm can be realized by different hardware-specific implementations. Moreover, there is no algorithm, which shows the best performance for every use-case [D<sup>+</sup>19]. Nevertheless, specialized operators, which can directly work on compressed data, can increase the query performance, even if the chosen algorithm is not the most optimal one, because a higher degree of data parallelism is possible.

#### **Specialized Operators**

Especially for data, which has been null suppressed, there is a huge variety of operators, mostly scans, e.g. [WPB+09, LP13, FLKX15]. These operators can be vectorized to gain more performance. They either decompress data in-register or not at all.

An example for a vectorized scan, which does an in-register decompression, is SIMD-Scan by Willhalm et al. [WPB+09]. SIMD-Scan directly loads a sequence of bit-aligned codes into a vector register  $(R_1)$ . A subset of these codes is then copied into a second register  $(R_2)$ , which is used for the next steps. Then, the codes in  $R_2$  are shifted within the register, such that a code starts at the least significant bit of each vector lane, i.e. at the beginning of each vector element. This allows predicate handling using instructions, which evaluate vector registers on element granularity. The result can be transformed into a bit vector and written to memory. After writing back the result, the next subset of codes is copied from  $R_1$  into  $R_2$  and the steps are repeated until there are no more elements left in  $R_1$ , which have not been evaluated.

BitWeaving [LP13] works without decompression and was originally designed for scalar processor words, but a variant of BitWeaving, the so-called Vertical BitWeaving, can be vectorized in a straight-forward way. Like SIMD-Scan, BitWeaving works on null suppressed bit-aligned codes. The vertical variant expects the codes to be stored in a vertical layout, i.e. a code is spread over multiple processor words. For example, assuming 64-bit processor words, the first bit of the first 64 codes are stored sequentially in one processor word. The second bit of the first 64 words is stored in the second processor word and so on. Hence, there are as many processor words needed as there are bits per code. The predicate is stored in the same way, i.e. a processor word is always filled with the corresponding bit of the predicate. Each of the processor words containing the codes is then bitwise compared to the corresponding processor word containing the predicate. The results after each step are combined bit-wise using a logical AND. In the end, the result is a bitmask indicating which of the 64 elements matched the predicate. This way, the codes do not even have to be decompressed in register. Furthermore, the larger the processor word, the more codes can be scanned at once. For this reason, the vectorization of Vertical BitWeaving is straight forward and shows a significant performance gain over the scalar implementation [LUH+18b]. There is also a vectorized variant of horizontal BitWeaving, where codes are aligned to be loaded sequentially into a vector register with a separating delimiter bit. This delimiter bit contains the result after the predicate evaluation. However, this does not only introduce additional computation overhead but also wastes some space in the vector register depending on the code size. Figure 2.5 exemplarily shows two different layouts for storing codes horizontally into a vector register. It illustrates how to store 10-bit codes into a 128-bit register. Layout 1 allows working within word boundaries. This is important because horizontal BitWeaving requires an arithmetic addition, which does not exist for whole vector registers. Layout 2 uses the register width more efficiently. For comparison, a naive layout without any delimiter bits is also shown. Next to the layouts, the number of unused bits is shown for different vector sizes.

#### 2.2.3 **Processing Techniques**

Operators and an option for compression alone do not make a query engine. To run vectorized queries, a processing technique is required. Generally, there are three different ways to process a query: (1) tuple-at-a-time, (2) operator-at-a-time, and (3) vector- or blockat-a-time. Tuple-at-a-time processing is also known as the Volcano iterator model [Gra94]. In this technique, a *next()*-function is implemented by each operator, which returns the next tuple. A query plan is realized as a tree and each node of this tree calls the next()function of its children until no tuples are returned anymore. This allows to fuse several operators into one loop, which computes individual tuples, effectively eliminating the need for materialization of the intermediate results. As much as the fusion of operators decreases unnecessary memory access, as much optimization potential does it take away in other aspects. For instance, capabilities of modern CPUs, e.g. useful prefetching, are heavily impeded by operator fusion as shown in  $[M^+17]$ . For this reason, the authors argue for a relaxed operator fusion, where execution pipelines are split in more places than only pipeline-breakers. They could show that this has a beneficial effect on query performance, even though there is an additional cost for writing and reading the materialized intermediates.

The opposite of tuple-at-a-time is operator-at-a-time. With the operator-at-a-time technique, no operators are fused. Instead, each operator processes a whole column producing an intermediate result, which is the input for the next operator. This eliminates the issues mentioned in  $[M^+17]$  most widely on the cost of additional main memory access.

A system using this technique is MonetDB [IGN+12], which adopts the column-store concept of C-Store. However, compression of the intermediates reduces memory access and therefore helps to compensate for this disadvantage. This allows for the combination of the advantages of both worlds. Moreover, when using SIMD, values from more than one tuple are processed. For this reason, *tuple-at-a-time* processing is not applicable when using SIMD, while operator-at-a-time is.

Vertica is another column-store system, which is a direct successor of C-Store [LFV<sup>+</sup>12]. One of the improvements over the original C-Store is the heavy and varied use of lightweight compression. Delta compression and Run Length Encoding can be used to minimize the memory footprint. Additionally, Vertica offers a variant of Dictionary Encoding. This is a necessary condition for all engines to make use of SIMD, because the overwhelming majority of SIMD instructions process only numeric values. For being able to process string values, they have to be encoded as numeric values first, which is done by Dictionary Encoding.

Apart from compression, an optimization of operator-at-a-time is to process only parts of a column at once, so-called blocks or vectors, where vector denotes to any number of values between the actual vector register size and the whole column. This is called vector- or block-at-a-time. The idea is to write smaller intermediate results, such that they fit into the cache. If these intermediates even fit into the registers, operators can still be fused.

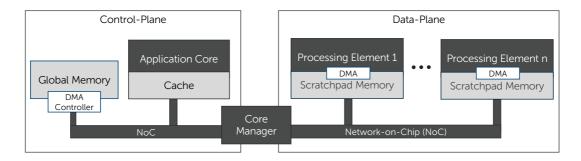

A system using the vector-at-a-time model is MonetDB/X100, which uses MonetDB as a base and is able to run vectorized queries on a Cell Engine [HNZB07]. A few adjustments were necessary to reach this. First, the operators were rewritten. Some have been adjusted to be better suited for auto-vectorizers, e.g. a bitmask is used instead of an offset vector to scan previously selected elements. Other operators, e.g. the grouped aggregation, are explicitly vectorized using the intrinsics provided for the cell architecture. Second, the *next*()-interface has been changed to return a collection of vectors instead of individual tuples. Finally, the algebra interpreter still runs on a traditional CPU core, called PPE (Power Processor Element) on the Cell engine. This PPE triggers the actual execution on the SPEs (Synergistic Processing Element), which contain vector registers and the means to process them. Unfortunately, this solution is not applicable anymore, because the Cell Engine is outdated and not produced anymore. However, the idea of processing columnar data in vectors was kept and turned into a commercial product called Actian Vector<sup>2</sup>, formerly Vectorwise[ZB12].

There are also approaches targeting more recent hardware, e.g. VIP, which uses the most recent SIMD instruction set by Intel, AVX512 [P+19b]. VIP does not build on an existing system, but implements a bottom-up approach. Explicitly vectorized and precompiled suboperators are used to build full operators, where suboperators, e.g. hash probing, can be used in multiple operators. Query execution works by suboperators processing blocks of tuples from one column and keeping the intermediates in cache wherever possible. A compression algorithm is also supported and realized by combining suboperators. VIP supports dictionary coding with subsequent bitpacking. The use of a recent instruction set and the according large registers (512 bit) combined with the avoidance of compilation during runtime, leads to competitive performance.

In this work, we focus on the opportunities of vectorization, not on those of optimized processing techniques. Therefore, we use the plain operator-at-a-time technique without

<sup>&</sup>lt;sup>2</sup>https://homepages.cwi.nl/~boncz/, accessed: 20/07/2020

fundamental changes such as *block-at-a-time* processing. Nevertheless, all the concepts we will present are also suited for an application in a *block-at-a-time* processing environment.

All mentioned processing techniques can profit from minimizing the overhead of reading and writing intermediates. There are two methods to reach this goal: (1) Avoid intermediates completely, i.e. fuse the operators of a query, and (2) Compress the intermediate results.

As already explained, the first option can easily be applied in tuple-at-a-time processing, although there are the mentioned drawbacks to this approach. However, HyPer processes vectors instead of tuples, but also applies operator fusion wherever possible [KN11]. Intermediate results are only materialized at pipeline-breakers, which are operators requiring more tuples than there are in registers. HyPer translates queries at runtime using the LLVM framework. Vectorization is thereby introduced by modeling LLVM vector types [Neu11].

MorphStore is a system, which compresses the intermediate results while heavily applying the SIMD paradigm [DUP+20]. In MorphStore, all intermediate results are materialized. This comes with a few advantages, e.g. intermediate results can be used multiple times, and extensively nested loops, which cannot be unrolled by the compiler, are avoided. To minimize the overhead of writing and reading these intermediates, they are compressed using lightweight integer compression, e.g. static bitpacking or delta. For this purpose, a so-called morphing-wrapper decompresses the content of a vector register before it is passed to an operator, and re-compresses the result before it is written to memory. This way, specialized operators do not require an implementation for each compression format. Instead, the core of the operator stays the same. The authors call this method *on-the-fly de-/re-compression*.

#### 2.2.4 Summary

Vectorization, is widely used in different aspects of analytical query execution. Data parallelism is increased by using SIMD registers and instructions in operators and by compressing data. Vectorization is also used to speed up compression itself. We presented a selection of vectorized operators and compression algorithms. All mentioned approaches use explicit vectorization, i.e. they do not solely rely on auto-vectorization. This provides the highest degree of control and, therefore, the best control over any vectorization related optimization knobs. For example, steps like the reorganization of data to enable linear memory access with vector instructions are identified manually. Therefore, it will not happen implicitly. Additionally, auto-vectorization by the compiler is error prone. Some, but by far not all, of the reasons why the compiler might fail to vectorize a piece of code are insufficient optimization of complex loops  $[M^+17]$ , the use of function calls or global pointers, or an unexpected data alignment [ZR02]. This is the reason, why we will address explicit vectorization in this work.

Finally, a processing technique is required, which glues operators and compression together to evaluate a query according to an execution plan. We decided for the operatorat-a-time technique to make the best use of modern CPU features.

#### HARDWARE TRENDS AND EFFECTS ON QUERY PROCESSING

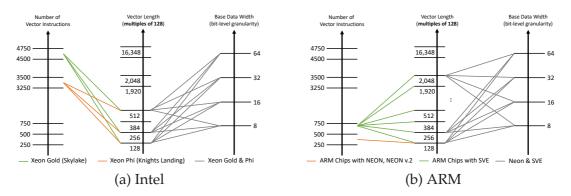

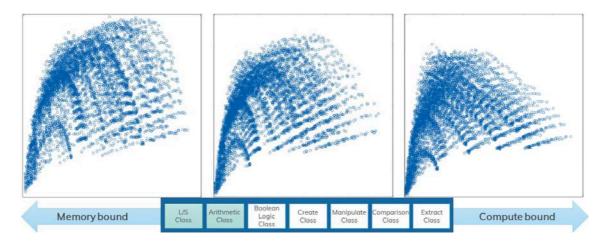

As shown in the last section, there is a huge variety of approaches to vectorize operators, compression, operators for compressed data, and even whole execution engines. However, all of them address a specific target architecture limiting their applicability, because hardware architectures are diverse and change over time, e.g. the cell engine MonetDB/X100 [HNZB07] is optimized for, is not produced anymore. The SSE and AVX instruction sets, which many originally vectorized operators and compression algorithms were developed for, e.g. [WPB+09, ZHNB06, ZR02, SGL10], have been extended by other instruction sets, which offer wider registers or more instructions, i.e. AVX2 and AVX512. Moreover, different instruction sets are available on different CPUs. The SIMD instruction landscape is diverse. Figure 2.6 shows the availability of SIMD instruction sets and vector registers on different Intel and ARM CPUs. The left side of each graph shows the number of available instructions, the middle shows the size of the available vector registers, and the right side shows the possible sizes of the vector elements. All of these general-purpose CPUs are able to work on the granularities of common integral data types, i.e. 8, 16, 32, and 64 bit. However, the number of available instructions and the vector register sizes differ, even between CPUs of the same manufacturer. For instance, the Xeon Gold and the Xeon Phi are both made by Intel® and support the SSE-, AVX-, and AVX512- instruction sets, but they support different subsets of AVX512. Thus, even though both CPUs can work on 128-bit, 256-bit, and 512-bit registers, the exact supported instructions are partially different. AMD® CPUs partially support the same SIMD instruction sets as Intel<sup>®</sup> CPUs, i.e. SSE and AVX/AVX2, but also implement their own instruction set extensions, e.g. SSE4a. Recent ARM® CPUs provide the NEON and NEON2 instruction set, which only work on 128-bit registers. SVE, the newest instruction set for  $ARM^{\mathbb{B}}$  cores, which can be tested in an emulator until supporting hardware is available  $^{3}$ , provides scalable vectors between 128 and 2048 bit [SBB+17].

Generally, the trend in SIMD hardware shows two directions. First, there are more instructions providing specialized functionality, e.g. in-register conflict detection with Intel AVX512. Second, the vector registers become larger, e.g. Intel doubles the size with each new major instruction set while ARM introduces scalable vectors up to 2048 bit with their most recent SIMD instruction set SVE. Unfortunately, there is no trend for a standardization of the instruction sets across architectures. As shown with the different supported AVX512 subsets on the Intel CPUs, the opposite is the case. There is no architecture independent standard of what a SIMD instruction set has to offer and how it can be used.

Implementing the same algorithm for different architectures requires significantly different code. Even the port to higher vector sizes on the same architecture includes a certain amount of manual refactoring due to the partially inconsistent naming schemes. For this reason, the implementations of the presented approaches in Section 2.2 cannot be used on architectures they are not designed for, because they use one concrete instruction set and vector size. Moreover, any port to a more recent instruction set, must be done by hand, e.g. an implementation using SSE does run on recent Intel CPUs, but do not use the wider 512-bit registers or any newer instructions, which might increase the performance. Hence, porting any solution to another architecture requires a domain expert of the available instruction set and of the application. However, all previously presented operators and compression implementations use the instruction set and register size, which was the most recent by the time the solutions were developed. This rises two questions: (1) When and how is it beneficial to port a solution to larger vector registers and new instruction sets? (2) How can the manual part of porting a solution be minimized without

<sup>&</sup>lt;sup>3</sup>Emulator available at https://developer.arm.com/tools-and-software/server-and-hpc/compile/ arm-instruction-emulator, accessed: 11/04/2020

Figure 2.6: Diversity in the SIMD hardware landscape.

eliminating the explicit vectorization as used in the solutions presented in Section 2.2? We address these questions in Section 2.3.1

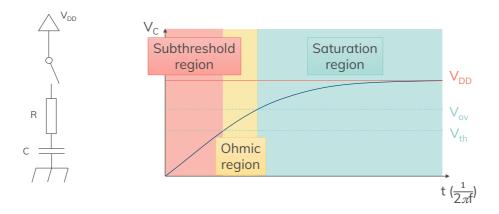

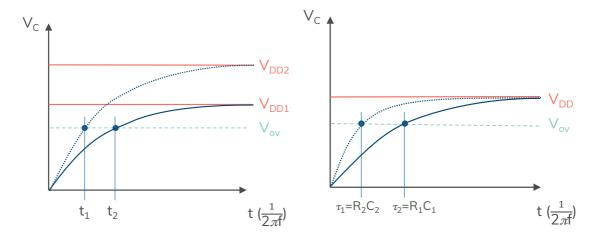

Finally, the chosen instruction set and vector size influences the CPU frequency [Int20] potentially leading to more internal changes, e.g. the memory bus frequency. This is because the circuits implementing SIMD functionality, are more complex than those implementing scalar functionality, but the number of transistors, which can be powered at the same time, is limited [EBA+11]. This leads to a different energy consumption depending on the used instruction set. Hence, it makes sense to not only optimize a vectorized solution for performance, but also for energy consumption. Section 2.3.2 describes the relationship between energy consumption and a chosen instruction set in more detail.

#### 2.3.1 Diversity of Instruction Sets and Vector Sizes

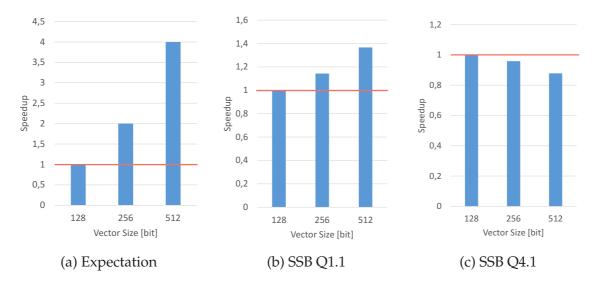

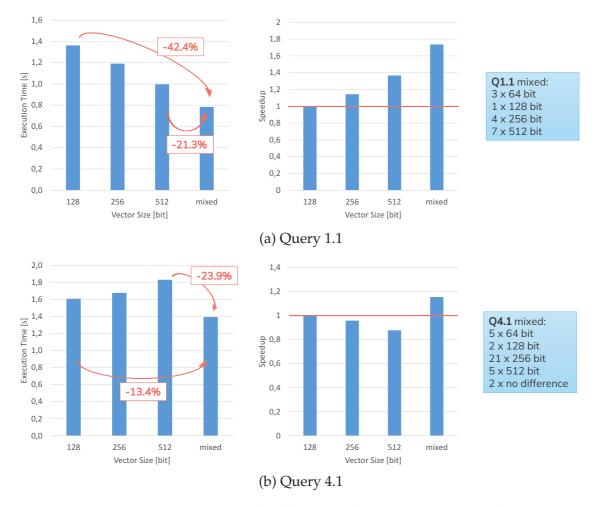

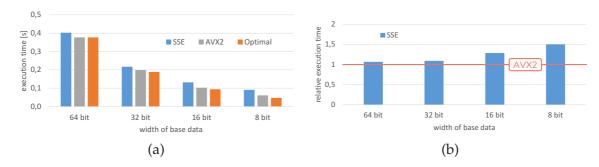

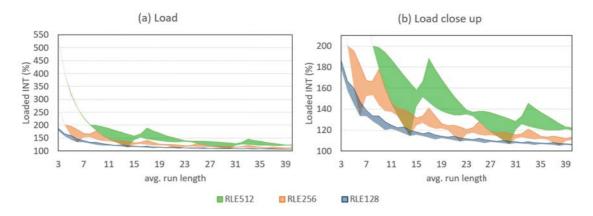

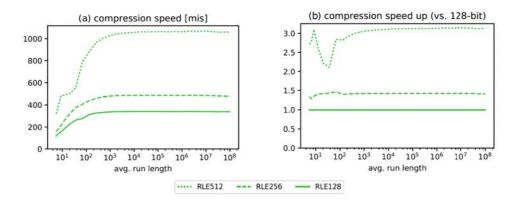

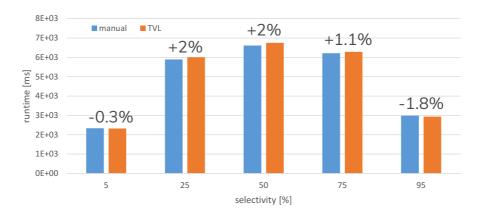

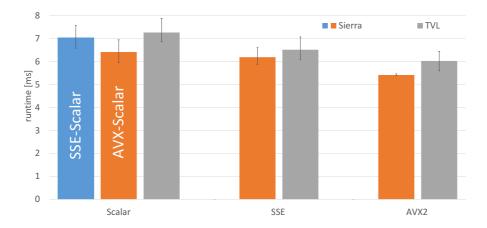

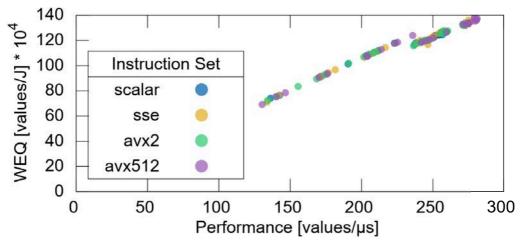

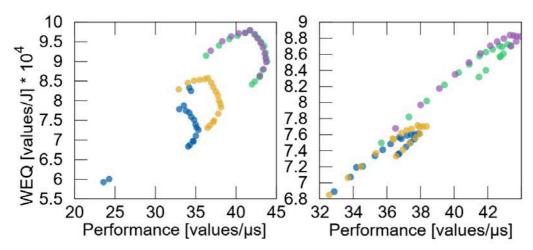

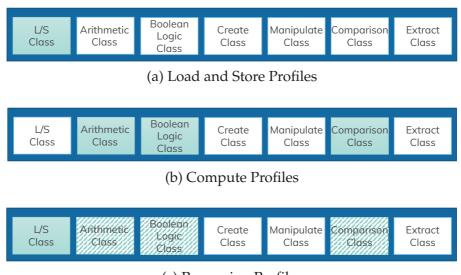

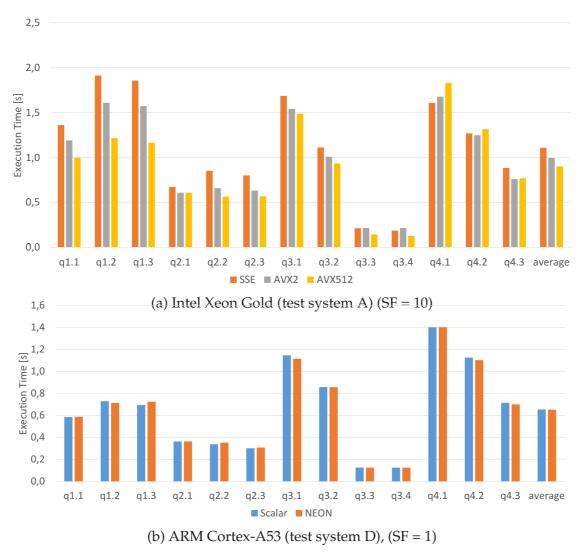

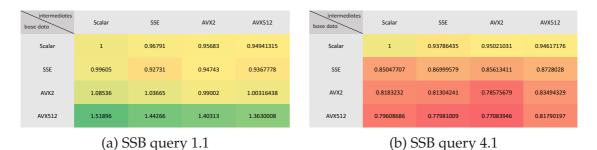

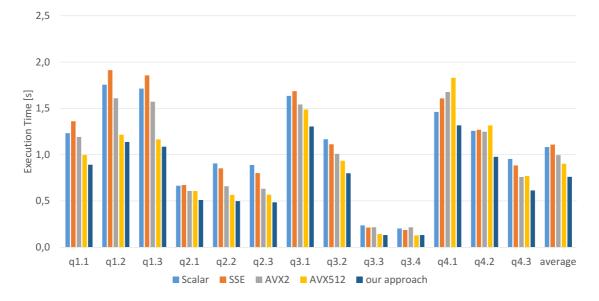

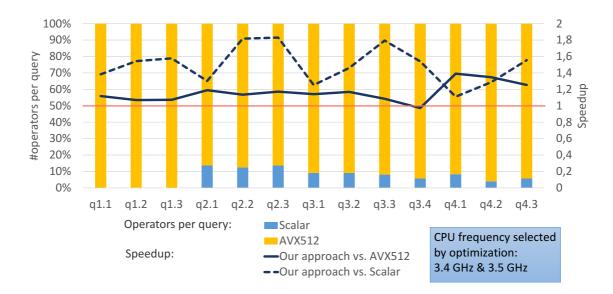

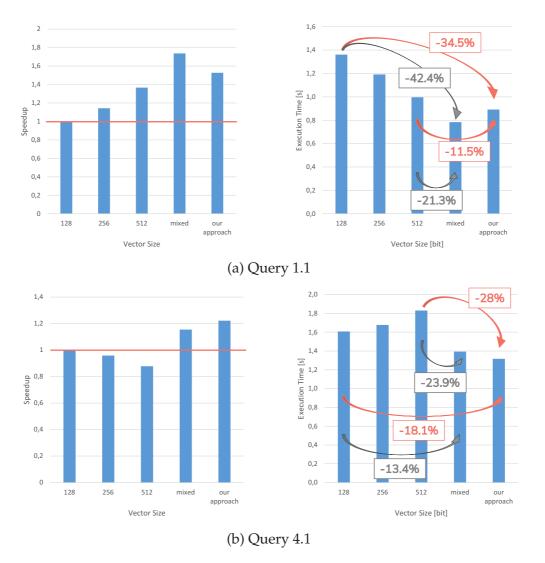

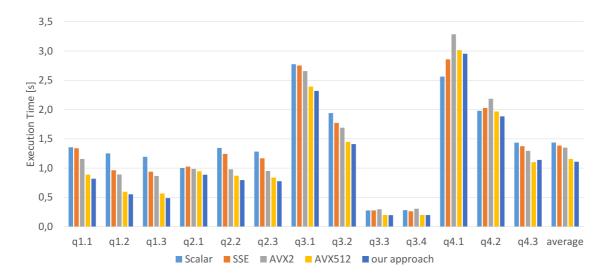

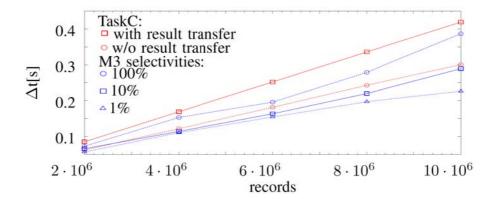

When using wider registers, the increased parallelism should lead to a higher performance. That expectation is depicted in Figure 2.7(a). To check, if this holds true in reality, we run the Star Schema Benchmark (SSB), which is based on the data warehousing benchmark TPC-H [OOC07]. It consists of 13 analytical queries on denormalized tables organized in a star schema. This means that there is one fact table, called *Lineorder*, which references several dimension table, e.g. Customer and Supplier.

We run the SSB with different instruction sets on an Intel Xeon, which supports the instruction sets SSE, AVX2, and AVX512 with their native vector widths of 128, 256, and 512 bit. All values were dictionary encoded, so all queries process integer values. All data is stored column-wise and reside completely in main memory. The operators for all vector sizes follow the same algorithm, regardless of the used instruction set, and the query execution plan is the same as well. Hence, we used a basic in-memory column-store query engine. From this benchmark, we extracted the results of two representative queries as shown in Figure 2.7(b) and (c). The graph shows the speed-up for different vector widths compared with 128-bit registers. Query 1.1 scales almost as expected. While the speedup from using a larger register is not as high as expected, there still is a performance gain compared to the use of a smaller register. The limited scalability could be explained by the limited memory bandwidth. In contrast, query 4.1 shows the reverse behavior, which cannot be explained trivially. The widest register size offering the worst performance seems to be in conflict with the increased data parallelism.

As a consequence, the choice of the SIMD instruction set and the according vector size turns out to be an important optimization knob. This optimization potential becomes even larger when the vector size is not chosen on the query level, but on the operator

Figure 2.7: Expectation versus reality. The queries of the Star-Schema-Benchmark scale differently and not as expected. A wider vector size does not guarantee faster query execution.

level. Figure 2.8 shows the results of the SSB queries 1.1 and 4.1 again with an added bar for the theoretically reachable optimum. This optimum represents a mixed choice of vector sizes. It is the sum of the execution times of each operator, where the vector size with the shortest execution time is chosen per operator. We also considered scalar processing for this mixed scenario. The boxes next to the graphs indicate how many operators use each available vector width. They show, that both queries require all available vector sizes to reach the best performance. An interesting insight is, that the vector size, which is optimal for most operators is not necessarily the best for the whole query. In this case, most operators in query 4.1 profit from using 256-bit registers. But the overall query has the shortest execution time with 128-bit registers. In this specific query, the execution is dominated by a semi join taking at least six times longer than any other operator. This semi join has the longest execution time when using registers, which are 256 bit or larger, which is sufficient to render the benefits of the other operators useless. This seemingly unpredictable behavior exposes a differentiated potential for optimization.

**Absolute optimization potential** is the difference between the worst case and the mixed optimum. For query 1.1 (Figure 2.8a), the worst case scenario is the use of 128bit registers. The optimization potential, i.e. the difference between 128-bit registers and the mixed processing, is 42.4%. For query 4.1 (Figure 2.8b), the worst case scenario is 512-bit registers. The according absolute optimization potential is 23.9%.

**Relative optimization potential** is the difference between an already existing optimization and the mixed optimum. An already existing trivial optimization would be the use of the largest available registers, which is 512 bit in our case. For this trivial approach, the relative and absolute optimization potential for query 4.1 are the same. For query 1.1, 512 bit is the best case scenario for a register choice on query granularity. The relative optimization potential is 21.3%, almost half of the absolute optimization potential, but still significant. Assuming that there is already a way to find the best performing vector size on a per query basis, the relative optimization potential for query 1.1 would not change, but for query 4.1 it would decrease to 13.4%. However, to the best of our knowledge, such a reliable optimization does not exist, yet.

Figure 2.8: The optimization potential of choosing the right vector size. The mixed bar shows the theoretically reachable execution time if every operator was executed with the optimal vector size.

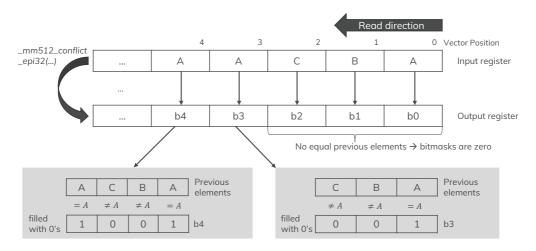

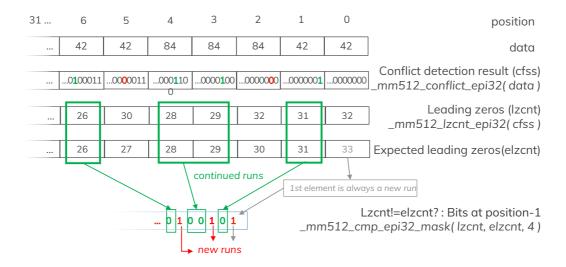

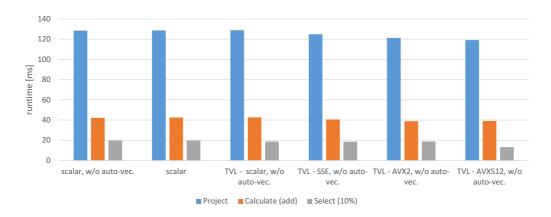

The example shows two main challenges for vectorized column-store engines: First, there seem to be new bottlenecks introduced by larger registers. In Section 3.1, we will have a deep dive into the reasons for this behavior and present a concrete solution for RLE using specialized instructions of the AVX512 instruction set, which go beyond basic logic and arithmetic operations. Second, the right choice of the vector register size and the instruction set is beneficial for the performance of query execution. To do this, there must be implementations to choose from. The implementation of another physical operator for each combination of register size (r), instruction set (s), data type (t), and operator algorithm (o), is a possible solution. However, this solution requires  $r \cdot s \cdot t \cdot o$  implementations for each operator, and ideally, they all provide the same interface. Moreover, the developer solving this task has to be a domain expert not only in database development, but also in all target architectures, i.e. he has to know all the instruction sets. The optimal solution for the database developer, as well as for a potential optimizer, is that there is only one implementation of each physical operator, which is independent of the register size, data type, or instruction set. The mapping to these quantities is not done during development but during compile time or runtime. This concept provides a unified interface for the optimizer and a separation of concerns for the developer. Concretely, no multidomain expert is necessary anymore because the database developer does not implement for a number of specific architectures, while the back-end developer needs no knowledge about the application domain. This concept can be realized by a library, which provides

|      |       |          |         |                                               |     |     |     |     |     |     | #   | of a | ctive | core | es / r | naxii | num | cor | e fre | quer | icy in | tur | bo n | node | (GH | z)  |     |     |     |     |     |     |

|------|-------|----------|---------|-----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|------|-------|------|--------|-------|-----|-----|-------|------|--------|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|

| SKU  | Cores | LLC (MB) | TDP (W) | Base<br>non-AVX<br>Core<br>Frequency<br>(GHz) | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8    | 9     | 10   | 11     | 12    | 13  | 14  | 15    | 16   | 17     | 18  | 19   | 20   | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  |

| 8176 | 28    | 38.50    | 165     | 2.1                                           | 3.8 | 3.8 | 3.6 | 3.6 | 3.5 | 3.5 | 3.5 | 3.5  | 3.5   | 3.5  | 3.5    | 3.5   | 3.4 | 3.4 | 3.4   | 3.4  | 3.1    | 3.1 | 3.1  | 3.1  | 2.9 | 2.9 | 2.9 | 2.9 | 2.8 | 2.8 | 2.8 | 2.8 |

| 8170 | 26    | 35.75    | 165     | 2.1                                           | 3.7 | 3.7 | 3.5 | 3.5 | 3.4 | 3.4 | 3.4 | 3.4  | 3.4   | 3.4  | 3.4    | 3.4   | 3.3 | 3.3 | 3.3   | 3.3  | 3.0    | 3.0 | 3.0  | 3.0  | 2.8 | 2.8 | 2.8 | 2.8 | 2.8 | 2.8 |     |     |

| 8164 | 26    | 35.75    | 150     | 2.0                                           | 3.7 | 3.7 | 3.5 | 3.5 | 3.4 | 3.4 | 3.4 | 3.4  | 3.4   | 3.4  | 3.4    | 3.4   | 3.2 | 3.2 | 3.2   | 3.2  | 2.9    | 2.9 | 2.9  | 2.9  | 2.7 | 2.7 | 2.7 | 2.7 | 2.7 | 2.7 |     |     |

| 8160 | 24    | 33.00    | 150     | 2.1                                           | 3.7 | 3.7 | 3.5 | 3.5 | 3.4 | 3.4 | 3.4 | 3.4  | 3.4   | 3.4  | 3.4    | 3.4   | 3.2 | 3.2 | 3.2   | 3.2  | 3.0    | 3.0 | 3.0  | 3.0  | 2.8 | 2.8 | 2.8 | 2.8 |     |     |     |     |

| 6152 | 22    | 30.25    | 140     | 2.1                                           | 3.7 | 3.7 | 3.5 | 3.5 | 3.4 | 3.4 | 3.4 | 3.4  | 3.4   | 3.4  | 3.4    | 3.4   | 3.1 | 3.1 | 3.1   | 3.1  | 2.9    | 2.9 | 2.9  | 2.9  | 2.8 | 2.8 |     |     |     |     |     |     |

| 6138 | 20    | 27.50    | 125     | 2.0                                           | 3.7 | 3.7 | 3.5 | 3.5 | 3.4 | 3.4 | 3.4 | 3.4  | 3.2   | 3.2  | 3.2    | 3.2   | 2.9 | 2.9 | 2.9   | 2.9  | 2.7    | 2.7 | 2.7  | 2.7  |     |     |     |     |     |     |     |     |

| 6140 | 18    | 24.75    | 140     | 2.3                                           | 3.7 | 3.7 | 3.5 | 3.5 | 3.4 | 3.4 | 3.4 | 3.4  | 3.4   | 3.4  | 3.4    | 3.4   | 3.1 | 3.1 | 3.1   | 3.1  | 3.0    | 3.0 |      |      |     |     |     |     |     |     |     |     |

| 8153 | 16    | 22.00    | 125     | 2.0                                           | 2.8 | 2.8 | 2.6 | 2.6 | 2.5 | 2.5 | 2.5 | 2.5  | 2.5   | 2.5  | 2.5    | 2.5   | 2.3 | 2.3 | 2.3   | 2.3  |        |     |      |      |     |     |     |     |     |     |     |     |

| 6130 | 16    | 22.00    | 125     | 2.1                                           | 3.7 | 3.7 | 3.5 | 3.5 | 3.4 | 3.4 | 3.4 | 3.4  | 3.1   | 3.1  | 3.1    | 3.1   | 2.8 | 2.8 | 2.8   | 2.8  |        |     |      |      |     |     |     |     |     |     |     |     |

|      |       | # of active cores / maximum core frequency in turbo mode (GHz) |         |                                               |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|------|-------|----------------------------------------------------------------|---------|-----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| SKU  | Cores | LLC (MB)                                                       | TDP (W) | Base<br>AVX-512<br>Core<br>Frequency<br>(GHz) | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  |

| 8176 | 28    | 38.50                                                          | 165     | 1.3                                           | 3.5 | 3.5 | 3.3 | 3.3 | 3.0 | 3.0 | 3.0 | 3.0 | 2.6 | 2.6 | 2.6 | 2.6 | 2.3 | 2.3 | 2.3 | 2.3 | 2.1 | 2.1 | 2.1 | 2.1 | 2.0 | 2.0 | 2.0 | 2.0 | 1.9 | 1.9 | 1.9 | 1.9 |

| 8170 | 26    | 35.75                                                          | 165     | 1.3                                           | 3.5 | 3.5 | 3.3 | 3.3 | 2.9 | 2.9 | 2.9 | 2.9 | 2.5 | 2.5 | 2.5 | 2.5 | 2.2 | 2.2 | 2.2 | 2.2 | 2.1 | 2.1 | 2.1 | 2.1 | 1.9 | 1.9 | 1.9 | 1.9 | 1.9 | 1.9 |     |     |

| 8164 | 26    | 35.75                                                          | 150     | 1.2                                           | 3.5 | 3.5 | 3.3 | 3.3 | 2.8 | 2.8 | 2.8 | 2.8 | 2.4 | 2.4 | 2.4 | 2.4 | 2.1 | 2.1 | 2.1 | 2.1 | 1.9 | 1.9 | 1.9 | 1.9 | 1.8 | 1.8 | 1.8 | 1.8 | 1.8 | 1.8 |     |     |

| 8160 | 24    | 33.00                                                          | 150     | 1.4                                           | 3.5 | 3.5 | 3.3 | 3.3 | 3.0 | 3.0 | 3.0 | 3.0 | 2.6 | 2.6 | 2.6 | 2.6 | 2.3 | 2.3 | 2.3 | 2.3 | 2.1 | 2.1 | 2.1 | 2.1 | 2.0 | 2.0 | 2.0 | 2.0 |     |     |     |     |

| 6152 | 22    | 30.25                                                          | 140     | 1.4                                           | 3.5 | 3.5 | 3.3 | 3.3 | 2.9 | 2.9 | 2.9 | 2.9 | 2.5 | 2.5 | 2.5 | 2.5 | 2.2 | 2.2 | 2.2 | 2.2 | 2.0 | 2.0 | 2.0 | 2.0 | 2.0 | 2.0 |     |     |     |     |     |     |

| 6138 | 20    | 27.50                                                          | 125     | 1.3                                           | 3.5 | 3.5 | 3.3 | 3.3 | 2.7 | 2.7 | 2.7 | 2.7 | 2.3 | 2.3 | 2.3 | 2.3 | 2.0 | 2.0 | 2.0 | 2.0 | 1.9 | 1.9 | 1.9 | 1.9 |     |     |     |     |     |     |     |     |

| 6140 | 18    | 24.75                                                          | 140     | 1.5                                           | 3.5 | 3.5 | 3.3 | 3.3 | 2.8 | 2.8 | 2.8 | 2.8 | 2.4 | 2.4 | 2.4 | 2.4 | 2.1 | 2.1 | 2.1 | 2.1 | 2.1 | 2.1 |     |     |     |     |     |     |     |     |     |     |

| 8153 | 16    | 22.00                                                          | 125     | 1.2                                           | 2.6 | 2.6 | 2.4 | 2.4 | 2.0 | 2.0 | 2.0 | 2.0 | 1.7 | 1.7 | 1.7 | 1.7 | 1.6 | 1.6 | 1.6 | 1.6 |     |     |     |     |     |     |     |     |     |     |     |     |

| 6130 | 16    | 22.00                                                          | 125     | 1.3                                           | 2.5 | 2 5 | 2.1 | 2.1 | 2.4 | 2.4 | 2.4 | 2.4 | 2.1 | 2.1 | 2.1 | 2.1 | 1.0 | 1.0 | 1.9 | 1.0 |     |     |     |     |     |     |     |     |     |     |     |     |

The 8176, 8170, 8160, and 6140 have 1.5 TB/socket memory capacity versions (8180M, 8170M, 8160M, and 6140M - not listed previously) with identical frequencies.

Figure 2.9: The maximum core frequencies of different Intel CPUs depending on the number of active cores when no SIMD extension is used and when AVX512 is used. Images taken from [Int20]

generic interfaces for all required functions and operators. The challenge is to find out how such a library must be realized to be applicable for the development of a query execution engine. We will cover this challenge in Section 3.2, where we introduce the general design of such a library.

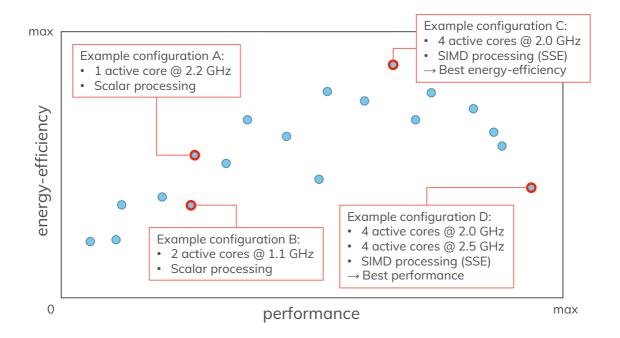

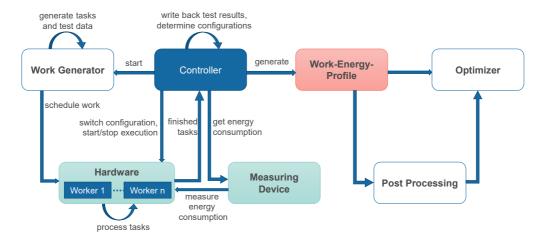

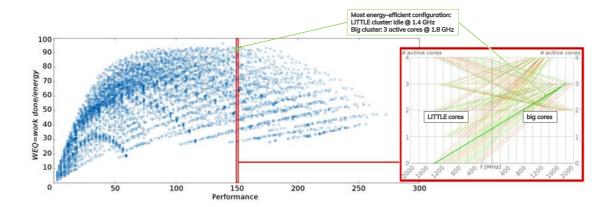

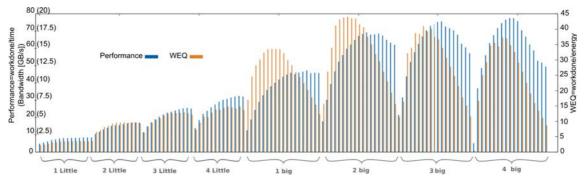

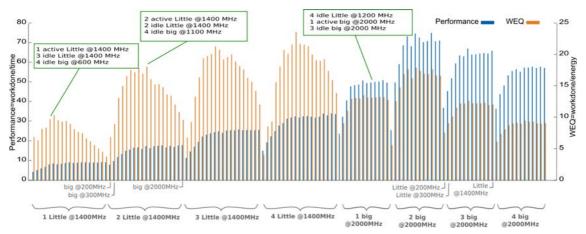

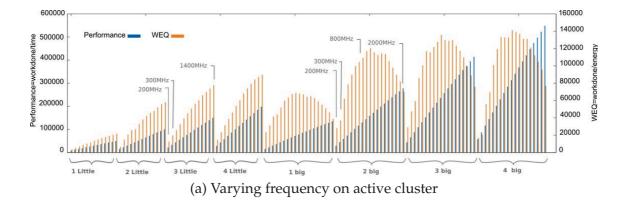

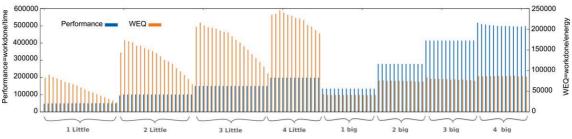

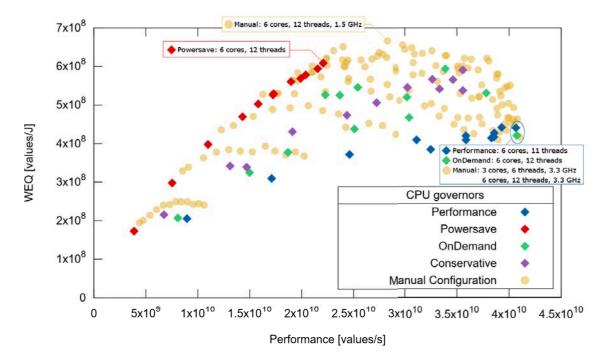

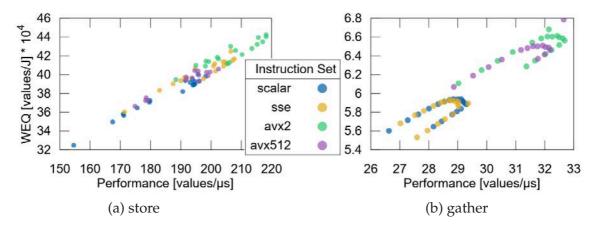

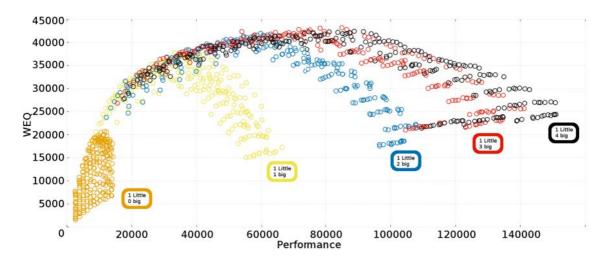

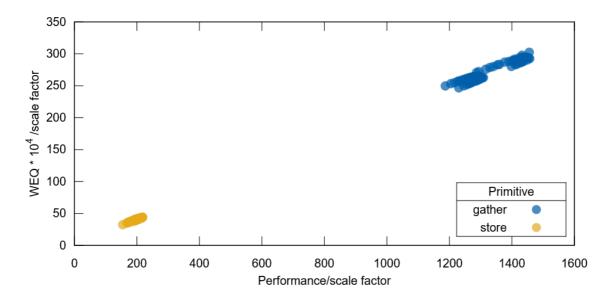

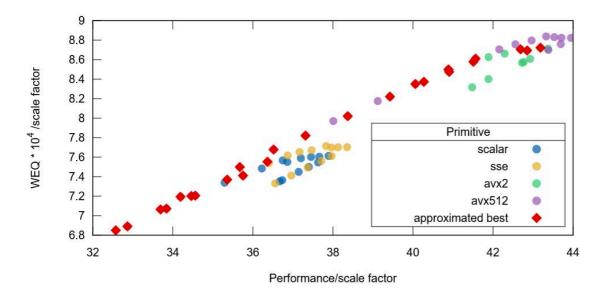

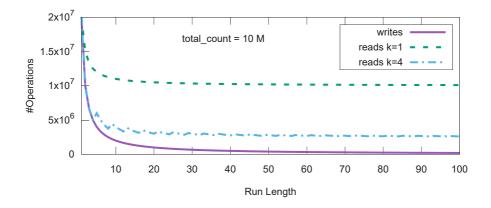

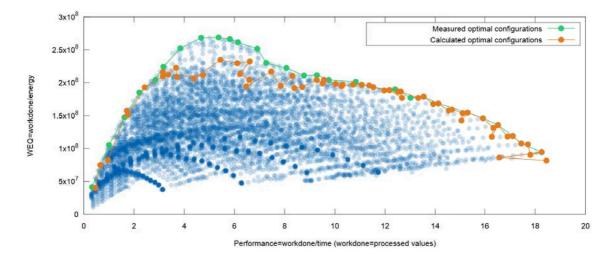

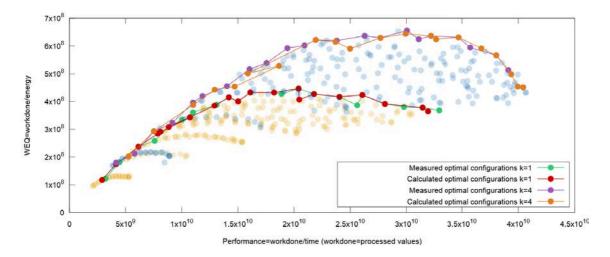

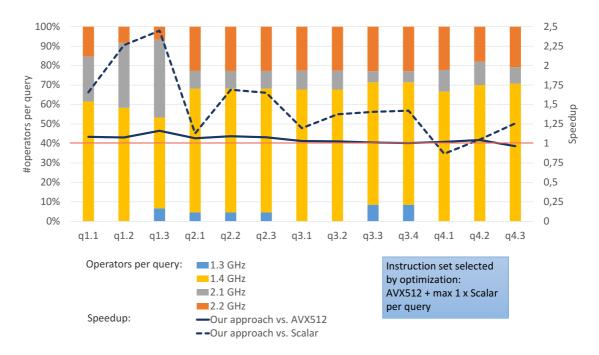

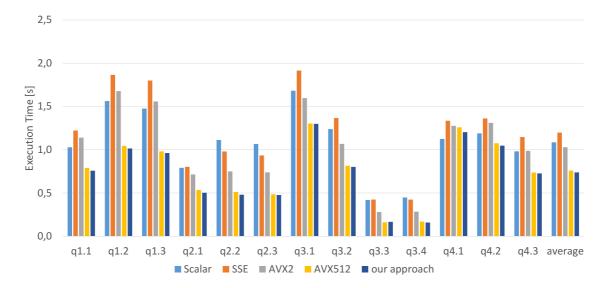

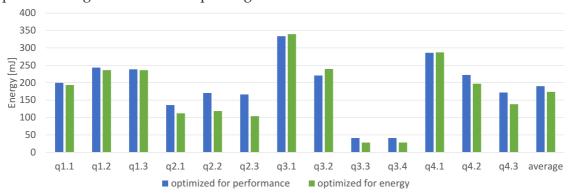

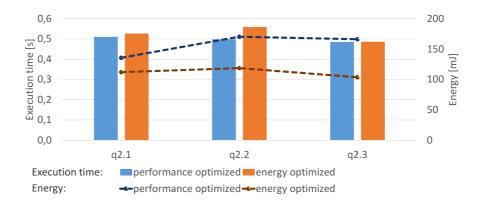

#### 2.3.2 Physical Constraints and Energy Consumption