INSTITUTE FOR MATERIALS SCIENCE CHAIR OF MATERIALS SCIENCE AND NANOTECHNOLOGY DEPARTMENT FOR MECHANICAL ENGINEERING DRESDEN UNIVERSITY OF TECHNOLOGY

# Multi-functional Hybrid Gating Silicon Nanowire Field-effect Transistors: From Optoelectronics to Neuromorphic Application

DISSERTATION for obtaining the degree of DOCTOR OF ENGINEERING (Dr.-Ing.)

submitted by

Eunhye Baek born on 9th of March 1988 in Choengju, Korea

August 2018

- 1. Reviewer: Prof. Dr. Gianaurelio Cuniberti (TU Dresden)

- 2. Reviewer: Prof. Dr. Ronald Tetzlaff (TU Dresden)

Defense on [ ]th of [ ] 2018

Institut für Werkstoffwissenschaft Lehrstuhl Materialwissenschaft und Nanotechnik Fakultät Maschinenwesen Technische Universität Dresden

# Multifunktionale Hybrid-Gating-Silizium-Nanodraht-Feldeffekttransistoren: Von der Optoelektronik zur neuromorphen Anwendung

Dissertation Zur Erlangung des wissenschaftlichen Grades Doktoringenieur (Dr.-Ing.)

vorgelegt von

Eunhye Baek Geboren am 09.03.1988 in Choengju, Korea

August 2018

- 1. Gutachter: Prof. Dr. Gianaurelio Cuniberti (TU Dresden)

- 2. Gutachter: Prof. Dr. Ronald Tetzlaff (TU Dresden)

Verteidigt am [ ]th of [ ] 2018

Quest'opera è dedicata al sole splendente di Milazzo, 그리고 사랑하는 나의 가족들에게 바칩니다.

#### Abstract

Enormous demands for fast and low-power computing and memory building blocks for consumer electronics, such as smartphones or tablets, have led to the emergence of silicon nanowire transistors a decade ago. Along with the Si-based nanotechnology, the silicon compatible optical and chemical sensing applications have boosted the research on hybrid devices that combine the organic and inorganic materials. Apart from the revolution in the device dimensions, the rapid growth of artificial intelligence in the software industry brunch requires the next generation's computers with the revolutionized hybrid device architecture. Implementing such new devices can effectively perform machine learning tasks without the massive consumption of energy. The hybrid Si nanowire devices have an excellent capability to replace the conventional computing element by providing new functionalities of combined materials to the traditional transistor devices preserving the advantage of CMOS technology.

A goal of this thesis is **to develop functional hybrid Si nanowire-based transistors modulated by the stimuli-dependent gate** to go beyond the current digital building blocks. The hybrid devices converge semiconductor channel and various materials from organic molecules to silicate composite as a gate of the transistor. External stimuli change the electronic state of the gate materials which is transformed to the gate potential of the transistors.

First, this thesis studies the electronic characteristics of the Si nanowire FETs under the optical stimulus. Optical stimulus induces the strong conductance change on bare Si nanowire FETs. Under the light with low power intensity, the transistor shows an unconventional negative photoconductance (NPC) which is dependent on the doping concentration of the nanowire and the wavelength of the incident light. The dopants ions and surface states cause photo-generated hot electrons trapping which restricts conventional photoconductance in the semiconductor.

In the hybrid device, however, the gate material on the Si dioxide layer plays a significant role in the optoelectronic modulation of the FET device. This thesis demonstrates that an organic photochromic material, porphyrin, wrapping around the nanowire channel acts as an optical gate of the Si nanowire transistor. The diffusive property of electrons in the molecular film decides the optical switching dynamics and efficiency.

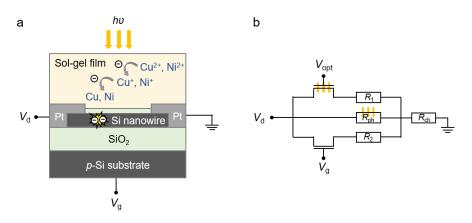

Further, this thesis introduces new functional gate material, *sol-gel derived ion-doped silicate film*, based on the availability of stimulus-dependent gate modulation. This amorphous and transparent silicate film shows memristive property due to the ionic redistribution in the film under bias condition. Interestingly, the sol-gel film-coated Si nanowire FETs the devices show a double gate effect cooperating with a back gate under light illumination which is due to the channel separation in the fin structure of the nanowire.

In addition, the sol-gel silicate film-coated Si nanowire transistor emulates the neuronal plasticity with pulsed gate stimulation, namely "*neurotransistor*." Because of the mobile ions in the silicate film, the transistor has a short-term memory and mimics membrane potential change of the neuron cell. The neurotransistor could be used as a computing node in the physical neural network for hardware machine learning.

This work demonstrates that the physical properties of the gate material decide the transfer characteristics and time-dependent dynamics of the hybrid Si nanowire transistors. The optical and neuromorphic gate features of the hybrid transistors would accelerate the advancement of an optical or brain-like computing machine.

#### Kurzfassung

Enorme Anforderungen an schnelle und stromsparende Rechen- und Speicherbausteine für die Unterhaltungselektronik, wie Smartphones oder Tablets, haben vor einem Jahrzehnt zur Entstehung von Silizium-Nanodraht-Transistoren geführt. Zusammen mit der Si-basierten Nanotechnologie haben die siliziumkompatiblen optischen und chemischen Sensoranwendungen die Forschung an hybriden Bauelementen, die organische und anorganische Materialien kombinieren, vorangetrieben. Neben der Revolution in den Geräteabmessungen erfordert das rasante Wachstum der künstlichen Intelligenz im Software-Branchenbrunch die Computer der nächsten Generation mit der revolutionierten hybriden Gerätearchitektur. Durch den Einsatz solcher neuen Geräte können maschinelle Lernaufgaben ohne massiven Energieverbrauch effektiv durchgeführt werden. Die hybriden Si-Nanodraht-Bauelemente haben eine ausgezeichnete Fähigkeit, das herkömmliche Rechenelement zu ersetzen, indem sie den traditionellen Transistorbauelementen neue Funktionalitäten aus kombinierten Materialien bieten und den Vorteil der CMOS-Technologie bewahren.

Ein Ziel dieser Arbeit ist es, funktionelle hybride Si-Nanodraht-basierte Transistoren zu entwickeln, die durch das stimuli-abhängige Gate moduliert werden, um über die aktuellen digitalen Bausteine hinauszugehen. Die hybriden Bauelemente konvergieren Halbleiterkanal und verschiedene Materialien von organischen Molekülen zu Silikatverbundwerkstoffen als Gate des Transistors. Externe Reize verändern den elektronischen Zustand der Gate-Materialien, der in das Gate-Potential der Transistoren umgewandelt wird.

Erstens, diese These untersucht die elektronischen Eigenschaften der Si-Nanodraht-FETs unter dem optischen Reiz. Der optische Reiz induziert die starke Leitwertänderung bei blanken Si-Nanodraht-FETs. Unter dem Licht mit geringer Leistungsintensität zeigt der Transistor eine unkonventionelle negative Photoleitfähigkeit (NPC), die von der Dotierungskonzentration des Nanodrahtes und der Wellenlänge des einfallenden Lichts abhängig ist. Die Dotierstoffe Ionen und Oberflächenzustände verursachen photogenerierte heiße Elektronen, die die konventionelle Photoleitfähigkeit im Halbleiter einschränken.

Im Hybridbauteil spielt jedoch das Gatematerial auf der Si-Dioxid-Schicht eine wesentliche Rolle bei der optoelektronischen Modulation des FET-Bauteils. Diese Arbeit zeigt, dass ein organisches photochromes Material, Porphyrin, das sich um den Nanodrahtkanal wickelt, als optisches Gate des Si-Nanodrahttransistors wirkt. Die Diffusionseigenschaft der Elektronen im Molekularfilm entscheidet über die optische Schaltdynamik und Effizienz.

In dieser Arbeit wird außerdem ein neues funktionelles Gate-Material vorgestellt, ein Sol-Geldotierter Silikatfilm, der auf der Verfügbarkeit von stimulierungsabhängiger Gate-Modulation basiert. Diese amorphe und transparente Silikat-Film zeigt memristive Eigenschaft durch die ionische Umverteilung in den Film unter Bias-Bedingung. Interessanterweise zeigen die mit Sol-Gel beschichteten Si-Nanodraht-FETs einen Doppelgate-Effekt, der durch die Kanaltrennung in der Lamellenstruktur des Nanodrahtes mit einem Hintertor unter Beleuchtung zusammenwirkt.

Darüber hinaus emuliert der mit Sol-Gel-Silikat beschichtete Si-Nanodrahttransistor die neuronale Plastizität mit gepulster Gatestimulation, dem "Neurotransistor". Durch die beweglichen Ionen im Silikatfilm hat der Transistor ein Kurzzeitgedächtnis und imitiert die Membranpotentialänderung der Neuronenzelle. Der Neurotransistor könnte als Rechenknoten im physikalischen neuronalen Netz für das maschinelle Lernen eingesetzt werden.

Diese Arbeit zeigt, dass die physikalischen Eigenschaften des Gatematerials die Übertragungseigenschaften und die zeitabhängige Dynamik der hybriden Si-Nanodrahttransistoren bestimmen. Die optischen und neuromorphen Gate-Eigenschaften der Hybridtransistoren würden die Weiterentwicklung einer optischen oder hirnähnlichen Rechenmaschine beschleunigen.

## <u>CONTENTS</u>

| Aci | ronyms                                                                 | xiii |

|-----|------------------------------------------------------------------------|------|

| Lis | t of Figures                                                           | . xv |

| Lis | t of Tables                                                            | xix  |

| 1.  | Introduction                                                           | 1    |

| 2.  | Hybrid gate Si nanowire field-effect transistors                       | 5    |

|     | 2.1. Si nanowire field-effect transistors                              |      |

|     | 2.2. The field-effect – gate-induced potential distribution            | 9    |

|     | 2.3. Subthreshold region: a fingerprint of the gate signal change      | . 13 |

|     | 2.4. Hybrid electronic element with stimuli-induced gate               | 15   |

| 3.  | Experimental methods                                                   | . 19 |

|     | 3.1. Fabrication of Si nanowire filed effect transistors               | 19   |

|     | 3.1.1 Bottom-up scheme: Schottky-junction Si nanowire FETs             | . 19 |

|     | 3.1.2 Top-down scheme: <i>n</i> - and <i>p</i> -doped Si nanowire FETs | 21   |

|     | 3.1.3 Top-down scheme: Top gate fabrication                            | . 23 |

|     | 3.2. Functional hybrid gate film formation                             | . 24 |

|     | 3.2.1 Organic film formation                                           | 24   |

|     | 3.2.2 Hybrid silicate sol-gel film formation                           | 25   |

|     | 3.3. Electrical characterization of FETs                               | . 25 |

|     | 3.3.1 Photocurrent measurement                                         | 25   |

|     | 3.3.2 Electrical measurement                                           | . 26 |

|     | 3.4. Film analysis                                                     | . 27 |

|     | 3.4.1 Capacitance analysis                                             | 28   |

|     | 3.4.2 Spectroscopic analysis                                           | . 28 |

| 4.  | Intrinsic optical gate: Negative photoconductance in Si nanowire FETs  | . 31 |

|     | 4.1. Photoconductance of Si nanowire                                   | 31   |

|     | 4.2. Negative photoconductance in various nanostructures               | . 34 |

|     | 4.3. Negative photoconductance in Si nanowire FETs                     | . 35 |

|     | 4.4. Light-induced threshold voltage shift and substrate effect        | . 37 |

|     | 4.5. Doping concentration and light intensity dependence               | 39   |

|     | 4.6. Wavelength dependence                                             | . 43 |

|     | 4.7. Conclusion                                                        | 45   |

| 5.  | External optical gate: Organic molecular coated Si nanowire FETs       | 49   |

|     | 5.1. Why organic materials for hybrid applications?                    | . 49 |

|            | 5.2. Hybrid organic/oxide/semiconductor (OOS) nanowire FETs                 | 51  |  |

|------------|-----------------------------------------------------------------------------|-----|--|

|            | 5.3. Optoelectronic switching of hybrid nanowire FETs                       | 54  |  |

|            | 5.4. Optical gating mechanism of hybrid FETs                                | 58  |  |

|            | 5.5. Effect of charge transfer in the organic film                          | 60  |  |

|            | 5.6. Conclusion                                                             | 63  |  |

| <i>6</i> . | Design of functional gate: Ion-doped sol-gel derived silicate film          | 67  |  |

|            | 6.1. Composite sol-gel film as a functional gate                            | 67  |  |

|            | 6.2. Morphology of sol-gel derived film                                     | 70  |  |

|            | 6.3. Dielectric properties                                                  | 73  |  |

|            | 6.4. Electrical properties                                                  |     |  |

|            | 6.5. Optical properties                                                     | 76  |  |

|            | 6.6. Conclusion                                                             | 77  |  |

| 7.         | Optoelectronic double-gate: Ion-doped silicate film coated Si nanowire FETs | 81  |  |

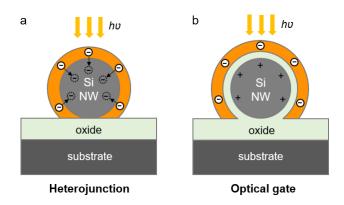

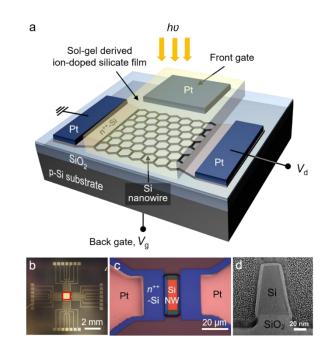

|            | 7.1. Si nanowire hybrid photodetectors                                      | 81  |  |

|            | 7.2. Double-gate transistors                                                | 83  |  |

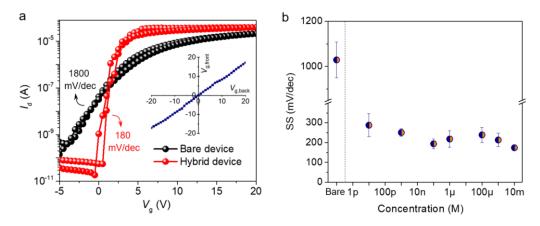

|            | 7.3. Front and back gate coupling                                           | 84  |  |

|            | 7.4. Optical gate coupling effects                                          | 87  |  |

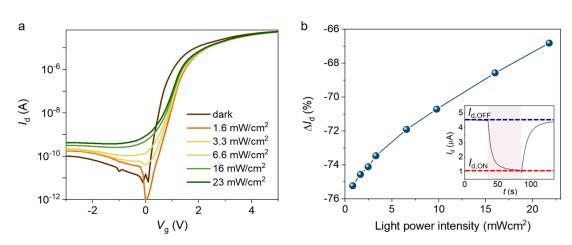

|            | 7.5. Optical current switching characteristics                              | 89  |  |

|            | 7.6. Conclusion                                                             | 90  |  |

| 8.         | History-dependent pseudo gate: Neurotransistors for memory and learning     | 93  |  |

|            | 8.1. Machine mimicking the human brain                                      | 93  |  |

|            | 8.2. Neurotransistors with tunable memory                                   | 96  |  |

|            | 8.3. Intrinsic plasticity in neurotransistors                               | 99  |  |

|            | 8.4. Emulation of memory and learning of neurons                            | 104 |  |

|            | 8.5. Intrinsically multiple output transistor                               | 107 |  |

|            | 8.6. Conclusion                                                             | 108 |  |

| 9.         | Conclusion and outlook                                                      | 115 |  |

|            | 9.1 Conclusion                                                              | 115 |  |

|            | 9.2 Outlook                                                                 | 117 |  |

| Ap         | pendix                                                                      | 120 |  |

| Lis        | of Publication                                                              | 125 |  |

| Ac         | Acknowledgement                                                             |     |  |

| Cu         | rriculum Vitae                                                              | 129 |  |

### <u>ACRONYMS</u>

| BOX     | Buried Oxide                                      |

|---------|---------------------------------------------------|

| CMOS    | Complementary Metal-oxide-semiconductor           |

| CPU     | Central Processing Unit                           |

| CVD     | Chemical Vapor Deposition                         |

| DC      | Direct Current                                    |

| DG      | Double Gate                                       |

| FET     | Field-effect Transistor                           |

| FinFET  | Fin Field-effect Transistor                       |

| GNP     | Gold Nanoparticle                                 |

| НОМО    | Highest Occupied Molecular Orbital                |

| HR-TEM  | High Resolution Transmission Electron Microscopy  |

| ICP-RIE | Inductively Coupled Plasma Reactive Ion Etching   |

| IPA     | Isopropanol                                       |

| ISFET   | Ion-sensitive Field-effect Transistor             |

| LCR     | Inductance (L), Capacitance (C), Resistance (R)   |

| LED     | Light Emitting Diode                              |

| LUMO    | Highest Unoccupied Molecular Orbital              |

| MIGFET  | Multiple Independent Gate Field-effect Transistor |

| MOS     | Metal-oxide-semiconductor                         |

| MTMS    | Trimethoxymethylsilane                            |

| NIR     | Near-infrared                                     |

| NPC     | Negative Photoconductance (Photoconductivity)     |

| OOS     | Organic-oxide-semiconductor                       |

| PECVD   | Plasma-enhanced Chemical Vapor Deposition         |

| PPC     | Positive Photoconductance                         |

| QD      | Quantum Dot                                       |

| SAM    | Self-assembled Monolayer                              |

|--------|-------------------------------------------------------|

| SOI    | Silicon on Insulator                                  |

| SS     | Subthreshold Slop                                     |

| STD    | Short-term Depression                                 |

| STP    | Short-term Potentiation                               |

| TEOS   | Tetraethoxysilane                                     |

| TLM    | Transmission Line Method                              |

| TMOS   | Tetramethyl Orthosilicate                             |

| ТРРОН  | 5,10,15,20-Tetrakis(4-hydroxyphenyl)-21H,23H-porphine |

| UV     | Ultraviolet                                           |

| UV-Vis | Ultraviolet-visible                                   |

| XPS    | X-ray Photoelectron Spectroscopy                      |

| XRD    | X-ray Diffraction                                     |

### LIST OF FIGURES

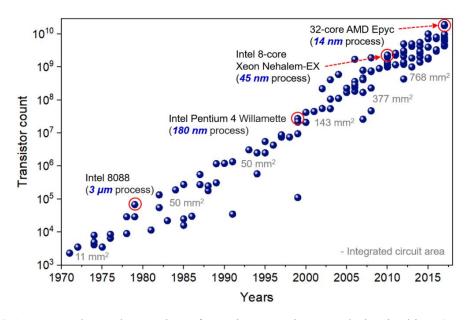

- 2.1 Moore's law: The number of transistors on integrated circuit chips. 6

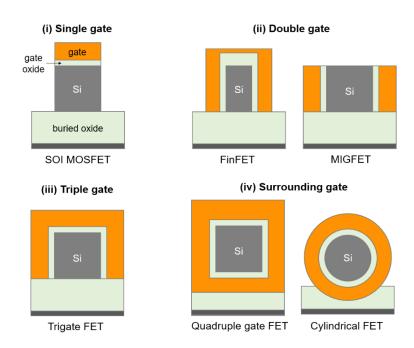

- 2.2 Various gate structures. 7

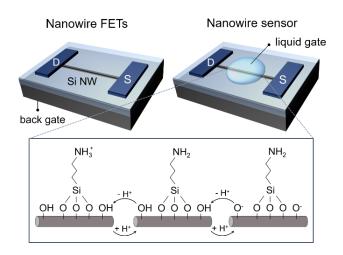

- 2.3 The conversion of the Si nanowire FETs to Si nanowire sensor. 8

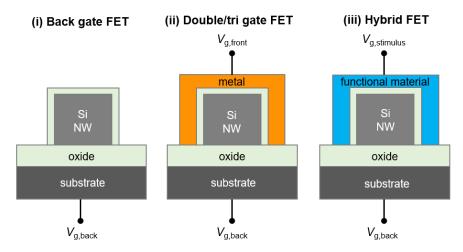

- 2.4 Structural evolution of functional gate field-effect transistors. 9

- 2.5 Energy band diagram of hybrid Si nanowire FETs with double gate. 10

- **2.6** Electric potential  $\varphi$  as a function of position in silicon. 12

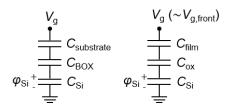

- 2.7 Capacitance model of MOSFET structure with back gate control. 14

- **2.8** Variation of front and back gate potential distribution and their corresponding transfer characteristics. 14

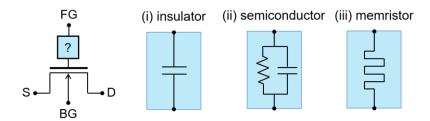

- 2.9 Various circuit elements for the hybrid gate. 15

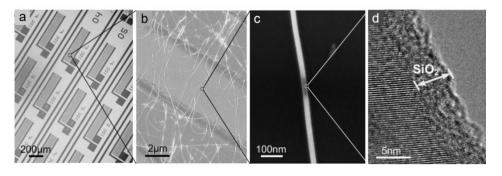

- 3.1 Microscopic images of Schottky-barrier Si nanowire FETs. 20

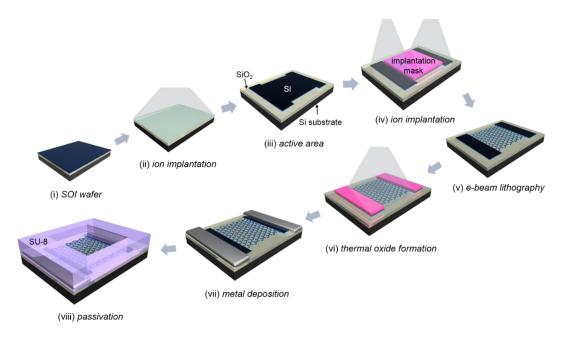

- 3.2 The steps of the top-down nanowire device fabrication. 21

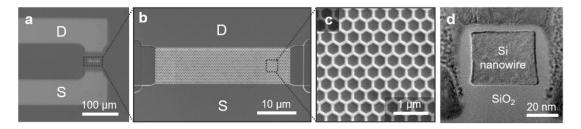

- 3.3 Structure of honeycomb Si nanowire FETs. 22

- 3.4 SEM images of the top electrode configuration on a honeycomb nanowire device. 23

- 3.5 Photocurrent measurement setup. 26

- 3.6 Block diagram of pulse measurement setup. 27

- 3.7 Microscopic image of the patterned gold electrodes for capacitance measurement. 28

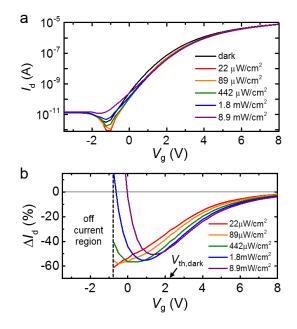

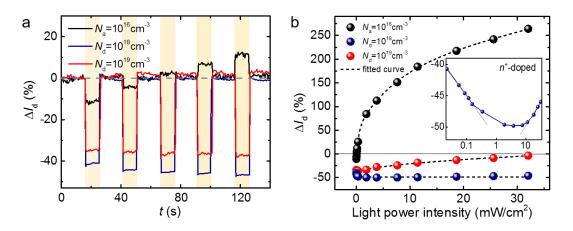

- 4.1 Photoconductance of a boron-doped (p-type) Si nanowire FET. 33

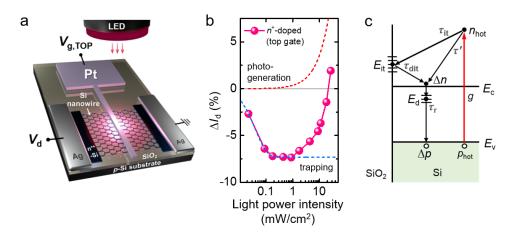

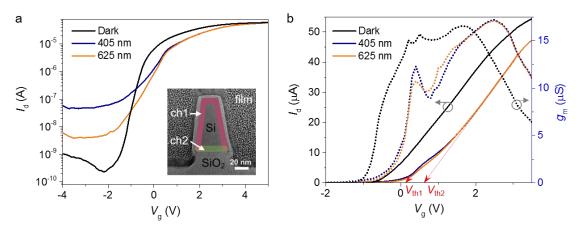

- 4.2 Structure and electrical characteristics of honeycomb Si nanowire FETs under illumination. 36

- 4.3 The current change depending on gate bias under light illumination. 37

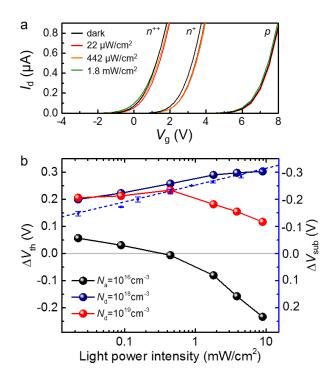

- **4.4** Transfer curve shift under illumination of the Si nanowire devices with various doping concentration, and Threshold voltage shift of the devices depending on the light power intensity, which is compared with the substrate potential change by illumination. 38

- 4.5 Photocurrent change of the devices with various doping concentration. 40

- 4.6 Negative photoconductivity of the Si nanowire device without substrate effect. 41

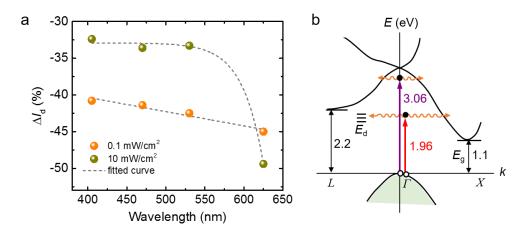

- 4.7 Wavelength dependence of photocurrent change of the n<sup>+</sup>-doped back gate device with weak and strong light power intensity, and the schematic energy band diagram of Si under visible light illumination. 44

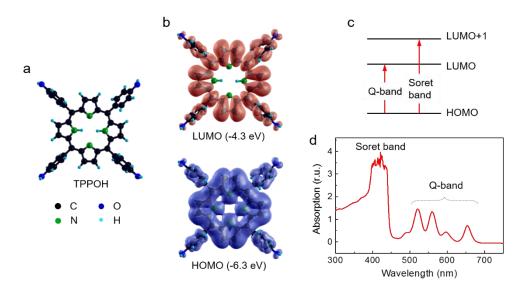

- 5.1 The physical characteristics of 5,10,15,20-Tetrakis(4-hydroxyphenyl)-21H,23H-porphine (TPPOH). 50

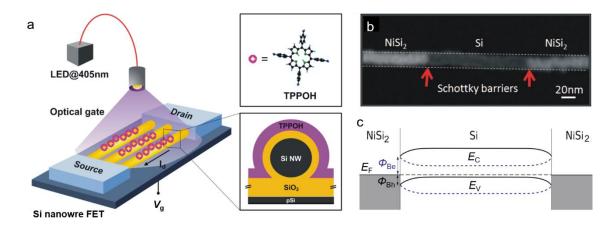

- **5.2** Schematic diagram of a hybrid light sensitive Si nanwoire FET, and SEM image of NiSi<sub>2</sub> electrode to a Si nanowire. Energy band diagram of a Schottky barrier FET. 52

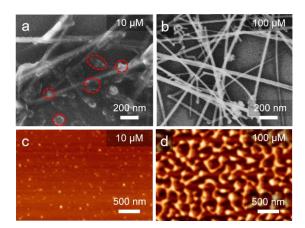

- 5.3 Surface functionalization of Si oxide surface with porphyrin film. Porphyrin coverage of nanowires depends on its concentration. Scanning electron microscopy (SEM) images of sprayed Si nanowires covered by 10  $\mu$ M and 100  $\mu$ M of the TPPOH solution. Atomic force microscope (AFM) images of porphyrin-coated SiO<sub>2</sub> surface with 10  $\mu$ M and 100  $\mu$ M of TPPOH solution. 53

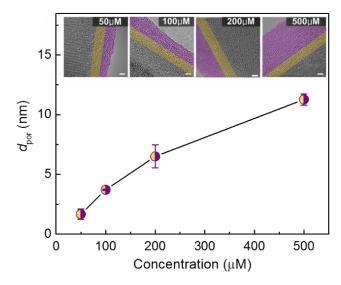

- 5.4 Plot of the thickness of porphyrin layer covering nanowires as a function of concentration. 54

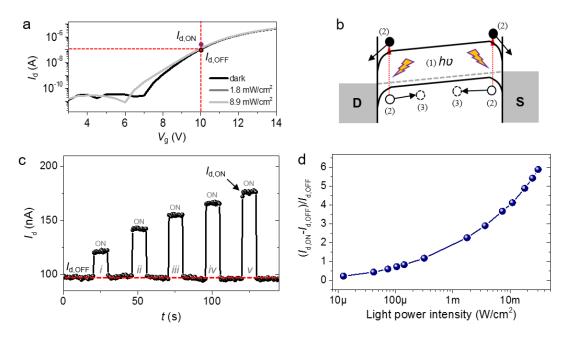

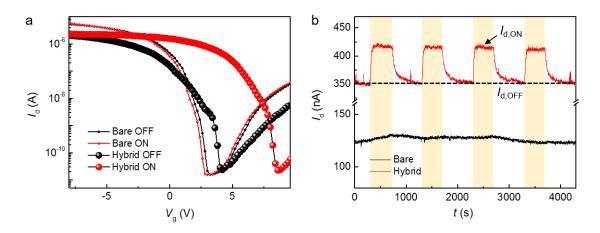

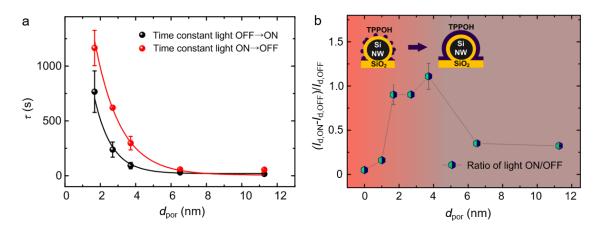

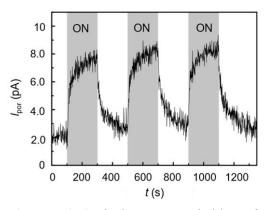

- 5.5 Light-induced Current switching characteristics of hybrid Si nanowire FETs. 55

- 5.6 Current witching dynamics and switching efficiency. 57

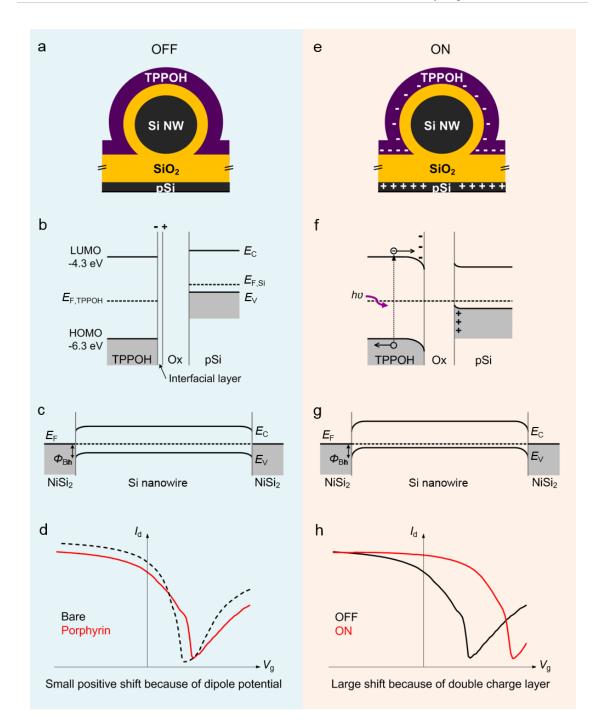

- **5.7** Current switching mechanism of porphyrin coated hybrid nanowire FETs. In the dark (OFF) state, the porphyrin film is ground state and insulating. When the light is turned on, the porphyrin behaves like a semiconductor inducing a negative charge close to the interface. 59

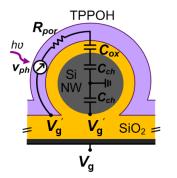

- **5.8** Schematic circuit diagram of porphyrin (TPPOH) coated hybrid nanowire FETs under light illumination. 60

- 5.9 Optical current switching of porphyrin layer without nanowires. 61

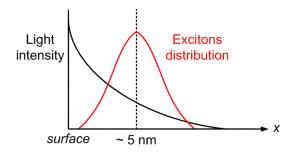

- **5.10** Expected schematic diagram of the exciton model for porphyrin-coated surface showing the light intensity as a function of the distance from the surface and the resulting expected distribution of excitons. 62

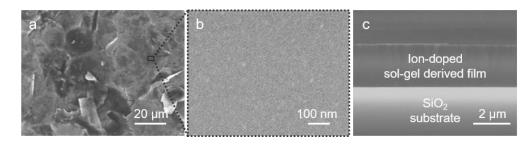

- 6.1 SEM image of the surface and the cross section morphology of the sol-gel derived film on the SiO<sub>2</sub> substrate. 71

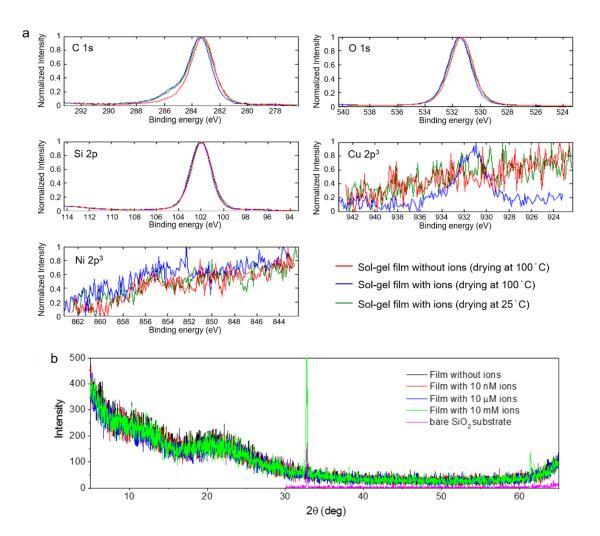

- **6.2** X-ray photoelectron spectroscopy (XPS) of the film with various drying temperature (10 mM of ion concentration), and X-ray diffraction (XRD) analysis with various doping concentration of the film (drying at 100 °C). 72

- 6.3 Chemical structure of the sol-gel derived film. 72

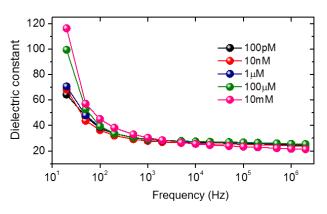

- 6.4 Extracted dielectric constant of the metal ion doped sol-gel derived film with various doping concentration versus frequency. 73

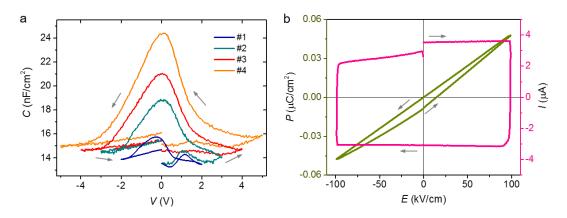

- **6.5** Polarization characteristics: C-V characteristics of a sol-gel derived film by time, and P-E hysterisis loop. 74

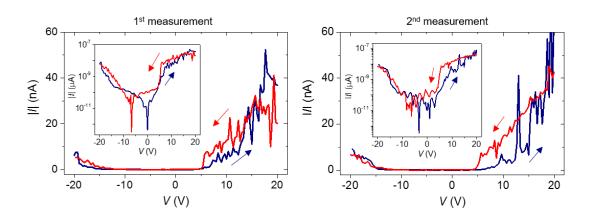

- 6.6 Electrical characteristics of the ion doped sol-gel derived silicate film. 75

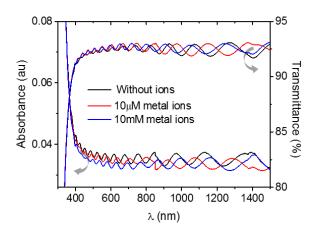

- 6.7 Absorbance and transmittance of the sol-gel derived film with various doping concentrations.76

- 7.1 Various structures of the hybrid photodetectors such as a heterojunction and an optical gate. 82

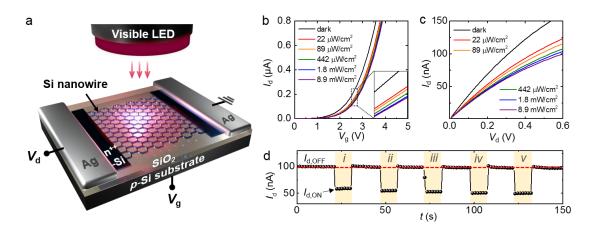

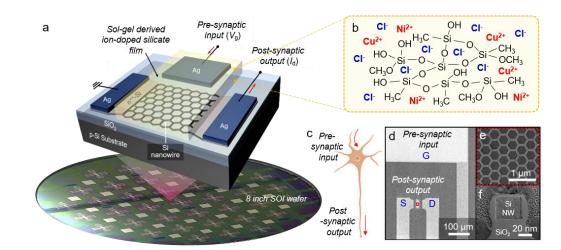

- 7.2 Structure of the hybrid Si nanowire FET devices. 84

- 7.3 Enhanced transfer characteristics of the sol-gel film-coated hybrid device compared to the bare nanowire device, and variation of subthreshold slope (SS) depending on the metal ion concentration. 85

- 7.4 Capacitive models of bare and hybrid devices. 86

- 7.5 Optical gate coupling effect of the ion-doped silicate film-coated devices. 87

- 7.6 Schematic and circuit diagrams of optoelectronic double gate effect. 88

- 7.7 Optical current switching characteristics. 89

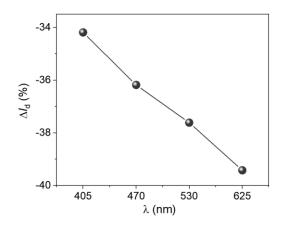

- 7.8 Wavelength dependence of light induced current change of the hybrid device. 90

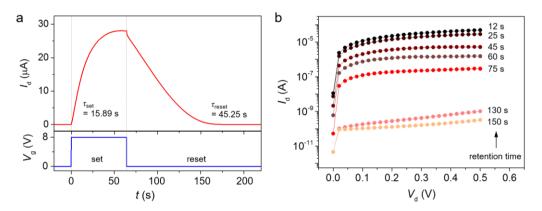

- 8.1 Structure of a Si nanowire neurotransistor. 96

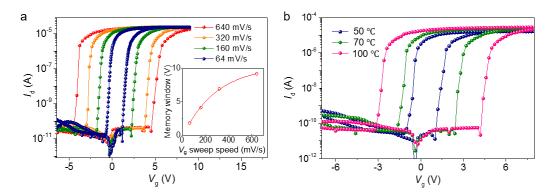

- 8.2 Tunable memory of the neurotransistors. 97

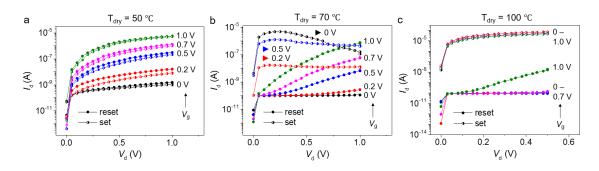

- **8.3** 1-transistor (1T) memory functionality of the sol-gel film coated Si nanowire transistors with various drying temperature: 50, 70 and 100 °C. 98

- 8.4 Set and reset time of memory. 99

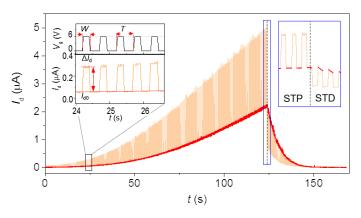

- **8.5** The post-synaptic output current  $(I_d)$  responding to pre-synaptic pulse-train  $(V_g)$  in the neurotransistor. 100

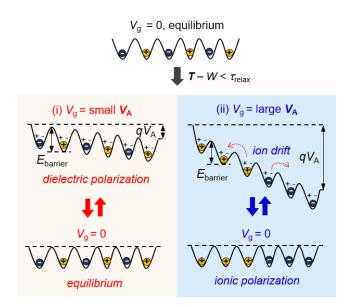

- 8.6 Neuroplasticity of neurotransistors. 101

- 8.7 A schematic diagram showing the various polarization occured in the ion-doped sol-gel silicate film through potential energy barrier when  $V_g$  is applied. 102

- 8.8 Sigmoid weight of neuron cell and neurotransistor. 103

- 8.9 History-dependent memory in the neurotransistor. 104

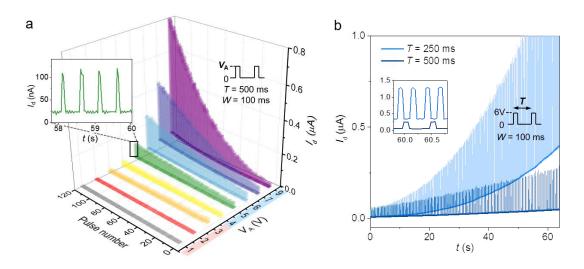

8.10 Metaplasticity of the neurotransistors. 105

8.11 Multiple outputs of the neurotransistor. 107

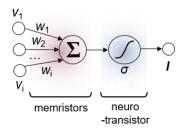

9.1 The schemetic diagram of perceptron: the simplest model of a neuron cell. 118

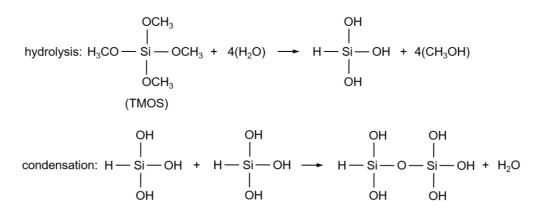

Scheme 1 Polymerization reactions (hydrolysis and condensation) of sol-gel precursor 69

### LIST OF TABLES

- 4.1 Negative photoconductance observed in different systems and its mechanism. 34

- 4.2 Experimental values of carrier life time in doped Si. 42

- 8.1 Comparison between the nanoelectronic candidates for neuromorphic computing machine. 95

- A.4 Sigmoid fitting of the output current of the neurotransistor. 123

### CHAPTER 1 INTRODUCTION

Last 50 years, silicon industry has been dramatically grown based on the needs for metaloxide-semiconductor (MOS) transistor which is a fundamental element of CPU and memory. Thanks to the development of nanotechnology including lithography and epitaxy, scaling down of the transistors opened the era of 10-nm processing (100 million of transistors per 1 mm<sup>2</sup> of a chip)<sup>1</sup>. The remarkably high integration density allows electronic devices to process a massive amount of data with high speed. The integration technology promoted the invention of *smart devices* (*e.g.*, smartphones or tablets) which can interact with users and other devices. The smart devices are changing our lifestyle and culture to more mobile and connecting. This trend has been expanded to smart system ems such as smart home, smart healthcare or smart grid.

In this circumstances, the Si-based transistors are not only used as a computing element but also operated as detecting elements interacting with the environment, for instance, chemical (bio<sup>2,3</sup> and gas<sup>4</sup>), light<sup>5,6</sup> or thermoelectric<sup>7</sup> sensors. The transistor-based sensors can be directly adaptable to electronic circuits with a wireless connection, so that detected signal could be processed ubiquitously. In the transistors, gate modulation "switches" (digital) or "amplifies" (analog) the channel current. This intrinsic property enables the various sensor applications requiring signal amplification combining with the digital process. A transistor can detect analytes using gate potential fluctuation induced by the charge of target elements. Sensor application was the evolution of transistors that converge various fields across the boundaries of biology, chemistry, and physics beyond the conventional transistor electronics. *Si nanowire*, one-dimensional Si-based nanostructured material, is verified as an attractive detector which has high sensitivity based on the large surface area-to-volume ratio and compatible diameter with nanoscale sensing targets like proteins or molecules<sup>8</sup>. Therefore, the Si nanowire field-effect transistor (FET) has emerged as a powerful sensor platform where a small amount of external electrical stimuli like charged bio- or gas molecules around the nanowires causes meaningful conductance change in the nanowire channel. To increase the sensitivity, researchers have developed molecular immobilization technique on the nanowire surface as well.

Interestingly those sensor studies involving the surface technology encouraged the birth of *hybrid nanowire transistors* that combine nanowire with organic materials to carry out distinct functionality which depends on the stimuli (*e.g.*, photodetectors). While the Si nanowire sensors treat the external molecules as a passive material which should be detected, the hybrid transistors exploit the organic molecules as an active material by forming a heterojunction which controls the gate potential of the transistor device.

The transistors as computing elements have targeted extremely high integration density by continuous downscale by Moore's law. The integration technology using conventional transistor structure has successfully improved the computing performance such as speed or memory storage using. However, the smart computing processing various environmental input signals or complex human brain tasks require a new and different paradigm of device architecture. Thus, the *hybrid device* system has an excellent capability to go beyond the conventional computing based on a functional variety of the organic materials. By combining with various functional organic/inorganic materials on the gate of a transistor, it can modulate the transistors using environmental stimuli which generates particular electric reactivity in gate material, also preserving the technological advantage of Si-based transistors.

Another important aspect is that nature inspires the stimuli-dependent hybrid system. All living creatures in nature are analog machines that actively interact with their environment based on sensing and reacting which are controlled by ionic movement at a cellular level. Regarding computing, the binary calculation of the conventional computers is different with nature. Although it would be not simple to mimic the sophistication and elegance of nature, if we need robots or computers that can substitute advanced human tasks in the near future, the machine that can emulate the natural computer, the brain, would be the best candidate which can understand our nature.

In this thesis, various gate materials from organic molecules, polymers to silicate composite and their systemic functions regarding field-effect affecting the Si nanowire transistor have been studied. In the following of introduction, **Chapter 2** discusses the basic theory of Si nanowire FET. In particular, this chapter describes how gate potential is modulating the channel conductivity using the energy band and potential diagrams, that would be the starting point to develop applications by gate engineering. **Chapter 3** covers the experimental method to fabricate the Si nanowire FETs. Also, film formation as a functional gate material is introduced. The electrical and optical characterization and spectroscopic procedure for the material analysis are followed.

**Chapter 4** investigates the optoelectronic modulation of Si nanowire FETs including unconventional negative photoconductivity (NPC). This chapter shows that the light-induced trapped electron causes unconventional conductance change by threshold voltage change. Since photoconductance is the intrinsic effect of the nanowire channel and interface area, it is fundamental to understand the conductivity change of nanowire by external stimuli (cf. light) to take a step forward towards the external gate effect.

**Chapter 5** to **Chapter 8** show various types of the external gate using the hybrid material system. In **Chapter 5**, the well-known organic material, porphyrin, is used as the outer shell of the nanowire transistor, acting as an optical gate. This chapter shows not only the optical current switching but also the possibility of optical gate modulation using pure field-effect.

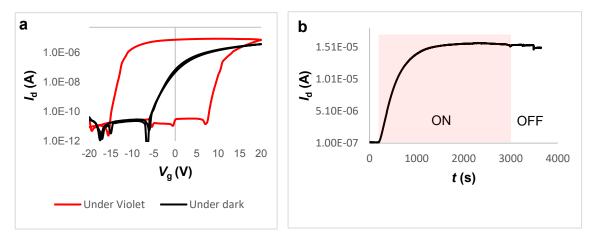

**Chapter 6** introduces the sol-gel derived composite materials for gate area. The solgel silicate film is used as a gate platform which can be doped with various small elements like ions or molecules. **Chapter 7** shows optical gate property of the sol-gel film-coated Si nanowire FETs under illumination. Interestingly, the devices show a double gate effect with a back gate which is typically shown in the FinFET. In **Chapter 8**, the sol-gel coated Si nanowire transistor shows new hardware opportunities that combine learning and memory functions within one unit cell, similar to a neuron. The device emulates the intrinsic neuronal plasticity and can perform as a computing node in a complex neural network.

Chapter 9 summarizes the thesis with the outlook for future applications.

#### References

- Loughran, J. Moore's Law 2017: an uphill battle. *Engineering and Technology* (2017). Available at: https://eandt.theiet.org/content/articles/2017/05/moore-s-law-2017-an-uphillbattle/. (Accessed: 29th November 2017)

- Shen, M. Y., Li, B. R. & Li, Y. K. Silicon nanowire field-effect-transistor based biosensors: From sensitive to ultra-sensitive. *Biosens. Bioelectron.* (2014). doi:10.1016/j.bios.2014.03.057

- Baraban, L. et al. in Nanowire Field Effect Transistors: Principles and Applications 241– 278 (Springer New York, 2014). doi:10.1007/978-1-4614-8124-9\_10

- Cao, A., Sudhölter, E. & de Smet, L. Silicon Nanowire-Based Devices for Gas-Phase Sensing. *Sensors* 14, 245–271 (2013).

- 5. Miller, D. A. B. Are optical transistors the logical next step? *Nat. Photonics* 4, 3–5 (2010).

- 6. Priolo, F., Gregorkiewicz, T., Galli, M. & Krauss, T. F. Silicon nanostructures for photonics and photovoltaics. *Nat. Nanotechnol.* **9**, 19–32 (2014).

- Choi, J., Jeon, Y., Cho, K. & Kim, S. Field-effect modulation of the thermoelectric characteristics of silicon nanowires on plastic substrates. *Nanotechnology* 27, 485401 (2016).

- 8. Cui, Y., Wei, Q., Park, H. & Lieber, C. M. Nanowire nanosensors for highly sensitive and selective detection of biological and chemical species. *Science* **293**, 1289–92 (2001).

- Yeonghwan Ahn, James Dunning, A. & Park\*, J. Scanning Photocurrent Imaging and Electronic Band Studies in Silicon Nanowire Field Effect Transistors. *Nano Lett.* (2005). doi:10.1021/NL050631X

## CHAPTER 2 THEORETICAL BACKGROUND: Hybrid gate Si nanowire field-effect transistors

Si nanowire field effect transistors (FETs) have been demonstrated as powerful building blocks for digital computing and sensing applications. Thus, the history and the current definition of Si nanowire FETs are introduced in this chapter. The analytical models of multiple gate transistors are fundamental to develop hybrid gate transistors. Therefore, the distribution of the potential in the Si nanowire, and threshold and subthreshold models in double gate transistor are presented. Finally, the physical concept of a hybrid gate induced by external stimuli is sketched for actual applications in next chapters.

### 2.1 Si nanowire field-effect transistors

To understand the birth and current state of Si nanowire field-effect transistors (FETs), it is worth noting the history of CMOS technology, since MOSFET (*metal-oxide-semiconductor* FET) is a building block of the CMOS, the backbone of the semiconductor industry. In 1965 Gordon Moore predicted the evolution of the transistor density in a chip, which is known as *Moore's law*. Remarkably, the semiconductor industry has faithfully followed the law for the last 40 years, that the number of transistors on integrated circuits has doubled every two years (Figure 2.1). The semiconductor devices have been evolved to achieve a fast circuit operation by reducing clock speed and parallel processing which can be obtained by reduced gate oxide capacitance and increased number of transistors

**Figure 2.1** Moore's law: The number of transistors on integrated circuit chips. (Data source: http://en.wikipedia.org/wiki/transistor\_count)

on a chip. In addition, smaller transistors guarantee lower leakage current by reducing the space charge region in bulk and lower power consumption. These advantages have leaded aggressive scaling down of semiconductor device components.

The integrated circuits in the initial period were built on a Si wafer. At the end of 1990, the invention of SOI (silicon-on-insulator) wafers boosted circuit performance by reducing the parasitic capacitances and enhancing charge transport. Major semiconductor companies like IBM or AMD have manufactured the memory and processor using SOI wafer. In 2010, semiconductor companies began to produce 20 nm gate length transistors, and 10 nm CMOS technology is established in 2017<sup>1</sup>.

As the dimension of the devices is reduced to sub-100nm gate length scale, the close distance between the source and the drain generates a number of parasitic effects such as short channel effects<sup>2</sup> that reduce the ability of the gate to control the channel current or random dopants fluctuation<sup>3</sup> from the enhanced atomistic effect in nanoscale devices. To overcome the short channel effect and recover the gate controllability, MOSFETs have evolved from a single planar gate to the multiple-gate structure on the SOI substrate (Figure 2.2). In 1984 the first theoretical paper of double gate (DG) MOSFET was published and showed that SCE is significantly reduced by fully depleted condition obtained by two gate electrodes<sup>4</sup>. The advantage of DG MOSFET was experimentally proven in 1989 using *Delta* (fully depleted lean-channel transistor) structure<sup>5</sup> which was

Figure 2.2 Various gate structures.

an initial model of fin-based FET (FinFET) which became main interest in transistor industry after 2000<sup>6</sup>. Further, an advanced structure like multiple independent gate FETs (MIGFET) with non-connected gates were developed<sup>7</sup>. Triple gate MOSFET has an island-like Si channel which is modulated by three sides<sup>8,9</sup>. The theoretically ideal structure is surrounding gate or gate-all-around MOSFET where the gate electrode wraps around all side of the nanowire so that dramatically suppresses short channel effect and its unit channel area is controlled by large gate electrode surface that extensively enhances gate controllability<sup>10</sup>. In the silicon industrial sector, surrounded cylindrical structure, in which diameter of Si channel is below 10 nm, is called Si nanowire MOSFET. The downscaling of the transistor enables to fabricate a MOSFET without forming p-njunctions at source/drain and the channel region, so-called 'junctionless' nanowire transistor that is turned off by full depletion of nanowire originating from the work function difference between the channel material and the gate electrode<sup>11</sup>. The main purpose of the Si nanowire FET in the industry is to suppress the parasitic effect induced by downscaling, and to enhance the functionality and convenience in the manufacturing of integrated circuits.

In most fields, however, it is called Si nanowire FETs, when the nanowire diameter is in the nanoscale (< 100 or 1000 nm). Bottom-up synthesized nanostructures have been separately studied in the field of physics and material science. Their interest is to

**Figure 2.3** The conversion of the Si nanowire FETs to Si nanowire sensor. Figure is adopted from the ref.<sup>14</sup>.

understand the physics in the nanosized materials and to search for novel functionalities using the distinct low dimensional characteristics like quantum effects or ballistic transport. In 2000, Charles M. Lieber published the transistor characteristics of the synthesized p- and n-type Si nanowire using chemical vapor deposition (CVD) method with 70-150 nm-thick diameter<sup>12</sup>. Further,

his group fabricated  $n^+$ -p-n bipolar transistor and CMOS inverter which is modulated by back gate<sup>13</sup>. The nanowire diameter was reduced to 20-50 nm range. In 2001, his group presented a historic result, the first Si nanowire biosensor detecting pH and protein<sup>14</sup> (Figure 2.3). This study has brought up explosive stream of the Si nanowire-based *ion-sensitive* sensor researches<sup>15</sup> which are still ongoing process<sup>16–18</sup>. For ion detection, the solid metal back gate can be substituted with a liquid gate connected to the metal reference electrode, namely ion sensitive FET (ISFET). Most of Si nanowire FET sensors follow the universal principle that channel current is fluctuated by dielectric capacitance change induced from electric charge of detection targets.

It is notable that there are several essential aspects of previous studies about Si nanowire FETs;

- (i) Although *bottom-up* transistors have the potential to reduce the cost of fabrication, *top-down* devices are more reliable in electrical performance based on the wellestablished CMOS process steps on an SOI substrate. However, bottom-up grown nanowires are easily printable on any substrate from SiO<sub>2</sub> to flexible organic films or grids, which is not easy to be performed using the top-down way. Therefore, both regimes are used these days depending on the target application and spec.

- (ii) The surface effect becomes critical in the nanowire FETs. The nano-sized material has more surface per unit volume that generate parasitic effects like interfacial trapping or scattering which should be overcome to obtain the best transistor

operation. On the other hand, people exploit the surface effect to enhance the performance of the transistor, for instance, gate all around structure or surface functionalization for sensing applications.

### 2.2 The field-effect – gate-induced potential distribution

Figure 2.4 Structural evolution of functional gate field-effect transistors.

In the field effect transistor, the variable voltage applied to the *gate* controls the effective cross-sectional area (*e.g.*, depletion or inversion region) of the conducting channel in the nanowire. Because of junctions between channel and source/drain, the current flow is generally blocked in an equilibrium state ( $V_g = 0$ ). However, gate potential ( $V_g$ ) changes conduction- and valence band bending which modulate the charge carrier distribution on each band. Enough voltage induces the mobile charge carriers which can flow between *source* and *drain*. Therefore, the surface potential modulation of the Si channel determines the current flows and the switching functionality (strong inversion) decided by the threshold voltage ( $V_{th}$ ).

In the CMOS industry, the back (substrate) gate is not used as a primary gate controller. However, using back gate has an advantage when one creates a 'manual' front gate to obtain complex gate controllability keeping the typical transistor behavior. Figure 2.4 shows several variations of the back-gate FETs. Opened front channel area can be combined with any material from the metal, organic to liquid. For instance, the ISFET for ion sensing is the liquid gate combination and double or tri-gate FinFET structure is one of the combined structure. If functional materials which have particular characteristics

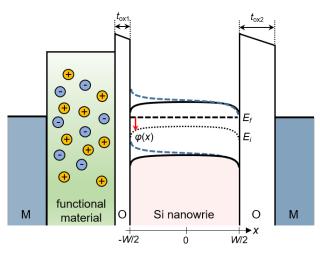

**Figure 2.5** Energy band diagram of hybrid Si nanowire FETs with double gate (left: front gate, right: back gate). (M: metal, O: oxide layer,  $t_{ox}$ : thickness of the oxide layer, W: thickness of the Si nanowire,  $E_{f}$ : Fermi energy,  $E_{i}$ : intrinsic Fermi energy)

with additional stimuli, are combined with the nanowire, functional hybrid FET can be created for tailored applications. Figure 2.5 shows the band bending of Si nanowire can be modulated by the internal electrical dynamics of the functional material which is a result of the external stimuli like voltage, temperature, light or chemical reactions etc.

Although the gate materials could be varied, the surface potential on the oxide interfacing the nanowire determines the transistor behavior in the devices using the field-effect scheme. The surface potential is induced from Poisson's equation:

$$\frac{d^2\varphi}{dx^2} = \frac{q}{\varepsilon_{si}} n_i e^{q\varphi/kT}$$

(2.1)

where q is electric charge,  $\varepsilon_{si}$  is permittivity of silicon,  $n_i$  is intrinsic carrier density and  $\varphi$  is the potential at any point x in the Si nanowire relative to  $E_i$ . The boundary condition at -W/2 and W/2 are different;

$$\varepsilon_{ox} \frac{V_g - \Phi_{ms1} - \varphi_{s1}}{t_{ox1}} = \varepsilon_{si} \frac{d\varphi}{dx} |_{x=W/2} = -\varepsilon_{si} \vec{E}_1$$

(2.2)

$$\varepsilon_{ox} \frac{V_g - \Phi_{ms2} - \varphi_{s2}}{t_{ox2}} = \varepsilon_{Si} \frac{d\varphi}{dx} |_{x = -W/2} = -\varepsilon_{Si} \vec{E}_2$$

(2.3)

where  $\Phi_{ms1}$  and  $\Phi_{ms2}$  are work function difference between the gates and Si nanowire (here the functional material is not considered),  $\varphi_{s1}$  and  $\varphi_{s2}$  are left and right oxide interfacial potential respectively,  $\vec{E}_1$  and  $\vec{E}_2$  are the electric field at the left and the right boundary.

By integrating eqs. (2.1) with the symmetry boundary condition  $\frac{d\varphi}{dx}|_{x=0} = 0$ , we can obtain

$$\frac{d\varphi}{dx} = -\sqrt{\frac{2kTn_i}{\varepsilon_{si}} \left(e^{\frac{q\varphi}{kT}} - e^{\frac{q\varphi_0}{kT}}\right)}$$

(2.4)

where  $\varphi_0$  is potential when  $d\varphi/dx = 0$ .

Integrating (2.4) we can obtain the potential distribution as a function of  $x^{19}$

$$\varphi(x) - \varphi_0 = -\frac{2kT}{q} \cdot \ln\left[\cos\left(\sqrt{\frac{q^2 n_i}{2\varepsilon_{si}kT}}e^{\frac{q\varphi_0}{2kT}} \cdot x\right)\right].$$

(2.5)

Similarly, in asymmetric boundary condition the symmetry point is moved to  $x_0$  (cf.  $\frac{d\varphi}{dx}|_{x=x_0} = 0$ ). The potential can be obtained from eqs. (2.5)

$$\varphi(x) - \varphi_0 = -\frac{2kT}{q} \cdot \ln\left[\cos\left(\sqrt{\frac{q^2 n_i}{2\varepsilon_{si}kT}}e^{\frac{q\varphi_0}{2kT}} \cdot (x - x_0)\right)\right]$$

(2.6)

where  $\varphi_0 \equiv \varphi(x = x_0)$ .

With very low gate voltages are applied, then it can be approximated as  $\frac{d\varphi}{dx} \approx -\vec{E}_0$  which is constant field when the charge inversion  $(e^{\frac{q\varphi}{kT}})$  is negligibly small. In this case the internal field is directly calculated by  $\varphi_{s1} - \varphi_{s2} \approx -W\vec{E}_0$ . Appling these into eqs (2.2) and (2.3), one obtains

$$\vec{E}_0 = \frac{\Phi_{ms1} - \Phi_{ms2}}{W + \frac{\varepsilon_{si}}{\varepsilon_{ox}}(t_{ox1} + t_{ox2})}$$

(2.7)

and

$$\varphi(x) = \frac{2kT}{q} \cdot ln \left[ \frac{\sqrt{\frac{\varepsilon_{si}}{2kT} \cdot n_i} \vec{E}_0}{\frac{sinh\left(\frac{q\vec{E}_0(x-x_0)}{2kT}\right)}} \right].$$

(2.8)

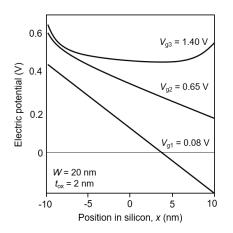

**Figure 2.6** Electric potential  $\varphi$  as a function of position in silicon.  $V_{g1}$ - $V_{g3}$  are equally applied on each gate. Left and right gates are  $n^+$  and  $p^+$  polysilicon respectively.<sup>20</sup>

Based on the equations above, the potential distribution of the nanowire with the same  $V_g$  applied on two different gate electrodes, is shown in Figure 2.6 which is adapted from the analytic study of double gate MOSFET<sup>20</sup>. When the gate bias is big enough, the potential in nanowire has distinct distribution and comparably uniform potential is applied overall nanowire channel which is not shown in the planar MOSFETs. If the gate bias is small, the potential is more affected by work function differences between the gate and the Si channel that makes a linear distribution. This information gives a hint of understanding the charge distribution in the nanowire which is

dependent on potential, when multiple gate structure is formed.

One of the important parameters that characterize a switching performance of the transistors is the threshold voltage ( $V_{\text{th}}$ ). The threshold voltage is classically defined by

$$V_{th} = \Phi_{ms} + 2\varphi_f - \frac{Q_d}{C_{ox}} - \frac{Q_i}{C_{ox}}$$

(2.9)

where  $\varphi_f$  is the difference between the Fermi level and the intrinsic Fermi level of Si,  $Q_d$  is the depletion region charge,  $Q_i$  is the oxide and interfacial charge and  $C_{ox}$  is gate capacitance. In nanowire devices. However, with low doped ultra-thin nanowire structure, inversion in the channel could be limited when the surface potential is at  $2\varphi_f$ . Therefore, eqs (2.9) should be modified to

$$V_{th} = \Phi_{ms} + 2\varphi_f - \frac{Q_d}{C_{ox}} - \frac{Q_i}{C_{ox}} + V_{inv}$$

(2.10)

where  $V_{inv}$  is the additional surface potential needed to induce the inversion charge in the nanowire channel.  $V_{inv}$  increases with narrower channel width and lower doping concentration<sup>21</sup>. Similarly, the surface charge in the hybrid devices strongly affects the threshold voltage. Any surface charge change, *e.g.* surface functionalization or stimuli-

induced charge generation in the hybrid gate materials, enhance or suppress  $V_{\text{th}}$  depending on the sign of the charge. Therefore, eqs (2.9) could be modified with surface charge  $Q_{\text{s}}$ :

$$V_{th} = \Phi_{ms} + 2\varphi_f - \frac{Q_d}{C_{ox}} - \frac{Q_i}{C_{ox}} - \frac{Q_s}{C_{ox}}.$$

(2.11)

Most of the sensor applications using the Si nanowire transistor use  $V_{\text{th}}$  shift by ionic charge change on the Si nanowire surface. The dynamics of charge formulation on the Si nanowire surface is directly applied as the surface potential of the nanowire, which must be considered to design hybrid gate devices. In addition, distinct fin-nanostructure and multiple gate modulation are able to generate a channel separation that two separated inversion charge is formed in a nanowire, which will be discussed in **Chapter 7**.

#### 2.3 Subthreshold region: a fingerprint of the gate signal change

Many studies have demonstrated the important role of the subthreshold region of the transfer characteristic, specifically for the detection of the surface charge fluctuation with the highest percentage of conductance change<sup>22,23</sup>. The reason is the subthreshold region current changed exponentially by gate potential change. The exponential increase of current allows the transistor to have (i) switching functionality from off to on current with low power consumption and (ii) amplification of current in this range. Therefore, this sensitive region shows the various information of electric properties of gate area through the slop, the shape (*e.g.* hump), or the off current level etc.

In the classical MOSFET, the subthreshold slop (SS) is represented by

$$SS = \ln 10 \cdot \frac{\partial V_g}{\partial \ln I_d} \cong \frac{kT}{q} \cdot \ln 10 \cdot \left(1 + \frac{C_d + C_{it}}{C_{ox}}\right)$$

(2.12)

where  $C_d$  is depletion capacitance and  $C_{it}$  is interface trap capacitance. With normal MOSFET with fully depleted thin channel structure with a top gate, the variation of depletion charge by voltage fluctuation is zero, so that  $C_d = 0$ . If the interfacial trapped charge is zero with a perfect process step,

$$SS \rightarrow \frac{kT}{q} \cdot \ln 10 = 60 \text{ mV/dec.}$$

(2.13)

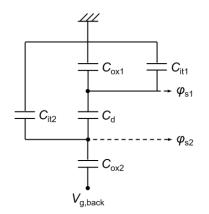

However, with multiple gate modulation, the back interfacial trap density is not negligible and all capacitance values at front and back should be considered. Figure 2.7 shows a

capacitance model of back gate control with fixed front gate potential. In this case, SS is induced from the eqs.  $(2.14)^{24}$ :

$$\frac{\partial \ln I_d}{\partial V_{g,back}} = \frac{1}{I_d} \cdot \frac{\partial I_d}{\partial \varphi_{s2}} \cdot \frac{\partial \varphi_{s2}}{\partial V_{g,back}}$$

(2.14)

$$\frac{\partial \varphi_{s2}}{\partial V_{g,back}} = \frac{C_{ox}}{C_{ox2} + C_{it2} + \frac{C_d \cdot (C_{it1} + C_{ox1})}{C_{it,front} + C_{ox1} + C_d}}$$

(2.15)

**Figure 2.7** Capacitance model of MOSFET structure with back gate control.

$$\frac{1}{I_d} \cdot \frac{\partial I_d}{\partial \varphi_{s2}} = \frac{kT}{q} - \frac{\frac{1}{t_{si}} \left[ 1 - \frac{C_d}{C_d + C_{it1} + C_{ox1}} \right]}{\left( \frac{\varphi_{s2} - \varphi_{s1}}{W} + \frac{qN_dW}{2\varepsilon_{si}} \right)} \quad (2.16)$$

where  $\varphi_{s1}$  and  $\varphi_{s2}$  are front and back surface potential of the nanowire channel, *W* is the thickness of the nanowire channel  $\varepsilon_{si}$  is the dielectric constanct of the Si and  $N_d$  is the doping concentration. Eqs. (2.16) shows that SS is related to the back and front gate potential difference ( $\varphi_{s2} - \varphi_{s1}$ ). The simplest front and back gate potential distribution is shown in Figure 2.8 which is redrawn from the previous study<sup>24</sup>. For back gate modulated devices, the subthreshold current is strongly affected by front gate potential. As front gate potential increases, SS and off current level also increases because high

**Figure 2.8** Variation of front and back gate potential distribution (1-4, left) and their corresponding transfer characteristics (right).

front gate potential can generate weak inversion in all over the nanowire channel. Therefore, from the subthreshold characteristics, an unknown surface potential could be estimated. This technique is very useful especially for stimulus-induced potential variation in hybrid gate.

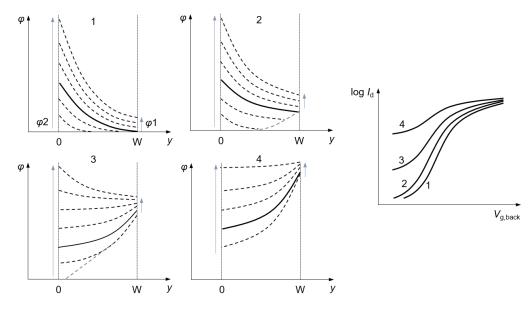

#### 2.4 *Hybrid electronic elements with the stimuli-induced gate*

Figure 2.9 Various circuit elements for the hybrid gate.

Previous sections show how the surface potential applied from multiple(double) gates affects the potential distribution in the nanowire, threshold voltage and subthreshold slope. Metal gate without any potential loss was a good starting point to understand the double or multiple gate system in previous sections. The purpose of hybrid electronic devices study is to generate distinct functionality which is induced by both internal electronic property and external stimuli, keeping the transistor characteristics. Since a lot of functional materials are available for the hybrid gate, it is convenient to classify the functional materials as circuit elements. Figure 2.9 shows the simplified transistor circuit with various hybrid gates. Insulators have been used to form a high-k stack on a transistor to guarantee enough capacitance level even in the strong downscaling. However, using semiconducting or memristive materials for gate modulation would be a new approach to build a single electronic circuit element. Apart from the work function difference between the gate material and the Si nanowire, external stimuli like light or voltage pulses would generate front gate potential and unique dynamics with specific time span in the functional materials. Many existing memory devices are using additional material (e.g. high- $\kappa$  to ferroelectric) on the top of the MOSFET performing 0 or 1 states. However, unique dynamics of various functional materials have the capability to be applied for analog circuits or unconventional application beyond CMOS. In this system, Si nanowire is modulated by physics in the gate materials whether the front gate bias is applied or not.

#### References

- Auth, C. *et al.* A 10nm high performance and low-power CMOS technology featuring 3 <sup>rd</sup> generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects. in *2017 IEEE International Electron Devices Meeting (IEDM)* 29.1.1-29.1.4 (IEEE, 2017). doi:10.1109/IEDM.2017.8268472

- Chaudhry, A. & Kumar, M. J. Controlling Short-Channel Effects in Deep-Submicron SOI MOSFETs for Improved Reliability: A Review. *IEEE Trans. Device Mater. Reliab.* 4, 99– 109 (2004).

- Asenov, A., Brown, A. R., Davies, J. H., Kaya, S. & Slavcheva, G. Simulation of intrinsic parameter fluctuations in decananometer and nanometer-scale MOSFETs. *IEEE Trans. Electron Devices* 50, 1837–1852 (2003).

- 4. Sekigawa, T. & Hayashi, Y. Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate. *Solid. State. Electron.* **27**, 827–828 (1984).

- Hisamoto, D., Kaga, T., Kawamoto, Y. & Takeda, E. A fully depleted lean-channel transistor (DELTA)-a novel vertical ultra thin SOI MOSFET. in *International Technical Digest on Electron Devices Meeting* 833–836 (IEEE, 1989). doi:10.1109/IEDM.1989.74182

- 6. Chenming Hu *et al.* FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. *IEEE Trans. Electron Devices* **47**, 2320–2325 (2000).

- Mathew, L. *et al.* CMOS Vertical Multiple Independent Gate Field Effect Transistor (MIGFET). in 2004 IEEE International SOI Conference (IEEE Cat. No.04CH37573) 187– 189 (IEEE, 2004). doi:10.1109/SOI.2004.1391610

- 8. Jong-Tae Park & Colinge, J.-P. Multiple-gate SOI MOSFETs: device design guidelines. *IEEE Trans. Electron Devices* **49**, 2222–2229 (2002).

- 9. Colinge, J.-P. Multiple-gate SOI MOSFETs. Solid. State. Electron. 48, 897–905 (2004).

- 10. Iwai, H. et al. Si nanowire FET and its modeling. Sci. China Inf. Sci. 54, 1004–1011 (2011).

- 11. Colinge, J.-P. *et al.* Nanowire transistors without junctions. *Nat. Nanotechnol.* **5**, 225–229 (2010).

- Yi Cui, Xiangfeng Duan, Jiangtao Hu, and & Lieber\*, C. M. Doping and Electrical Transport in Silicon Nanowires. (2000). doi:10.1021/JP0009305

- 13. Cui, Y., Lieber, C. M. & Bawendi, M. G. Functional nanoscale electronic devices assembled using silicon nanowire building blocks. *Science* **291**, 851–3 (2001).

- 14. Cui, Y., Wei, Q., Park, H. & Lieber, C. M. Nanowire nanosensors for highly sensitive and selective detection of biological and chemical species. *Science* **293**, 1289–92 (2001).

- 15. Patolsky, F. & Lieber, C. M. Nanowire nanosensors. Mater. Today 8, 20-28 (2005).

- 16. Zhang, G.-J. & Ning, Y. Silicon nanowire biosensor and its applications in disease

diagnostics: A review. Anal. Chim. Acta 749, 1-15 (2012).

- Zhang, A., Zheng, G. & Lieber, C. M. Nanowire Field-Effect Transistor Sensors. in 255– 275 (Springer, Cham, 2016). doi:10.1007/978-3-319-41981-7 10

- Dai, X., Zhou, W., Gao, T., Liu, J. & Lieber, C. M. Three-dimensional mapping and regulation of action potential propagation in nanoelectronics-innervated tissues. *Nat. Nanotechnol.* 11, 776–782 (2016).

- 19. Yuan Taur. An analytical solution to a double-gate MOSFET with undoped body. *IEEE Electron Device Lett.* **21**, 245–247 (2000).

- 20. Taur, Y. Analytic solutions of charge and capacitance in symmetric and asymmetric doublegate MOSFETs. *IEEE Trans. Electron Devices* **48**, 2861–2869 (2001).

- Tahara, Y. & Omura, Y. Empirical Quantitative Modeling of Threshold Voltage of Sub-50nm Double-Gate Silicon-on-Insulator Metal–Oxide–Semiconductor Field-Effect Transistor. *Jpn. J. Appl. Phys.* 45, 3074–3078 (2006).

- 22. Gao, X. P. A., Zheng, G. & Lieber, C. M. Subthreshold regime has the optimal sensitivity for nanowire FET biosensors. *Nano Lett.* **10**, 547–52 (2010).

- 23. Zörgiebel, F. M. *et al.* Schottky barrier-based silicon nanowire pH sensor with live sensitivity control. *Nano Res.* **7**, 263–271 (2014).

- 24. Wouters, D. J., Colinge, J.-P. & Maes, H. E. Subthreshold slope in thin-film SOI MOSFETs. *IEEE Trans. Electron Devices* **37**, 2022–2033 (1990).

# CHAPTER 3 EXPERIMENTAL METHODS

In this chapter, the experimental methods will be discussed. Two main device fabrication scheme, bottom-up and top-down, will be introduced with details. Also, the hybrid gate formation by various film coating method depending on the device functionality and the material characteristics will be shown. Finally, procedure of electrical and film analysis will be described.

# 3.1 Fabrication of Si nanowire field-effect transistors

#### 3.1.1 Bottom-up scheme: Schottky-junction Si nanowire FETs

The content of this part is mainly based upon my published article<sup>1</sup>.

(i) Si wafer preparation with gold catalysts: A clean Si (100) wafer was prepared using piranha and organic cleaning using acetone and isopropanol, and hydroxyl groups on the surface were activated using air plasma for 20 sec. Poly (diallyl dimethylammonium) chloride (PDDA) was used as stabilizing agent of gold nanoparticles (GNPs) that acts as a catalyst of nanowire growth. PDDA solution (0.5 vol% PDDA and 5 mM NaCl in distilled water) was treated on the Si wafer and 19 nm GNPs were attached to PDDA. O<sub>2</sub> plasma removed PDDA linking that makes equivalent distribution of Au NPs and prevents aggregation of Au NPs.

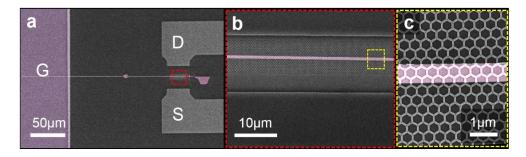

**Figure 3.1** Microscopic images of Schottky-barrier Si nanowire FETs. (a) The conformation of the Ni electrode on high density nanowires. (b) Inter- electrode spacing of devices are varied from 6 to 12  $\mu$ m. (c) NiSi<sub>2</sub> formation as Schottky barrier of a nanowire. The brighter part indicates N–Si phases and the dark part of the nanowire is the Si channel. (d) The thickness of the thermally grown oxide wrapping nanowires is around 5 nm.

(ii) Growth of Si nanowire: Si nanowires were synthesized in chemical vapor deposition (CVD) chamber heated at 400°C using silane (SiH<sub>4</sub>) gas and hydrogen (H<sub>2</sub>) gas as precursors with an inner pressure of 65 mbar for 45 min<sup>2</sup>. The length of grown Si nanowires was around 20-40  $\mu$ m and the diameter was around 20 nm depending on the size of Au nanoparticles.

(iii) Fabrication of the transistor chip: The contact printing method was used to align the synthesized nanowires in a common direction<sup>3</sup>. The nanowire-growth wafer was put on a SiO<sub>2</sub> wafer for Schottky-barrier FETs with vertical pressure of 100-200 N/cm<sup>2</sup> and moved with constant velocity that provides friction force between nanowires and the SiO<sub>2</sub> wafer. Nanowires are covalently bonded on the interface (Figure 3.1(b)). Dry thermal oxidation was employed to form a thermal oxide layer of 5 nm (Figure 3.1(d)). For the fabrication of Schottky barrier FETs, metal source and drain pads were patterned on the Si nanowires embedded SiO<sub>2</sub> wafer using photolithography process (Figure 3.1(a)). Finally, the sample was annealed at 450 °C in a H<sub>2</sub>/N<sub>2</sub> atmosphere for 1 min. Thus nickel diffused along Si nanowires and nickel silicide was formed. Figure 3.1(c) shows welldefined phases of nickel silicide fractions within the single nanowire produced by means of axial diffusion of nickel into the nanowire body<sup>4,5</sup>. The FET devices, consisting of arrays of parallel nanowires, provide reduced device-to-device variability and high source-drain current level as well as high transconductance<sup>5</sup>.

This work was conducted by Dr. S. Pregl at NamLab, Dresden. This scheme is used for the organic molecular coated Si nanowire FETs described in **Chapter 5**.

#### 3.1.2 Top-down scheme: n- and p-doped Si nanowire FETs

**Figure 3.2** The steps of the top-down nanowire device fabrication. A doped SOI wafer (i, ii and iv) is patterned using (iii) photolithography and (v) electron beam lithography depending on the pattern size. After (vi) thermal oxide formation and (vii) metal deposition for the electrodes, (viii)the devices are passivated except nanowire and electrode contact area.

The content of this part is mainly based upon my published article<sup>6</sup>.

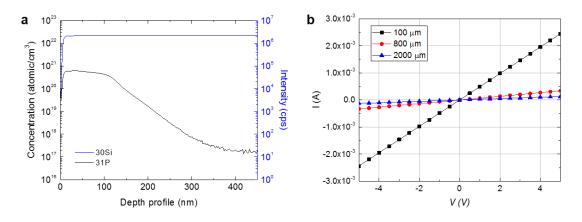

Si nanowire FETs were fabricated on three 8-inch SOI wafers that consist of a 40 nmthick top-Si layer (Boron,  $10^{16}$  cm<sup>-3</sup>), a 400 nm-thick buried oxide layer and the 725 µmthick p-type Si substrate (Figure 3.2(i)). To implant phosphorus ions in the top Si layer, the 20 nm SiO<sub>2</sub> buffer layer was deposited using plasma enhanced CVD (PECVD) at 300 °C. After that, phosphorus ions are implanted with an energy of 15 kEV and the concentrations of dopants were  $10^{13}$  cm<sup>-2</sup> for  $10^{18}$  cm<sup>-3</sup> and  $10^{14}$  cm<sup>-2</sup> for  $10^{19}$  cm<sup>-3</sup> samples (Figure 3.2(ii)). Rapid thermal annealing followed, at 1,000 °C for 20s in N<sub>2</sub> atmosphere to activate dopants. Finally, the buffer oxide layer was stripped in 1:100 dHF for 2~3 min. Consequently, one of the wafers has a boron concentration of  $10^{16}$  cm<sup>-3</sup>, respectively.

An active area including the channel, the source and the drain region was defined for electrical isolation of devices using photolithography and inductively coupled plasma reactive ion etching (ICP-RIE) (Figure 3.2(iii)). The source and the drain region were

**Figure 3.3** Structure of honeycomb Si nanowire FETs. (b) Microscopic image of Si nanowire devices with source and drain transmission line. Scanning electron microscopy (SEM) image of (c) Si nanowire channel area and (d) honeycomb structure of nanowires. (e) Transmission electron microscopy (TEM) image of cross-section of nanowire and thermal SiO<sub>2</sub> layer.

formed using phosphorus ion implantation with a concentration of  $5 \times 10^{20}$  cm<sup>-3</sup>, and dopant activation followed, using the same recipe above (Figure 3.2(iv)). )). The source and drain area was heavily doped to form ohmic contact (See **Appendix I**). A honeycomb nanowire was patterned on the channel region using electron beam lithography and etched with ICP-RIE (Figure 3.2(v)). The pattern width of the nanowire was 50 nm and the length of the nanowire was 8 µm. (Figure 3.3 (b) and (c)) The final height of nanowire was 30 nm. (Figure 3.3(d)) A 5-nm thick gate oxide layer was grown on the nanowire using a wet oxidation furnace at 850 °C for passivation and post-processing (Figure 3.2(vi) and 3.3(d)). To form the source and the drain electron-beam evaporator, and liftoff process has followed the deposition steps (Figure 3.2(vii), 3.3(a) and (b)). Finally, the whole wafer area except the nanowire channel region and metal contact pad was passivated with 2 µm thick SU-8 epoxy-based photoresist to protect the long transmission line from undesired contamination (Figure 3.2(viii)).

Figure 3.3 shows the fabricated honeycomb Si nanowire FETs. The Si channel area was heavily doped ( $10^{18}$  and  $10^{19}$  cm<sup>-3</sup>) with phosphorus to modify the channel conduction properties from normal inversion mode *n*-type FETs to accumulation mode *n*-type FETs. Therefore, device is normally in an on-state at gate bias  $V_g = 0$  V, which is advantageous for low power sensor applications. As a nanowire channel region, a honeycomb structure was designed (see Figure 3.3(c)) in order to obtain higher signal to noise ratio and higher current stability at the subthreshold voltage regime <sup>7,8</sup>. The source and drain area was heavily doped ( $10^{20}$  cm<sup>-3</sup>) to form ohmic contact with the metal transmission line (Figure 3.3(a)).

The fabrication process of honeycomb structured Si nanowire FET is done by Dr. T. Rim and Dr. K.Kim at NINT of POSTECH in Republic of Korea. This scheme is used for the photoconductance of Si nanowire FETs in **Chapter 4** and for the ion-doped sol-gel film coated Si nanowire FETs in **Chapter 7 and 8**.

## 3.1.3 Top-down scheme: Top gate fabrication

**Figure 3.4** SEM images of the top electrode configuration on a honeycomb nanowire device. (a) Top view of the gate electrode on the nanowire FET device with source and drain electrodes. (b) Top gate electrode covers the part of nanowire area. (c) The transparent gate electrode on the honeycomb nanowire structure.

The content of this part is mainly based upon my published article<sup>6</sup>.

Top gate electrodes were fabricated by patterning Poly(methyl methacrylate) (PMMA) 950k using electron beam lithography, followed by a lift-off process with sputtered platinum (Figure 3.4). The resist was spin-coated on the honeycomb nanowire devices at a speed of 1000 rpm for 60 s, resulting in a 120 nm thick PMMA film. The top electrode pattern was written by electron beam. Then, the samples were immersed into the H<sub>2</sub>O:IPA(isopropanol) (1:3) development solution for 3 min and cleaned in isopropanol. After, a thin chromium adhesion layer (3 nm) was thermally evaporated and a 30 nm platinum layer was sputtered on it. The chip was immersed into acetone for 3 min and treated in ultrasonication for 1-2 min to remove the residual PMMA layer. This protocol allowed connection of the gate electrode to the honeycomb nanowires with a thin Pt electrode with a width of 650 nm which covers approx. 8% of the nanowire area (Figure 3.4(b)). Finally, the sample was annealed in 200 °C to reduce the contact resistance.

This scheme is used for the photoconductance of Si nanowire FETs in Chapter 4.

# 3.2 Functional hybrid gate film formation

### 3.2.1 Organic film formation

#### Photochromic molecular film

The content of this part is mainly based upon my published article<sup>1</sup>.

Nanowire FET chip (in the **section 3.1.1**) is cleaned first with acetone, and then with isopropanol for 5 min respectively to remove organic contaminant. As a final cleaning step, ethanol is used for 5 min. This step helps to regularly spread the ethanol based solution over the chip.

45 µl of 5,10,15,20-Tetrakis(4-hydroxyphenyl)-21H,23H-porphine (Sigma Aldrich) solution based on ethanol and distilled water (95:5) was dropped on a chip with constant area with 1x2 cm<sup>2</sup>. The concentration is changed from 10 to 500 µM. Solvent was evaporated overnight (~12 hrs) with high humidity that promotes the formation of a conformal porphyrin layer on all over the surface. Therefore, the porphyrin layer is formed on the 5 nm of thermal oxide on the Si nanowire. Depending on the concentration, the thickness of the porphyrin layer is varied from 2 nm to 12 nm that is discussed in **Chapter 5**.

#### **Organic semiconductor film**

The nanowire chips (in the **section 3.1.2**) was cleaned with acetone, isopropanol and ethanol around 5 minutes respectively to remove the organic contaminations on the chips. After this process, the sample was rinsed with the deionized water. The chip was dried using nitrogen gas and baked in vacuum oven at 100°C for 15 minutes to remove the water completely.

Electron transporting copolymer, Poly-{[N,N'-bis(2-octyldodecyl)-naphthalene-1,4,5,8-bis-(dicarboximide)-2,6-diyl]-alt-5,5'-(2,2'-bithiophene)} (P(NDI2OD-T2), synthesized by IPF Dresden) was dissolved in trichloroethylene (TCE) solvent with a concentration of 7g/L. The mixture was stirred using magnetic hot plate stirrer at 50°C for 1 hour, then the solution was kept in ultrasonic bath for 15 minutes and shaken by vortex mixer for 15 minutes. Well mixed solution was filtered using 400 nm pore size filter. The resulting solution was spin-coated with an angular speed of 2000 rpm during 60 seconds. The polymer coated sample was annealed using 110 °C hot plate for 1 hour to eliminate any remaining solvent and to produce a uniform film.

The film formation method in this section is used for the organic molecular coated Si nanowire FETs described in **Chapter 5** and **Appendix A.3**.

### 3.2.2 Hybrid silicate sol-gel film formation

Firstly, 2.0 x 2.0 cm<sup>2</sup>-size nanowire FET chip (in the **section 3.1.2**) was cleaned with acetone, isopropanol and deionized water for 3 minutes to remove existing organic contaminants. Air plasma cleansing was applied to the cleaned chip for 5 seconds to form ultra-hydrophilic surface which guarantees a better adhesion with sol-gel derived film.

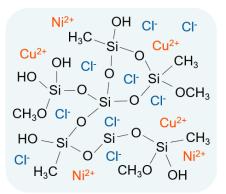

1.7 mg of Nikel(II) choloride hexahydrate (Cl<sub>2</sub>Ni·6H<sub>2</sub>O) (Sigma Aldrich) and 2.4 mg of Copper(II) chloride dehydrate (Cl<sub>2</sub>Cu·2H<sub>2</sub>O) (Sigma Aldrich) were mixed in 467 µl deionized water. 900 µl of Tetramethyl orthosilicate (TMOS) (Sigma Aldrich), 600 µl of Trimethoxymethylsilane (MTMS) (Sigma Aldrich) and 33 µl of 0.1 M HCl were added to metal salt solution. The total concentration of metal ions ([M]<sub>tot</sub>) indicates the sum of equal concentration of two metal salts in the final mixed solvent. ([M]<sub>tot</sub> = [Cu<sup>2+</sup>] + [Ni<sup>2+</sup>] = 10 mM, [Cu<sup>2+</sup>] = [Ni<sup>2+</sup>] = 5 mM). Final solvent is filtered by 200 nm pore-size filter to remove unwanted huge particles. 400 µl of the metal ion-sol was spin-coated on the cleaned FET chip with 7000 rpm in 60 sec. The sol-coated chip was dried in a vacuum oven under various temperature from 25°C to 100°C (depending on applications) for 24 hours to get a uniform gel-formation.

This scheme is used for the ion-doped sol-gel film coated Si nanowire FETs described in **Chapter 6, 7 and 8**.

## 3.3 Electrical characterization of FETs

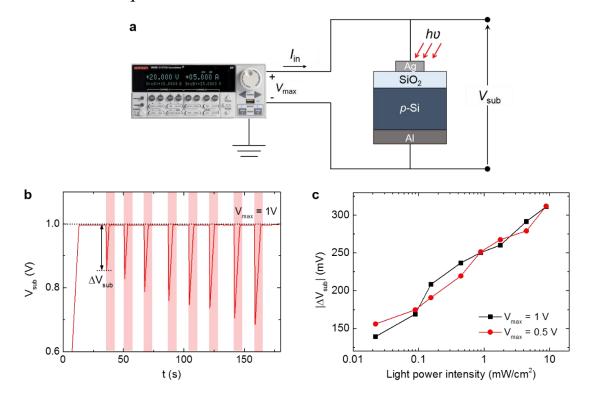

#### 3.3.1 Photocurrent measurement

A 4-channel light emitting diode (LED) driver (DC-4100, Thorlabs) which includes 4 visible LEDs ( $\lambda = 405$  nm, 470 nm, 530 nm and 625 nm) was used as a visible light source. The controller of DC-4100 controlled the power intensity of light illumination and selected the wavelength. The LED driver was connected to the collimator through liquid waveguide to illuminate the target device area with equivalent light power. The collimator was installed on the hand-made metal dark box with 5 cm-height. Therefore,

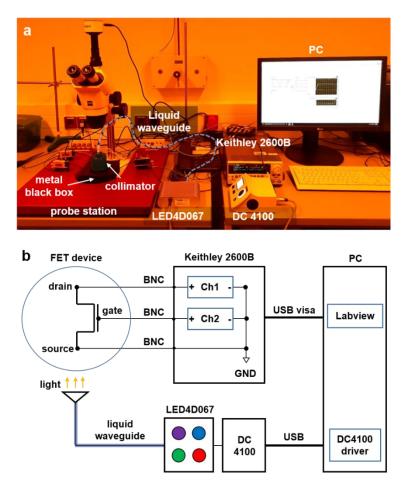

Figure 3.5 (a) Photocurrent measurement setup. (b) block diagram of the measurement setup.

the distance between the light source and the FET sample was fixed as 5 cm. (see Figure 3.5) The bias generation and current measurement of FET devices were performed using Keithley 2600B (source meter in Figure 3.5) at room temperature. The source meter was controlled by manually programed LabView program. This measurement setup is used in **Chapter 4, 5 and 7**.

#### 3.3.2 Electrical measurement

#### I-V measurement

The electrodes of the devices including field effect transistors or any patterned film are connected to tungsten needles of the micro-manipulators. The voltage and current supply and the current flowing through the devices were measured with Keithley 2604B controlled by Labview program (see the Keithely 2600B connection setup of Figure 3.5(b)). This measurement scheme is used for **Chapter 4, 5, 7 and 8**.

#### **Pulse measurement**

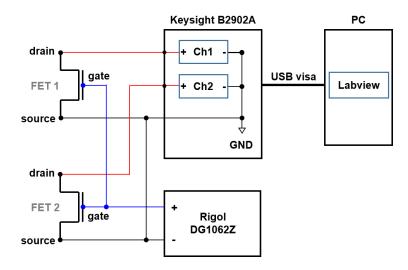

Figure 3.6 Block diagram of pulse measurement setup.

In order to characterize the plasticity behavior of the devices, Keysight B2902A was used as source meter to read the output currents under the modulation of the input pulses generated by the pulse generator, Rigol DG1062Z (Figure 3.6). The current from multiple devices was measured using Labview program. Square pulses are used as input signal with various pulse width and period. This pulse measurement is used in **Chapter 8**.

## 3.4 Film analysis

In this section, the methods used for the analysis of hybrid sol-gel derived film (described in **section 3.2.2**) and film preparation steps for analysis will be introduced. The tailored modulation of hybrid functional devices relies on the physical and chemical properties of the film. Since the sol-gel film doped with metal ions is an uncommon material for present electronic applications, the careful analysis from various angles were essential to verify the quality of film formation on the surface and to determine the functional purpose of the hybrid devices. The result of the analysis in this section will be discussed in **Chapter 6**.

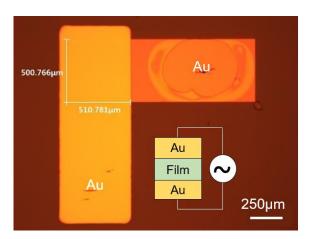

#### 3.4.1 Capacitance analysis

To measure the capacitance of the sol-gel film, the gold electrode was formed using thermal evaporation. Using a metal shadow mask, patterns with large area  $(0.5 \times 1.0 \text{ mm}^2)$

of electrodes were deposited on the cleaned SiO<sub>2</sub> wafer with 50 nm thickness (Figure 3.7). The large electrodes are necessary to increase the capacitive signal which has to be measurable by commercial LCR meters. The patterned wafer is cleaned with isopropanol and activated with ozone generator. Then, the sol-gel derived film was coated on the wafer in accordance with the section 3.2.2. Second one, top electrode was

**Figure 3.7** Microscopic image of the patterned gold electrodes for capacitance measurement. Overlapped area is used to extract capacitance.

deposited on the film following same method above.

The bottom and top electrode were connected to LCR meter (Agilent E4980A) which is shown in the schematic diagram in Figure 3.6 and the capacitance of the film between two electrodes was measured at various frequencies.

#### 3.4.2 Spectroscopic analysis

To verify the chemical structure including crystallinity and composition of the hybrid solgel film in the **section 3.2.2**, X-ray diffraction (XRD) and X-ray photoelectron spectroscopy (XPS) analysis were performed. The film is formed on the SiO<sub>2</sub> wafer surface (see the **section 3.2.2**) dried in different temperature such as 25 °C and 100 °C with and without the present of metal salts. To obtain the absorption spectra of the film, UV-Vis spectroscopy was used. The absorption spectra of the film is distinct from the solution state, because the degree of freedom of molecules is reduced by interference from neighboring molecules in solid state. For UV-vis spectroscopy which exploits transmission of the light through the sample, the transparent glass substrate is used instead of the SiO<sub>2</sub> wafer. The film formation was following the **section 3.2.2**. The sol-gel film samples with and without metal salts were compared.

XRD and UV-Vis spectroscopy were performed in POSTECH, Korea and XPS is analyzed at IFW Dresden, Germany.

#### References

- 1. Baek, E. *et al.* Optoelectronic switching of nanowire-based hybrid organic/oxide/ semiconductor field-effect transistors. *Nano Res.* **8**, 1229–1240 (2015).

- Weber, W. M. *et al.* Silicon nanowires: catalytic growth and electrical characterization. *Phys. status solidi* 243, 3340–3345 (2006).

- 3. Weber, W. M. *et al.* Silicon-Nanowire Transistors with Intruded Nickel-Silicide Contacts. *Nano Lett.* **6**, 2660–2666 (2006).

- Léonard, F. & Talin, A. A. Electrical contacts to one- and two-dimensional nanomaterials. *Nat. Nanotechnol.* 6, 773–783 (2011).

- 5. Pregl, S. *et al.* Parallel arrays of Schottky barrier nanowire field effect transistors: Nanoscopic effects for macroscopic current output. *Nano Res.* **6**, 381–388 (2013).

- Baek, E. *et al.* Negative Photoconductance in Heavily Doped Si Nanowire Field-Effect Transistors. *Nano Lett.* 17, 6727–6734 (2017).

- 7. Rim, T. *et al.* Improved Electrical Characteristics of Honeycomb Nanowire ISFETs. *IEEE Electron Device Lett.* **34**, 1059–1061 (2013).

- Kim, K. *et al.* Suspended honeycomb nanowire ISFETs for improved stiction-free performance. *Nanotechnology* 25, 345501 (2014).

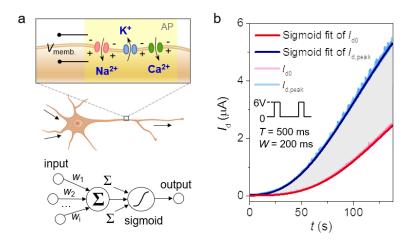

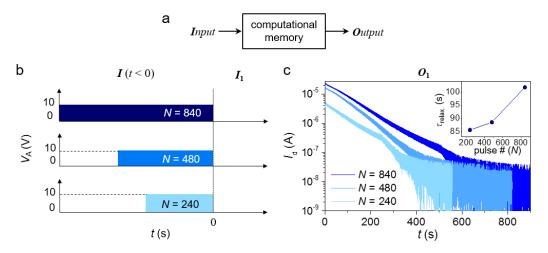

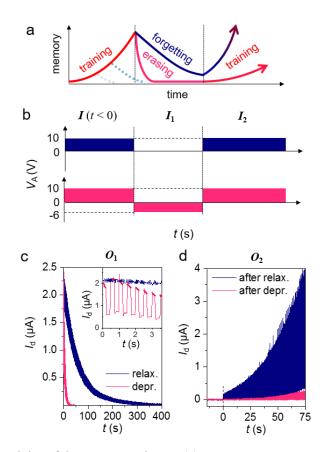

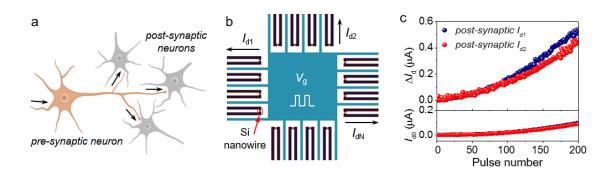

# CHAPTER 4 INTRINSIC OPTICAL GATE: Negative Photoconductance in Si nanowire FETs