Technische Universität Dresden

### pinMOS Memory:

## A novel, diode-based organic memory device

Yichu Zheng, M. E.

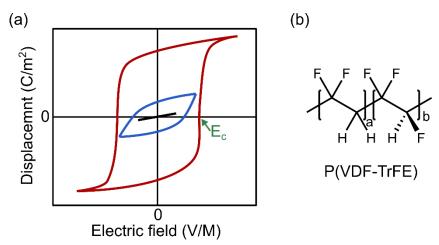

der Fakultät Elektrotechnik und Informationstechnik der Technischen Universität Dresden

zur Erlangung des akademischen Grades

### Doktoringenieur

(Dr.-Ing.)

genehmigte Dissertation

Vorsitzender: Prof. Dr.-Ing. Prof. Hubert Lakner Gutachter: Prof. Dr. rer. nat. Stefan Mannsfeld Gutachter: Prof. Dr. Koen Vandewal Tag der Einreichung: 24.10.2019 Tag der Verteidigung: 07.08.2020

## Abstract

A novel, non-volatile, organic capacitive memory device called p-i-n-metal-oxide-semiconductor (pinMOS) memory is demonstrated with multiple-bit storage that can be programmed and read out electrically and optically. The diode-based architecture simplifies the fabrication process, and makes further optimizations easy, and might even inspire new derived capacitive memory devices. Furthermore, this innovative pinMOS memory device features local charge up of an integrated capacitance rather than of an extra floating gate.

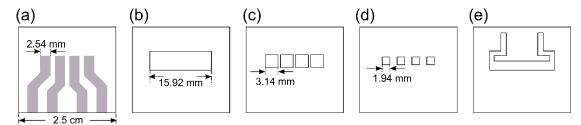

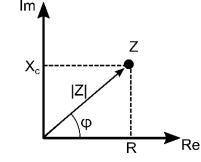

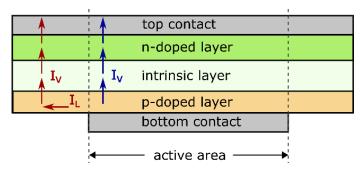

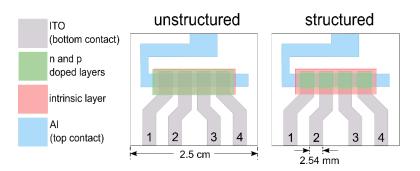

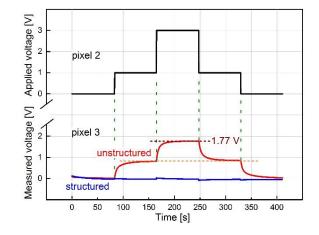

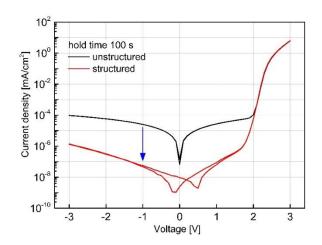

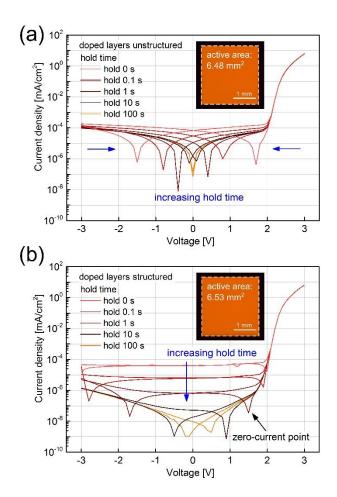

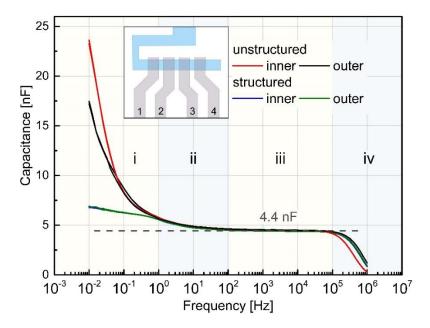

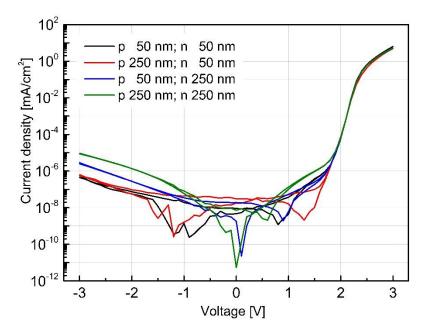

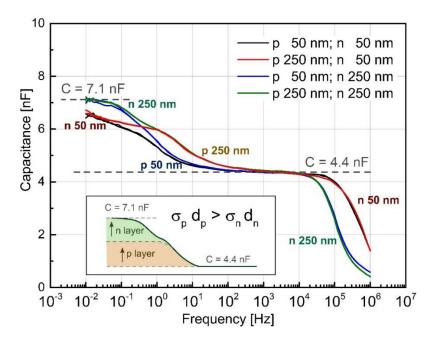

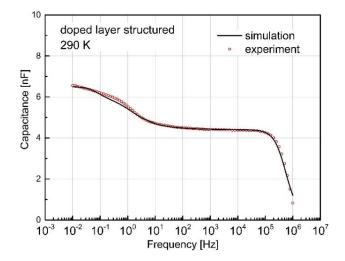

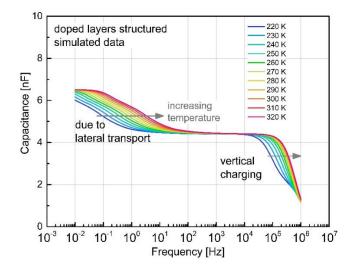

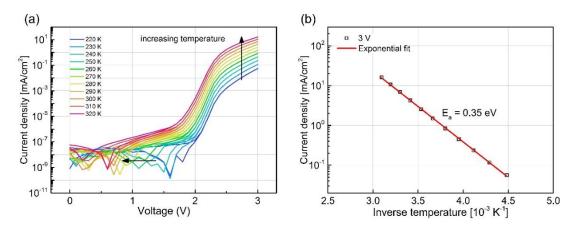

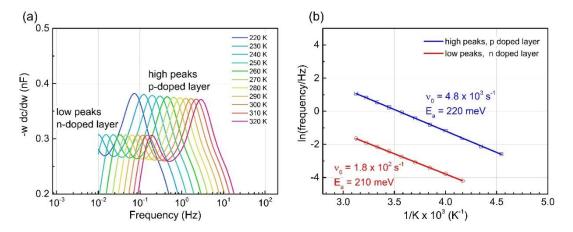

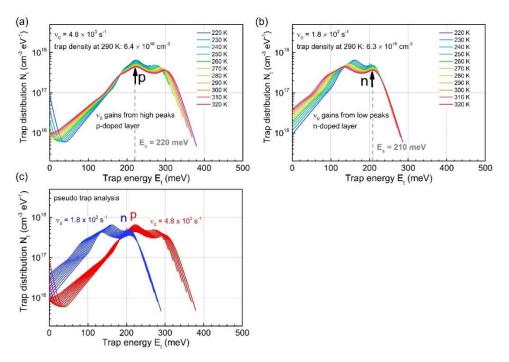

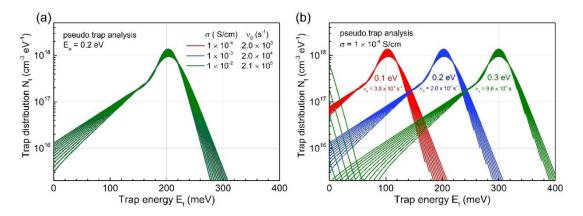

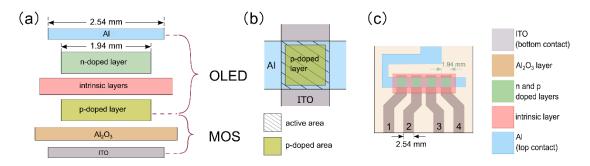

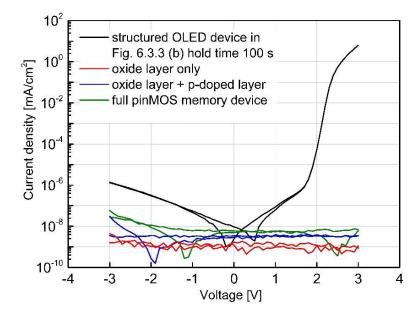

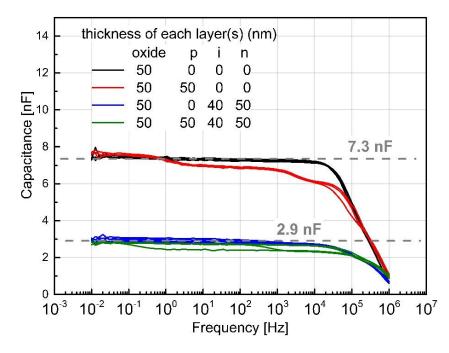

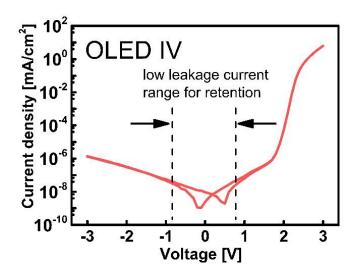

Before the device can perform as desired, the leakage current due to the lateral charge up of the doped layers outside the active area needs to be suppressed. Therefore, in this thesis, lateral charging effects in organic light-emitting diodes (OLEDs) are studied first. By comparing the results from differently structured devices, the presence of centimeter-scale lateral current flows in the n-doped and p-doped layers is shown, which results in undesirable capacitance increases and thus extra leakage currents. Such lateral charging can be controlled via structuring the doped layers, leading to extremely low steady-state leakage currents in the OLED (here 10<sup>-7</sup> mA/cm<sup>2</sup> at -1 V). It is shown that these lateral currents can be utilized to extract the conductivity as well as the activation energy of each doped layer when modeled with an RC circuit model.

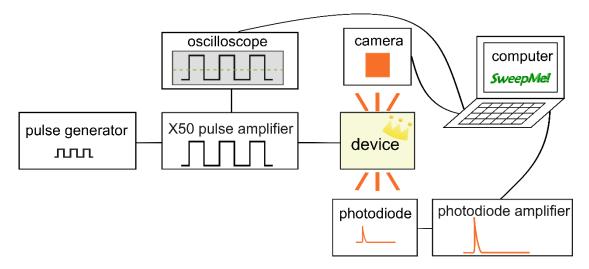

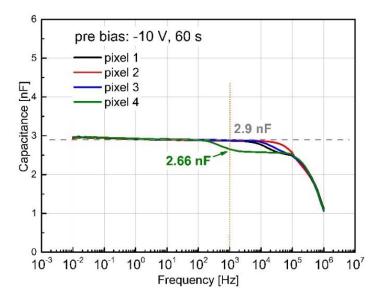

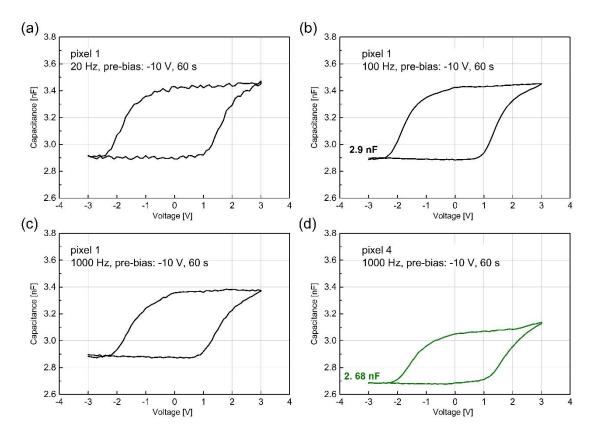

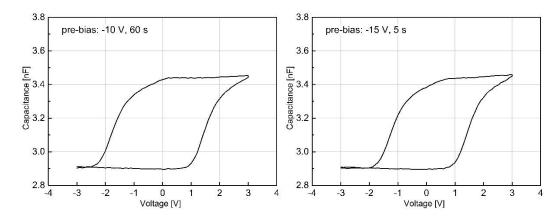

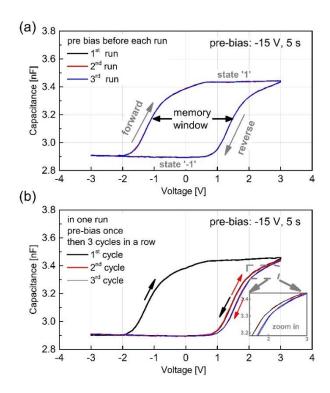

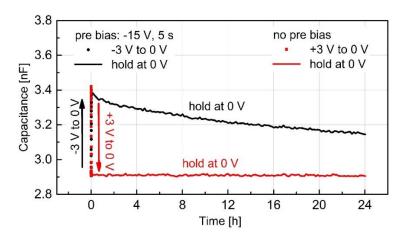

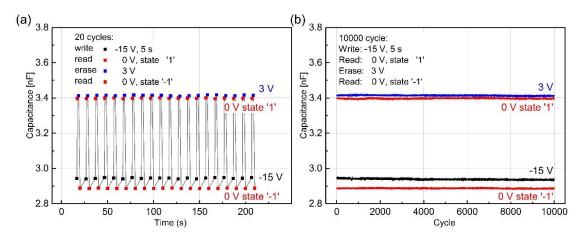

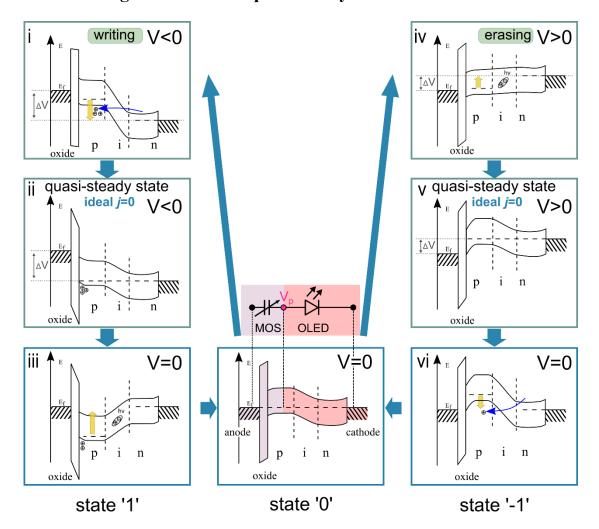

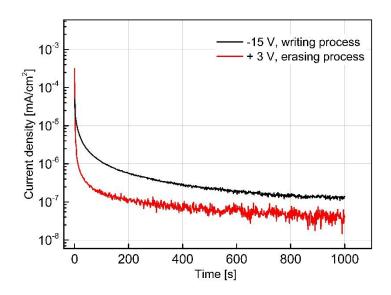

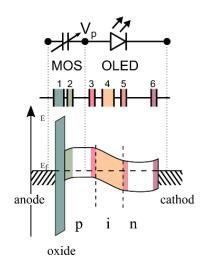

Secondly, pinMOS memory devices that are based on the diode with structured doped layers are investigated. The memory behavior, which is demonstrated as capacitance switching for electrical signals, and light emission for optical signals, can be tuned either by the applied voltage or ultraviolet light illumination, respectively. The working mechanism is explained by the existence of quasi steady-states as well as the width variation of space charge zones. The pinMOS memory shows excellent repeatability, an endurance of more than 10<sup>4</sup> write-read-erase-read cycles, and currently already over 24 h retention time. Furthermore, an early-stage investigation on emulating synaptic plasticity reveals the potential of pinMOS memory for applications in neuromorphic computing. Overall, the results indicate that pinMOS memory in principle is promising for a variety of future applications in both electronic and photonic circuits. A detailed understanding of this new concept of memory device, for which this thesis lays an important foundation, is necessary to proceed with further enhancements.

## Zusammenfassung

Es wird ein neuartiges, organisches kapazitives Speicherelement demonstriert, das p-i-n-Metalloxid-Halbleiter (pinMOS) Speicher genannt wird und eine Mehrfachbitspeicherung besitzt, die elektrisch und optisch programmiert und ausgelesen werden kann. Die auf einer Diode basierende Architektur vereinfacht den Herstellungsprozess sowie die weitere Optimierung und könnte sogar Inspiration für neue kapazitive Speichermedien sein. Darüber hinaus basiert dieses innovative pinMOS Speicherelement auf der lokalen Aufladung einer integrierten Kapazität und nicht auf einem zusätzlichem "Floating Gate".

Bevor das Speicherelement wie gewünscht funktioniert, muss der Leckstrom, der durch die laterale Aufladung der dotierten Schichten außerhalb des aktiven Bereichs verursacht wird, unterdrückt werden. Deshalb werden in dieser Arbeit zuerst die lateralen Aufladungseffekte in organischen Leuchtdioden (OLEDs) untersucht. Beim Vergleich verschiedener Device-Strukturen wird die Existenz von lateralen Stromflüssen im Zentimeterbereich in den n- und p-dotierten Schichten gezeigt, was zu einer unerwünschten erhöhten Kapazität und folglich einem höheren Leckstrom führt. Diese laterale Aufladung kann durch die Strukturierung der dotierten Schichten kontrolliert werden, was zu extrem geringen Gleichgewichtsleckströmen in den OLEDs (10<sup>-7</sup> mA/cm<sup>2</sup> bei -1 V) resultiert. Es wird auch gezeigt, dass die lateralen Ströme genutzt werden können um die spezifische Leitfähigkeit sowie die Aktivierungsenergie der einzelnen dotierten Schichten zu extrahieren, wenn diese mit einem RC-Modell modelliert werden.

Im zweiten Teil werden pinMOS Speicherelemente, die auf der Diode mit strukturierten dotierten Schichten basieren, untersucht. Das Speicherverhalten, dass durch Kapazitätsschaltung für elektrische Signale und als Lichtemission für optische Signale gezeigt wird, kann entweder durch die angelegte Spannung, beziehungsweise durch die Belichtung mit ultraviolettem Licht eingestellt werden. Die Wirkungsweise wird durch die Existenz quasistatischer Gleichgewichte sowie durch die Größenänderung der Raumladungszonen erklärt. Der pinMOS Speicher zeigt eine hervorragende Wiederholbarkeit, eine Beständigkeit über mehr als 10<sup>4</sup> Schreiben-Lesen-Löschen-Lesen Zyklen und aktuell schon eine Retentionszeit von über 24 h. Weiterhin offenbaren erste Versuche in der Nachahmung von Neuronaler Plastizität das Potenzial von pinMOS Speichern für Anwendungen im "Neuromorphic Computing". Insgesamt deuten die Ergebnisse an, dass pinMOS Speicher prinzipiell vielversprechend für eine Vielzahl von zukünftigen Anwendungen in elektronischen und photonischen Schaltkreisen ist. Ein tiefgreifendes Verständnis von diesem Konzept neuartiger Speicherelemente, für das diese Arbeit eine wichtige Grundlage bildet, ist notwendig, um weitere Verbesserungen zu entwickeln.

# Contents

| 1 | Introduction                                                                                                                                                                        | 1                          |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2 | Fundamentals of organic semiconductors                                                                                                                                              | 5                          |

|   | <ul> <li>2.1 Electronic states of a molecule</li> <li>2.1.1 Atomic orbitals and molecular orbitals</li> <li>2.1.2 Solid states</li> <li>2.1.3 Singlet and triplet states</li> </ul> | 5<br>9                     |

|   | <ul><li>2.2 Charge transport</li></ul>                                                                                                                                              | 13                         |

|   | <ul><li>2.3 Charge injection</li></ul>                                                                                                                                              | 17                         |

|   | 2.4 Doping                                                                                                                                                                          | 22                         |

| 3 | Organic junctions and devices                                                                                                                                                       | 25                         |

|   | <ul> <li>3.1 Metal-semiconductor junction</li></ul>                                                                                                                                 | 25<br>27<br>29<br>31<br>31 |

| 4 | Organic non-volatile memory devices                                                                                                                                                 | 35                         |

|   | 4.1 Basic concepts                                                                                                                                                                  | 35                         |

|   | <ul> <li>4.2 Organic resistive memory devices</li></ul>                                                                                                                             | 38<br>38                   |

|   | <ul> <li>4.3 Organic field-effect transistor and memory devices based thereon</li></ul>                                                                                             | 41<br>43                   |

|   | 4.4 Organic ferroelectric memory devices                                             | 46  |

|---|--------------------------------------------------------------------------------------|-----|

|   | 4.4.1 Ferroelectric capacitor memory                                                 | 47  |

|   | 4.4.2 Ferroelectric transistor memory                                                |     |

|   | 4.4.3 Ferroelectric diode memory                                                     |     |

| 5 | Experimental methods                                                                 | 53  |

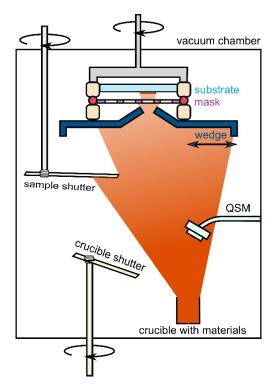

|   | 5.1 Device fabrication                                                               | 53  |

|   | 5.2 Device characterization                                                          | 55  |

|   | 5.3 Materials                                                                        | 57  |

| 6 | Lateral current flow in semiconductor devices having crossbar electrodes             | 61  |

|   | 6.1 Introduction                                                                     | 61  |

|   | 6.2 Device architecture                                                              | 62  |

|   | 6.3 Characteristics comparison between unstructured and structured devices           | 63  |

|   | 6.3.1 Charging measurement                                                           | 63  |

|   | 6.3.2 Current-voltage characteristics                                                |     |

|   | 6.3.3 Capacitance-frequency characteristics                                          |     |

|   | 6.4 Influence of conductivity of doped layers                                        |     |

|   | 6.4.1 Dependence on doped layers thickness                                           |     |

|   | 6.4.2 Dependence on temperature                                                      |     |

|   | 6.5 Lateral charging simulation                                                      |     |

|   | <ul><li>6.5.1 Analytical description.</li><li>6.5.2 RC circuit simulation.</li></ul> |     |

|   | 6.5.3 Parameters for doped layers gained by simulation                               |     |

|   |                                                                                      |     |

|   | 6.6 Pseudo trap analysis                                                             |     |

|   | 6.6.1 The pseudo trap density of states determination                                |     |

|   | 6.6.2 The pseudo trap analysis under simulated identical conditions                  |     |

|   | 6.7 Summary                                                                          | 85  |

| 7 | The pinMOS memory: novel diode-capacitor memory with multiple-bit storag             | e87 |

|   | 7.1 Introduction                                                                     |     |

|   | 7.2 Device architecture                                                              |     |

|   | 7.2.1 Dependence on layout and pixel                                                 | 89  |

|   | 7.2.2 Fundamental memory behavior characterization                                   |     |

|   | 7.3 Working mechanism                                                                | 96  |

|   | 7.3.1 Working mechanism of quasi-steady states                                       |     |

|   | 7.3.2 Working mechanism of dynamic states                                            | 101 |

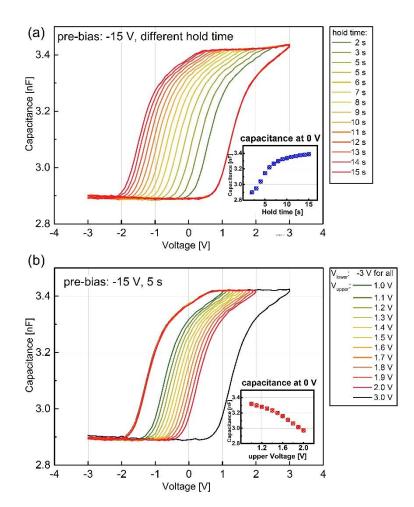

|   | 7.4 Tunability of the memory effect                                                  | 105 |

|                   |                       | 7.4.1                         | Operation parameters                              |     |  |  |  |

|-------------------|-----------------------|-------------------------------|---------------------------------------------------|-----|--|--|--|

|                   |                       | 7.4.2                         | Photoinduced tunability                           | 108 |  |  |  |

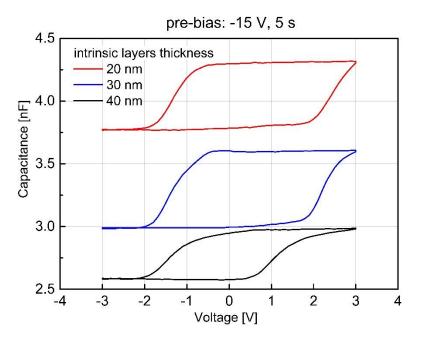

|                   |                       | 7.4.3                         | Intrinsic layer thickness                         | 110 |  |  |  |

|                   | 7.5                   | Poter                         | ntial in neuromorphic computing application       | 111 |  |  |  |

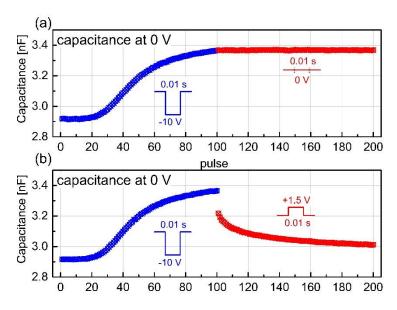

|                   |                       | 7.5.1                         | Extracting capacitance at 0 V sequentially        | 112 |  |  |  |

|                   |                       | 7.5.2                         | Mimicking the long-term plasticity (LTP) behavior | 113 |  |  |  |

|                   | 7.6                   | Sum                           | mary                                              | 114 |  |  |  |

| 8                 | Op                    | toelec                        | tronic properties of pinMOS memory                | 117 |  |  |  |

|                   | 8.1                   | duction                       | 117                                               |     |  |  |  |

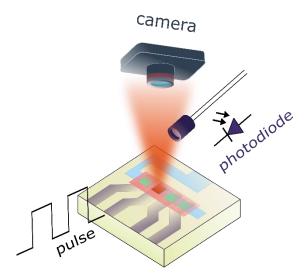

|                   | 8.2 Measurement setup |                               |                                                   |     |  |  |  |

|                   | 8.3                   | IOS memory emission intensity | 118                                               |     |  |  |  |

|                   | 8.4                   | Pulse                         | e characteristics and device brightness           | 119 |  |  |  |

|                   | 8.5                   | Conc                          | elusion                                           | 124 |  |  |  |

| 9                 | Co                    | nclusi                        | on                                                | 125 |  |  |  |

| Bi                | iblio                 | graph                         | ıy                                                | 129 |  |  |  |

| Li                | List of Figures       |                               |                                                   |     |  |  |  |

| List of Tables151 |                       |                               |                                                   |     |  |  |  |

| Li                | ist of                | f Abbi                        | reviations                                        | 153 |  |  |  |

| Pı                | ublic                 | cation                        | s and Conference                                  | 157 |  |  |  |

| A                 | ckno                  | owledg                        | gment                                             | 159 |  |  |  |

## **Chapter 1**

## Introduction

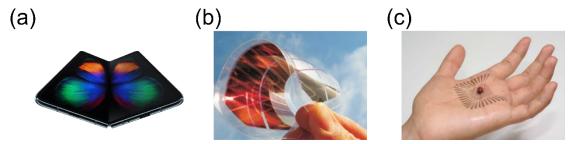

We are living in a more and more electronic world where electronics like computers and phones, accompanied by modern communication techniques like internet, occupy our daily life. Electronics based on inorganic materials, i.e., silicon, are the main body of commercial applications owing to their advanced fabrication techniques and remarkable device performance [1]. However, siliconbased devices cannot meet the emerging application requirements on flexibility and optical transparency, indicating that inorganic electronics are not appropriate candidates for the future tendency in foldable electronics or flexible electronics [2]. Furthermore, the expensive and energyintensive fabrication process limits the further development of silicon-based devices. Therefore, organic electronics that involve semiconductors, dielectrics, electrolytes, ferroelectrics, and even biological organisms, have been intensely investigated in the last decade. Their potential to make ultra-lightweight, low-cost, large area, printable electronics promises several commercial applications including electronic papers, imagers, sensors, organic light-emitting diode (OLED) drivers, etc [3-8]. Some of them can already reach the real consumer market, especially OLED based color displays that widely used in TV, computer, phone with long lifetime and high efficiency. Other organic electronics like organic field-effect transistors (OFETs) and organic solar cells (OSCs) are on the way to commercialization, while more exotic devices such as organic memories and lasers are studied with high expectations.

Figure 2.1.1: Photographs of (a) phone with foldable OLED display, (b) flexible OSCs, and (c) skin electronics based on stretchable transistor array. Pictures are taken from [9-11].

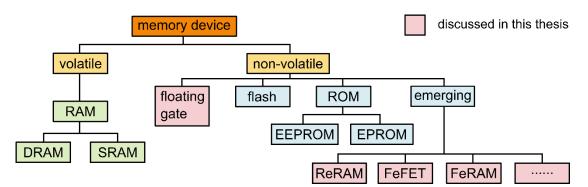

Among major devices now being investigated in this large and ever-growing field, the demand for organic memory devices, which are data storage devices, increases along with the advance of digital information technology. Three memory technologies dominate the market: silicon-based solid state dynamic random access memory (DRAM) and flash memory, and inorganic magnetic hard disk

drives [12], [13]. Emerging technologies such as resistive random access memory (ReRAM), single transistor-based memory comprising a floating gate layer as charge-storage (trapping) layer, ferroelectric memory including ferroelectric random access memory (FeRAM) and ferroelectric field-effect transistor (FeFET), phase-change random access memory, electrochemical memory have been intensively studied and some of them are about to enter the market [14-18]. To take advantage of unique properties from organic electronics for extending the field of applications, a wide variety of organic materials or hybrid materials, including polymers, small molecules, hybrid perovskite, ferroelectric organic polymers, have been studied and utilized as hysteretic elements in integrated memory devices, especially in organic non-volatile memory (ONVM) devices [19], [20]. Despite the architectural difference, organic memory devices that are most widely studied are those holding information by using resistance-switching behavior, which can be modeled by employing memristive equations and are widely proposed to participate in artificial neural networks as artificial neuromorphic devices [21-23]. However, another type of memory devices, the memcapacitors or capacitive memory devices, have received less attention although it can also possess memory behavior via switchable capacitances and even superior in prospective applications (like artificial neural networks) with lower power consumption and free of steady-state crosstalk currents [24-26]. Furthermore, similar to the role of OLED in electronics, memory devices nowadays should not limit

out of information via light emission. Such kind of memory devices are referred to as optical storage devices.

to electrical accessibility but have functionality though optical pathways such as storage and read

Figure 2.1.2: Photographs of (a) organic flash memory and (b) re-programmable non-volatile memory arrays produced on flexible substrates. Pictures are taken from [27], [28].

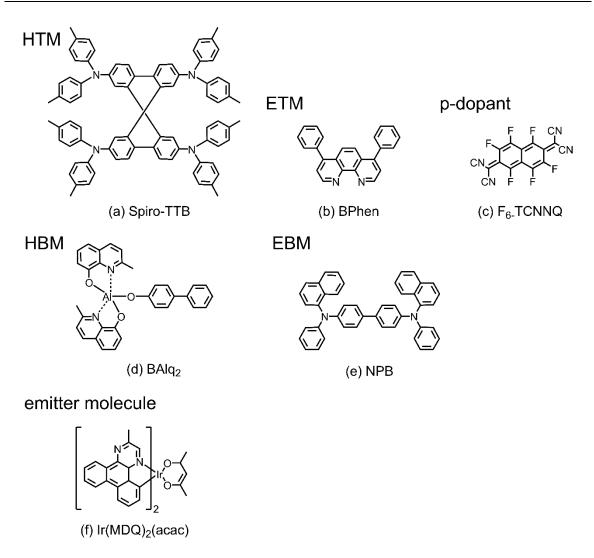

With the consideration of appropriate device architecture, storage capabilities, device down-scaling, optical switching and read-out property, as well as easy fabrication, a novel concept of diode-based, non-volatile, capacitive memory device is demonstrated in this thesis. In the beginning, a fundamental introduction of organic semiconductors is provided in Chapter 2 as a theoretical background for carbon-formed molecules as well as the related charge carrier motions. Based on this knowledge, concepts of organic junctions like Schottky junction, p-n junction, p-i-n junction and devices like MOS capacitor and OLED, are further discussed in Chapter 3. An overview of organic memory devices is then presented in Chapter 4 with a focus on organic resistive memory devices, organic transistor-based memory devices, and organic ferroelectric memory devices. Within Chapter 5, the basics of experimental techniques that have been used for device fabrication and characterization are described, along with an overview of materials used in this thesis.

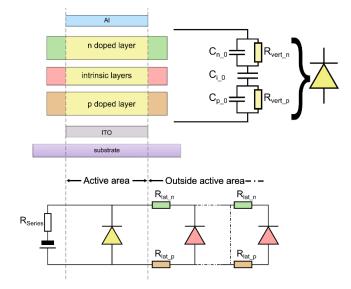

In order to obtain a structure comprehension for further memory device optimization, the results part starts with Chapter 6 by investigating the centimeter-scale lateral charge flow in crossbar structure

with doped layers that are larger than the active area. Not limited to the memory devices studied in this thesis, organic devices commonly have crossbar structures where doped layers are applied (with larger occupied area than active area) in a sandwich layer architecture stacked between two electrodes. The high conductivity of doped layers facilitates the charge carrier transport and thus device performance in organic electronics, but sometimes introduces a rarely noticed side-effects of leakage current and extra capacitance increase at low frequency. The leakage currents are in general unwanted for electronics as they increase the device's power consumption, reduce the on-off or rectification ratio of transistors and diodes, and remove the information stored in memory device and thus ruin the basic memory function. Here, by studying the centimeter scale lateral charge flow in OLEDs, an easy and effective method is proposed to prevent the introducing of leakage current by structuring the doped layers. With the assistance of a newly developed RC circuit, the controlled capacitive charge up of the doped layers outside the active area can be used for extracting the information about the conductivity as well as the corresponding activation energy of the n-doped and p-doped layer, simultaneously. In this way, the doped layer quality can be easily checked after device fabrication. More importantly, the device layout, especially for the memory device, is proven to require have well-structured doped layers.

Further results and investigations regarding the proposed p-i-n-metal-oxide-semiconductor (pinMOS) memory are presented in Chapters 7 and 8. The pinMOS memory device is a memory device with multiple-bit storage that can be tuned and read out electrically or optically, i.e., it can be programmed by either voltage application via Zener tunneling or ultraviolet light illumination, and be read-out by either capacitance (electric signal) or light emission (optical signal). The pinMOS memory is based on an OLED with an integrated capacitor on which charges can be added or removed in fractions, revealing a very decent memory performance in terms of repeatability, cyclic endurance, and retention time. The working mechanisms, both under quasi and dynamic steady-state operation conditions, are proposed to get an essential understanding of this novel concept of device for further optimization or applications. Three advantages are pointed out for the pinMOS memory: easy to achieve multiple-bit storage and possibility for device downscaling; an easy fabrication process that is a straight-forward layer-by-layer deposition similar to OLED; the ability to be written and read out by light, which is attractive for future use in integrated electronic and photonic circuits.

As summarized in Chapter 8, the pinMOS memory and the basic understanding behind it might open the pathway for future applications not only in the general electrical memory system but also in the full-color visual system, optical-electrical-optical repeater systems, or capacitive neural networks.

Finally, a conclusion of the work is given in Chapter 9.

## **Chapter 2**

### **Fundamentals of organic semiconductors**

In this chapter, the basic physical properties of organic semiconductors are introduced from aromatic organic molecules to solids and related charge carrier behaviors. The hybridization of carbon atoms and the resulting stable molecules with partially delocalized electrons are shown in Sec. 2.1 by using examples of ethane and benzene. The transition from a single molecule to a solid state molecule is discussed with the consideration of interactions between molecules and the spin of electronic state. Furthermore, two different charge carrier transport models are overviewed in Sec. 2.2 with different applicable conditions. Besides charge transport in the semiconductor, the injection from electrode is also highlighted in Sec. 2.3 with aspects of contact interface, current limitations regarding the injection barrier, and injection mechanism models. The doping, which is important for improving both, the charge carrier mobility and injection efficiency, is demonstrated in Sec. 2.4. This chapter paves the fundamental way of understanding semiconductor devices.

### **2.1** Electronic states of a molecule

#### 2.1.1 Atomic orbitals and molecular orbitals

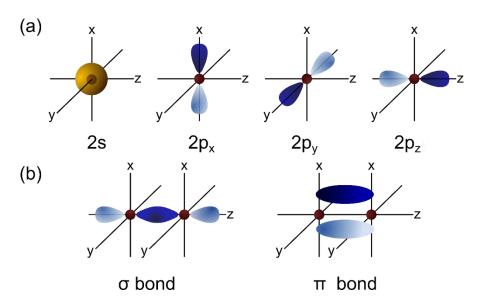

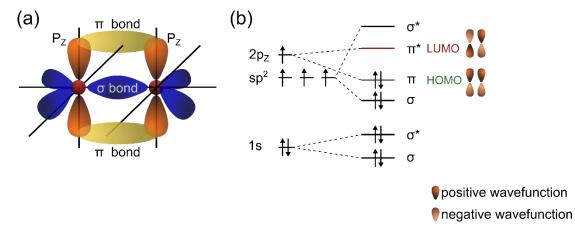

Organic semiconductor materials are carbon-based materials with heteroatoms, therefore the discussion will start with the electronic structure of carbon atoms. A single carbon atom has six electrons in its ground state and atomic orbitals are referred to as s orbital and p orbital with angular momentum quantum number of 1 and 2, respectively. As illustrated in Fig. 2.1.1 (a), the s orbital is radially symmetric with a spherical charge distribution while the three p orbitals named after the plane in which they lie have a positive and a negative (the sign of the wavefunction) lobe with a "dumbbell" charge distribution [29]. The possibility of the electron being in either lobe in one p orbital is the same. When two atomic orbitals hybridize, molecular orbitals called  $\sigma$ -orbitals will be formed if it is head-on overlapping, otherwise  $\pi$ -orbitals will be formed if it is side-by-side overlapping (Fig. 2.1.1 (b)) [30].

Figure 2.1.1: (a) The atomics and p orbitals. (b) The molecular  $\sigma$  and  $\pi$  orbitals.

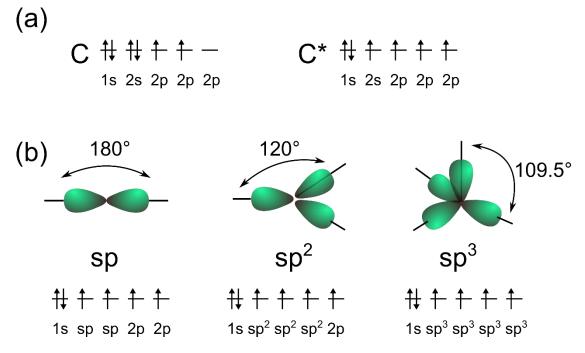

A single carbon atom has six electrons in its ground state with the configuration of  $1s^22s^22p^2$ , i.e., two electrons in a 1s orbital, another two in a 2s orbital, and the remaining two in two out of the three 2p orbitals  $(2p_x, 2p_y \text{ or } 2p_z)$  as shown in Fig. 2.1.2 (a). When carbon is in its elementary atomic form of  $1s^22s^22p_x^{-1}2p_y^{-1}2p_z^{-0}$ , only two covalent bonds are available to form in the singly occupied p orbitals. However, if one of the doubly occupied 2s electrons excited (or promoted) into the empty  $2p_z$  orbital, four singly occupied orbitals enable four covalent bonds. As a result, new hybridized orbitals with more stable bonds,  $\sigma$  bond or  $\pi$  bond, are obtained by a linear combination of atomic orbitals between the 2s and 2p orbitals (Fig. 2.1.2 (b)).

As shown in Fig. 2.1.2, after the electron excitation, there are three possible hybridizations from the combinations of orbitals, sp, sp<sup>2</sup>, and sp<sup>3</sup>, named after the number of participating p orbitals. For the sp hybridization, a 2s orbital hybridized with one out of the three 2p orbitals, resulting in two sphybrid orbitals with a bond angle of 180° in a linear arrangement. In the case of sp<sup>2</sup> hybridization, two p orbitals (assume to be  $2p_x$  and  $2p_y$ ) are mixed with the 2s orbital, leading to three  $sp^2$  orbitals distributed in the xy-plane with a bond angle of 120° in a trigonal arrangement. The unhybridized  $2p_z$  orbital is orthogonal to xy-plane of the new sp<sup>2</sup> orbitals. When all of the three p orbitals participate, sp<sup>3</sup> hybridization with four equivalent hybridized orbitals can be obtained with a bond angle of 109.5° in a three-dimensional tetrahedral construction. The combination of different types of hybridization leads to different chemical bonds between carbon atoms. For example, the combination of two hydrogen atoms and two sp hybridized carbon atoms results in ethyne (CH=CH), which has one  $\sigma$ -bond and four  $\pi$ -bonds between the two carbon atoms. However, a similar case between two sp<sup>2</sup> hybridized carbon atoms will lead to ethene (CH<sub>2</sub>=CH<sub>2</sub>) with only two  $\pi$ -bonds, and so on, two sp<sup>3</sup> hybridized carbon atoms yield the molecule ethane (CH<sub>3</sub>-CH<sub>3</sub>) with  $\sigma$ -bond only. Therefore, hybridization has large impact on the molecules and consequently determines the properties of the materials.

Figure 2.1.2: (a) The ground state and excitation state configurations of the carbon atom. (b) The sp, sp2, and sp3 hybridizations and the corresponding carbon configuration.

Among all types of hybridizations discussed above, sp<sup>2</sup> hybridizations as well as the bonds between the sp<sup>2</sup> hybrid orbitals are most important for organic semiconductors and thus will be further discussed in detail. The simplest case is ethene which has two threefold degenerate sp<sup>2</sup> orbitals inplane and two 2pz orbitals from the carbon atoms out-plane being perpendicular as shown schematically in Fig. 2.1.3 [31]. Since energy contributions from orbitals of different energy are small, we can simplify the stimulation of resulting molecular orbitals energy by only considering the mutual interaction of orbitals at equal or similar energy. Here, a covalent  $\sigma$ -bond is formed between two out of the six sp<sup>2</sup> orbitals along the internuclear axis, while  $\sigma$ -bonds are formed between the 1s orbitals that not shown here. Furthermore,  $\pi$ -bonds without rotational symmetry formed due to the interaction of the  $2p_z$  orbitals. The bonding molecular orbital comes from the energetic splitting of two single orbital energy levels with different resonance interactions and leads to different attractive forces. For the 1s orbitals which are close to the core, the resulting bonding from  $\sigma$  orbital and anti-bonding from  $\sigma^*$ -orbital has little splitting due to the negligible resonance interaction. However, since the principal quantum number of the carbon 1s orbital is one, it will be fully occupied by two electrons, leading to no participation in the covalent carbon-carbon band. For the sp<sup>2</sup> hybrid orbitals, due to a large amount of charge overlapping, they create a strong bonding  $\sigma$ and anti-bonding from  $\sigma^*$  with a large resonance integral and thus a large energetic splitting. All three sp<sup>2</sup> hybrid orbitals from one carbon own one single electron for each orbital. Once they combine with the electron from either another  $sp^2$  hybrid orbital in another carbon atom or the 1s orbital in the hydrogen atom, the new electron pair will fill the low-lying bonding  $\sigma$  and leave the high-lying anti-bonding  $\sigma^*$  empty. Since the energetically lowest states will always be filled first, the low bonding states of the three  $\sigma$  orbitals will be filled right after the 1s orbitals. Finally for the  $p_z$  orbitals which are comparable far away from the nuclei, the interaction between them is weak, resulting in weak splitting between the bonding  $\pi$  and anti-bonding  $\pi^*$ . Due to the smaller charge overlapping  $\pi$ -bonds, in general, are much weaker than  $\sigma$ -bonds. As the third order of being filled by electrons, the bonding  $\pi$  orbital is the highest occupied molecular orbital (HOMO). The next higher orbital in ethene is the anti-bonding  $\pi^*$  orbital, which is empty, referred as the lowest unoccupied molecular orbital (LUMO). The energy gap is then given by the energetic distance between the LUMO and the HOMO level as:

$$E_g = E_{LUMO} - E_{HOMO} \tag{2.1.1}$$

In organic semiconductors, electronic processes like charge injection from metal electrodes, light absorption, photon excitation, etc. decide the application of the materials. Because of the weaker splitting of  $\pi$  and  $\pi^*$  orbitals, the moderate energy difference between the orbitals or relative to the typical electrode work functions enables various electronic processes. For example, the charge injection from electrodes is impossible due to the significant energy difference, and the optical transitions between the  $\sigma$  and  $\sigma^*$  orbitals will be out of visible light range, requires much higher energy like UV light. Therefore, the energy levels of HOMO and LUMO are two important orbitals for organic semiconductor applications, and their energy levels need to be tuned for their applications.

Figure 2.1.3: (a) Schematic of sp<sup>2</sup> hybridizations in ethene with  $\sigma$  and  $\pi$  orbitals. (b) Energy levels of the ethane.

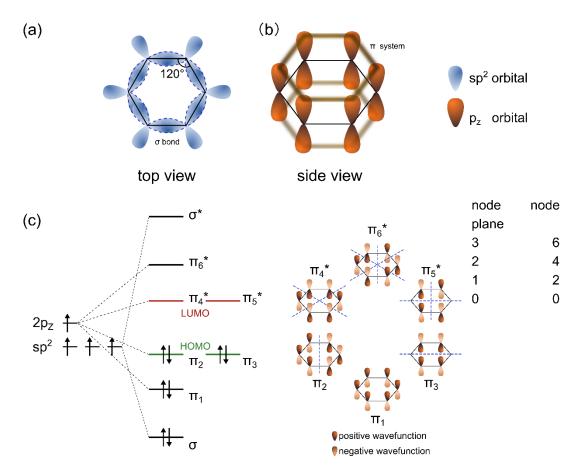

Furthermore, electrons can delocalize in the HOMO and LUMO in a conjugated system with neighboring sp<sup>2</sup> hybrid orbitals sharing one  $\pi$ -bond, resulting delocalized  $\pi$ -system like benzene shown in Fig. 2.1.4 [32][33]. The electrons from the six p<sub>z</sub> orbitals with  $\pi$ -system bonds in benzene are effectively delocalized over the conjugated system across the full benzene ring. Meanwhile, the six sp<sup>2</sup> hybrid orbitals are arranged in a planar hexagon with a larger network of carbon rings, forming  $\sigma$  bonds with either further carbon atoms or hydrogen atoms. Depending on the sign of six wavefunctions of the p<sub>z</sub> orbitals, the symmetry or antisymmetric combinations will result in six molecular orbitals. Among these molecular orbitals, different numbers of nodes lead to different energy levels, which are presented by three bonding  $\pi_1$ ,  $\pi_2$ ,  $\pi_3$  orbitals with lower energy and three anti-bonding  $\pi_4^*$ ,  $\pi_5^*$ ,  $\pi_6^*$  orbitals with higher energy. The HOMO ( $\pi_2$ ,  $\pi_3$  orbitals) and LUMO ( $\pi_4^*$ ,  $\pi_5^*$  orbitals) are illustrated in Fig. 2.1.4 (b).

Figure 2.1.4: (a) Top view of  $sp^2$  hybrid orbitals in a carbon ring configuration. (b) Side view of  $p_z$  orbitals and the delocalized ring-like  $\pi$  systems formed by  $\pi$  bonds at the above and bottom of  $p_z$  orbitals. (c) Energy levels of the benzene and graphical representation of the molecular orbitals with their node planes.

#### 2.1.2 Solid states

In a solid state, atoms or molecules are held together by a attractive force (beside repulsive force) between them. The strong covalent bonds which are the common bonds between inorganic atoms, cannot exist in organic semiconductors since all electrons are already incorporated in bonding orbitals by hybridization so that molecules do not usually form any further covalent bonds. However, the charge distribution of organic molecules is not entirely rigid, implying that a temporary fluctuating dipole moment can be induced if there is a temporal fluctuation in the charge distribution in a molecule (e.g. a displacement of the delocalized  $\pi$ -system). This dipole will further induce a corresponding fluctuating dipole in the second molecule. The attractive force between the correlated dipoles is the van-der-Waals interaction, which will stabilize the dipoles and which forms the attractive force between them.

The van-der-Waals force strongly depends on the distance r between the molecules. When a temporary dipole moment  $p_1$  is induced in one molecule, an associated electric field F will be formed by:

$$\mathbf{F} \sim \frac{p_1}{r^3} \tag{2.1.2}$$

while another fluctuating dipole in the second molecule will be induced by:

$$p_2 \sim \alpha \frac{p_1}{r^3} \tag{2.1.3}$$

where  $\alpha$  is the polarizability of the second molecule which indicating the ability to induce dipole moments in charge distribution. Therefore, the potential energy associated with a van-der-Waals interaction is given by:

$$\mathbf{E} = -p_2 \cdot \mathbf{F} \sim -\alpha \frac{p_1^2}{r^6} \tag{2.1.4}$$

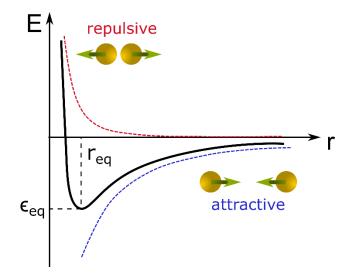

which decrease with the sixth power of the distance and it is part of the Lennard-Jones potential which describes the repulsive and attractive forces between two molecules [34]:

$$V(r) = A \frac{1}{r^{12}} - B \frac{1}{r^6}$$

(2.1.5)

where A and B are molecule specific coefficients. The nucleus will repel each other as they are all positively charged. The closer they get, the more repulsive the Coulomb interaction will be.

Figure 2.1.5: Schematic of Lennard-Jones potential, consisting of an attractive and a repulsive part.

As schematically shown n Fig. 2.1.5, with the increase of molecular distance r, the repulsive part decreases much faster than the attractive part and finally achieves an equilibrium state in a global energetic minimum. At the equilibrium state, the distance  $r_{eq}$  between two bounded molecules is defined when the net force is zero, and the depth of the potential presents the maximum binding energy  $\epsilon_{eq}$  needed for breaking the bond. Since the typical binding energy is in the range of several 0.1 eV or smaller, similar to the thermal energy at room temperature (~0.25 eV), the bonds from the van-der-Waals force thus are really weak and can be broken thermally [35]. Furthermore, thermally induced energy fluctuations could already separate the two molecules if the  $k_BT$  ( $k_B$  is the Boltzmann's constant) is higher than binding energy  $\epsilon_{eq}$ , resulting in a liquid or gaseous phase and thus a low melting point or sublimation temperature of the material.

#### (a) single molecule (b) amorphous solid (c) crystalline solid

Figure 2.1.6: Comparison of the distribution of the energy levels HOMO (or valence band) and LUMO (or conductive band) in (a) a single molecule, (b) amorphous solid, and (c) crystalline solid.

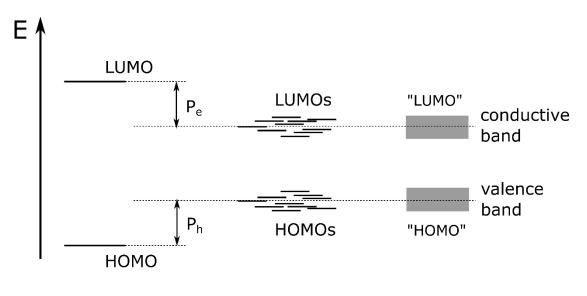

Organic solids can be crystalline or amorphous. Due to the above discussed van-der-Waals forces between the organics molecules, most of them are not arranged perfectly in an amorphous solid. The molecule in the disorder solid state will polarize and redistributes charges with adjacent molecules for reaching an energetically favorable configuration. Therefore, the energy levels of the HOMO and LUMO in amorphous solid will shift due to the different interactions between neighboring molecules. As a consequence, the disorder arrangements of molecules from the local variations in polarization energy for electrons  $P_e$  and holes  $P_h$  will lead to a variety of different slight energy level shift as compared with a single molecule shown in Fig. 2.1.6 (b) [36].

In organic crystals, however, molecules have a regular arrangements, such as in anthracene or pentacene whose  $\pi$ -systems are mainly located above and underneath the molecular plane, resulting in close electron clouds and thus strong interaction. The regular arrangement of the molecules leads to the formation of electronic bands. Due to the polarization energy, the ionization potential decreases (by P<sub>h</sub>) while the electron affinity is increased (by P<sub>e</sub>), leaving a narrower bandgap in crystal as shown in Fig. 2.1.6 (c).

#### **2.1.3** Singlet and triplet states

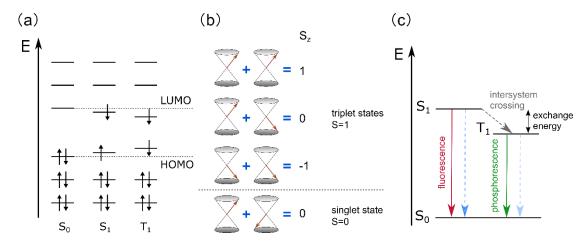

Figure 2.1.7: (a) Orbital configuration schematic of singlet and triplet states. (b) Vector diagram of four spin wavefunctions regarding the relative orientations of the two electron spins for the singlet and the triplet states. (c) State schematic of singlet and triplet states with radiative (fluorescence for singlet state and phosphorescence for triplet state) and non-radiative decays.

The spin of an electronic state of a molecule is given by the total spin of all electrons in all orbitals. As the Pauli exclusion principle states, it is impossible for two electrons in an atom to have the same four quantum numbers, which are the principal quantum number n, the Azimuthal quantum number  $\ell$ , the magnetic quantum number  $m_{\ell}$ , and the spin quantum number  $m_s$ . Therefore, the maximum two electrons that occupy the same orbital have to have opposite spin states, and are referred to as spin pairing. These paired electrons in filled orbitals contribute zero to the total spin and the state is singlet ground state  $(S_0)$ . When there is an unpaired electron, a doublet state occurs that shows the splitting of spectral lines into a doublet. Further two unpaired electrons then result in triplet states. However, it is sufficient only to consider the concept of singlet and triplet states in this thesis since only these two states can be formed when one electron of the paired electrons is excited to a higher energy level [37]. In an excited state configuration, the unpaired electrons are usually one located in a  $\pi^*$  orbital and one in a  $\pi$  orbital. For the singlet excited state, the spin of electron in the  $\pi$  orbital is promoted in the same spin orientation as it was in the ground state, therefore being antiparallel to the remaining electron in the  $\pi$  orbital, adding up a total spin of zero. For the triplet excited state, the spin of electron in the  $\pi$  orbital has the same spin orientation (parallel) as the unpaired electron in the  $\pi^*$  orbital, resulting in a total spin of 1. As indicated in Fig. 2.1.7 (a), the excited states then can be referred to in energetic order as S<sub>1</sub>, S<sub>2</sub> and so on for singlet excited state, or T<sub>1</sub>, T<sub>2</sub>, and so on for triplet excited state. The unpaired electrons in the excited state dominate the forming of a twoparticle system, consisting of four eigenstates for description as illustrated in schematic in 2.1.7 (b). These eigenstates are listed in Tab. 2.1.1 [38]:

| spin wavefunction                                                                                | S | Sz | _ |

|--------------------------------------------------------------------------------------------------|---|----|---|

| $\Psi_{\text{spin}, T^+} = \alpha_1 \alpha_2$                                                    | 1 | 1  | _ |

| $\Psi_{\text{spin, T0}} = \frac{1}{\sqrt{2}} \left( \alpha_1 \beta_2 + \beta_1 \alpha_2 \right)$ | 1 | 0  |   |

| $\Psi_{\text{spin, T}-} = \beta_1 \beta_2$                                                       | 1 | -1 |   |

| $\Psi_{\text{spin, S}} = \frac{1}{\sqrt{2}} (\alpha_1 \beta_2 - \beta_1 \alpha_2)$               | 0 | 0  |   |

Table 2.1.1: The spin wavefunctions of the four eigenstates to the two-particle system with the yielding total spin and magnetic field in the z-direction.

Where the  $\Psi_{spin}$  is the spin wavefunction, and  $\alpha$  or  $\beta$  denote the spin wavefunctions of the oneelectron states with eigenvalues of s = 1/2, m<sub>s</sub> = 1/2 or s = -1/2, m<sub>s</sub> = -1/2, index 1 and 2 refer to electron 1 and 2, giving the eigenvalues S of total angular momentum to be 1, 0, and S<sub>z</sub> of magnetic field in z-direction to be 1, 0, -1. The first three spin wavefunctions with a total spin of 1 are the arrangement for the triplet states, while the last spin wavefunction with a total spin of 0 refers to the singlet state. As shown in Fig. 2.1.7 (c), there is an exchange energy of several tenths of eV by which the energies between the first singlet  $(S_1)$  and triplet  $(T_1)$  state differ, and which scales exponentially with the overlap of the respective electron wavefunctions. Therefore, the more significantly HOMO and LUMO overlap, the larger the exchange energy will be. Due to the spin selection rule, the triplet state T<sub>1</sub> with lower energy level cannot be accessed by a direct electronic excitation from ground singlet state  $S_0$  [39]. When the electron in the ground singlet state  $S_0$  absorbs energy, it will excite to another singlet state S<sub>1</sub>, and then follows several possible processes that occur between different states. If the excited state  $S_1$  has a transition back to the  $S_0$ , it will have either radiative or nonradiative (quenching or relaxation) decay. The former case, referred to as fluorescence, will give off a photon which is invariably red-shifted, i.e., the wavelength is longer than the one that initially led to excitation. Nevertheless, the electron can also end up in the triplet excited state T<sub>1</sub> via intersystem crossing, subsequent either non-radiative relaxation or phosphorescence that electron drop back down to the  $S_0$ , accompanied by the emission of a photon.

### 2.2 Charge transport

#### 2.2.1 Charge carrier mobility

Charge carriers will move once they are injected into the semiconductor and then driven by an electric field with a gradient in the electrostatic potential  $\Phi$ . The contributions from drift and diffusion will sum up to a total current as:

$$j_{tot} = j_{drift} + j_{diffusion} \tag{2.2.1}$$

of which the drift current through the semiconductor can be given by the number N of charges e that flow per unit time t and unit area A as:

$$j_{drift} = \frac{eN}{At} = \frac{eNl}{At} = env_{drift} = en\mu F$$

(2.2.2)

where *l* is the unit length, *n* is the number density of charges, that is, the charge carrier contraction, and  $v_{drift}$  is the mean drift velocity that charges obtained from the electric field *F*. Therefore, the associated mobility of the charges can be gained from:

$$\overrightarrow{v_{drift}} = \mu \vec{F} \tag{2.2.3}$$

Under a gradient in the electrostatic potential, there is also a gradient in the charge carrier concentration that leads to an effective movement from the region with higher concentrations towards regions with a lower concentration. Therefore, the diffusion current can be gained by:

$$j_{diffusion} = -eD\frac{dn}{dx} = -eD\nabla n$$

(2.2.4)

where D is the diffusion coefficient. The final equation is the continuity equation (not shown), in which can be gained by using the Einstein relation between diffusivity D and mobility as:

$$eD = \mu k_B T \tag{2.2.5}$$

Based on the above discussion, the total current now can be sum up as:

$$j_{total} = en\mu\nabla\Phi - eD\nabla n \tag{2.2.6}$$

where the former part comes from the drift current and the latter part comes from the diffusion current. Which one dominates in the final current depends on the relative magnitude of the relevant gradients. In organic semiconductors, the charge concentration and its gradient are smaller (compared with that of inorganic semiconductors), and the current is thus usually dominated by drift. However, there are some exceptions like the condition of space charge limited current (SCLC).

#### 2.2.2 Charge carrier transport

In the concept of orbital, the charge carrier transport is the process that an electron in the LUMO orbital transfer to the empty LUMO orbital, or a hole transfer between the HOMO orbitals equivalently. In order to have charge carrier transfer process, one necessary yet not sufficient condition is the electronic coupling among the sites in orbitals. At absolute zero temperature (T $\sim$ 0 K), an electron (or a hole) in a regularly ordered crystal will move coherently within a band of states. If the crystal is then in an electric field, the scattering process at the band edge drives the charge carrier to move at constant mobility. However, for a molecular with irregular structure, such perfect conditional charge carrier scattering. If such scattering is weak compared with the overall electronic coupling between the adjacent molecules, the band transport model can be used for describing the charge transport, yielding an inverse temperature relation with charge carrier mobility. If the vibronic coupling of molecular becomes comparable to the electronic coupling at a high temperature, the charge carrier will scatter at each site which can be described by a hopping model with different temperature dependence of the charge carrier mobility [40].

**Band transport** As described above, band transport can be obtained in organic semiconductors that have a highly crystalline structure. In this case, the interaction energy is large than the energy

fluctuations from dynamic or static disorder, and charge carrier transport can be modeled by a band. The charge carriers are delocalized across the regularly arranged molecules that form a propagating Bloch wave which may be scattered by lattice vibrations [41]. As discussed above, compared to inorganic crystals where covalent interactions dominate, the electronic coupling is weak in organic molecular crystals. Furthermore, the bands of organic semiconductors will be narrow due to the vander-Waals force between the molecules, leading the charge carriers behave as if having a larger effective mass m\* which is determined by the electronic coupling. Therefore, the charge carrier mobility can be given by Drude model as:

$$\mu = \frac{e\tau}{\mathrm{m}*} \tag{2.2.7}$$

where  $\tau$  is the mean scattering time between collisions of the charge carriers. As the Eq. 2.2.7 indicates, a larger effective mass compared to the inorganic semiconductors results in a lower mobility, which can be easily understood by less efficient acceleration after a higher mass collisions with defects or phonons.

When band-like transport prevails, the scattering with defects, phonons, or electron-interactions will increase with the increase of temperature and results in lower mobility as the temperature dependence equation:

$$\mu \propto T^{-n}, \quad 0 < n < 3$$

(2.2.8)

of which the ideal exponent n is 3/2 at room temperature. At low temperature (T<50 K) however, the relation will no longer be true since the mobility is saturated.

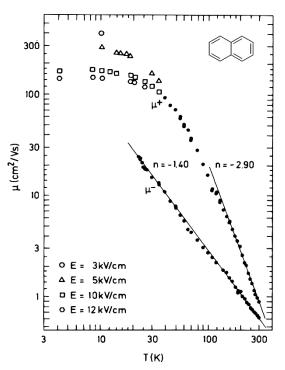

Figure 2.2.1: The temperature dependence of electron (n=2.90) and hole (n=1.40) mobilities in an ultrapure naphthalene with electric field applied parallel to the crystallographic *a* direction. (Figure is redrawn from [42])

An experimental example of proving the band-like transport in an organic molecular crystal was presented by Karl et. al by measuring the temperature dependence of charge carrier mobility in naphthalene crystal (Fig. 2.2.1) [42]. In a temperature range of 4 K to 300 K, both electron and hole mobilities were measured along the crystallographic *a* and *b* directions with different electric fields E. With the decrease in temperature, the mobility increases linearly in the double-logarithmic figure, revealing a temperature power-law with an n of 2.90 for hole transport and 1.40 for electron transport. When the temperature is below 30 K, the hole mobility reaches the saturation value and only shows the dependence on electric field.

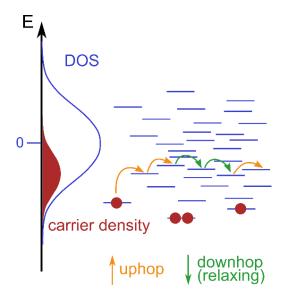

Figure 2.2.2: Schematic charge hopping transport in amorphous solids with a Gaussian DOS distribution. The orange arrows indicated the "uphop" where charge "jump" from low energy site to high energy site thermally, while the green arrows reveal the "downhop" where charge in the high energy site relaxes into the low energy site. The hopping process is only possible if the destination state is unoccupied.

**Hopping transport** In an amorphous organic semiconductor, regular arrangements of molecules no longer exist, and an energies spread, therefore, will come from dynamic or static disorder. If such energies are larger than the nearest neighbor interaction energy, the delocalized wavefunctions will be destroyed and thus band transport will not occur anymore. Herein, charge carriers are localized at individual states, i.e., the states in the HOMO and LUMO levels are distributed. The concept of incoherent hopping transport is applicable to this situation, as the carrier has to "hop" from its state (site *i*) into a nearby free state (site *j*) and then proceeds a sequence of non-coherent transfer. If the energy level of the destination site *j* is lower than the initial site *i*, the charge carrier can relax into the lower state site (green arrows in Fig. 2.2.2), which is preferred. Otherwise the carrier in the site *i* needs to be promoted with additional thermal energy in order to "jump" into site *j* which has higher energy (orange arrows in Fig. 2.2.2). This site to site carrier motion is a phonon-assisted tunneling mechanism, in which electrons tunneling through an energetic barrier involving lattice phonons whose energy facilitates the process [43][44]. The hopping rate (transition rate)  $v_{ij}$  can be given by Miller-Abrahams rate as:

$$v_{ij} = v_0 \exp(-2\gamma r_{ij}) \begin{bmatrix} \exp(-\frac{\Delta E_{ij}}{k_B T}) & \Delta E_{ij} > 0 \text{ uphop} \\ 1 & \Delta E_{ij} \le 0 \text{ downhop} \end{bmatrix}$$

(2.2.9)

where  $v_0$  is the maximum hopping rate (attempt-to-escape frequency), and  $\gamma$  is the inverse localization radius that proportional to the transfer integral,  $\Delta E_{ij}$  and  $r_{ij}$  are the energy and distance difference between the site *i* and *j* [45]. The transitions from lower energy site *i* to higher energy site *j* with energy difference  $\Delta E_{ij} \gg k_BT$  is unlikely, indicating that unlike the band transport, hopping transport at low temperature is either impossible or has small mobility. The mobility can be expressed with temperature dependence as:

$$\mu(T) = \mu_0 \cdot \exp(-\frac{T_0^2}{T^2})$$

(2.2.10)

where  $\mu_0$  is the mobility with infinitely high temperature and  $T_0$  is proportional to the width of the Gaussian DOS (density of states) [46]. For the hopping transport, the higher the temperature, the lower the mobility will be, which is opposite to the band transport.

When an external electric field is applied, the hopping transport is promoted since the electric field lowers the potential energy in the direction of the charge carrier drift. The probability of uphopping, where the carriers (electrons as the example) jump into energetically higher states, becomse higher since the electron gain additional energy of ca. e|F|a (*a* is the mean distance of the molecule ). Meanwhile, the number of "jumps" without the support from additional thermal energy is increased, indicating that the possible hopping sites increase. As a consequence, hopping mobility has field dependence as charges are transported more efficient with a higher electric field.

Furthermore, the charge carrier concentration also determines the mobility of hopping transport as partly indicated in Fig. 2.2.2. When the carrier concentration is low, meaning the numbers of electrons in the LUMO (or holes in the HOMO) is less, the charge transport will happen in the region where the energy of the states is low, and the density is small. Therefore, the spatial site distance  $r_{ij}$  as well as energetic difference  $\Delta E_{ij}$  between two neighboring sites are large, resulting in a low hopping rate according to Eq. 2.2.9. When the carrier concentration is high, the low states are filled with charges preferentially, allowing the energetically higher free states to participate in the hopping transport. Following the Gaussian distribution, the transport energy is more close to the maximum value of DOS, leading to a smaller  $r_{ij}$  and  $\Delta E_{ij}$  that increase the charge transport mobility.

It is worth to mention that although a one-dimensional schematic is shown for the hopping process, the three-dimensional space is the real model, where charge carriers can bypass the high energy sites by transporting through multiple low energy sites with larger total site distance.

### 2.3 Charge injection

#### 2.3.1 Current limitation

Under the dark condition, the currents that flow through a device (i.e., through a optoelectronic device where a semiconductor is applied with metal contacts in various layouts like organic lightemitting diodes (OLEDs), organic solar cells (OSCs), organic field-effect transistors (OFETs), or organic non-volatile memories (ONVMs)) can be limited by either the efficiency of charge injection from the electrode, associated as injection limited current (ILC), or by the charge crowding, referred to as space charge limited current (SCLC) [47-54]. In either case, the current density can be described by the drift current with the Eq. 2.2.2 discussed in Sec. 2.2.1.

**Metal-semiconductor interface** For maintaining a constant current flow in the device, charge carrier injection between the metal (electrode) and semiconductor is necessary and is limited by interrelated factors. If the current cannot meet SCLC conditions, which will be discussed later in this section, the current in the device is injection limited, i.e., the electrode cannot supply a sufficient number of charge carriers and the current is determined by these limited carriers. Otherwise the current will be limited as space charge limited current. Therefore, the ability of an electrode in sustaining SCLC conditions plays an important role in deciding the type of current limitations. Such ability, however, depends on both the injection barrier between the metal-semiconductor interface, and the charge carrier mobility of the organic semiconductor.

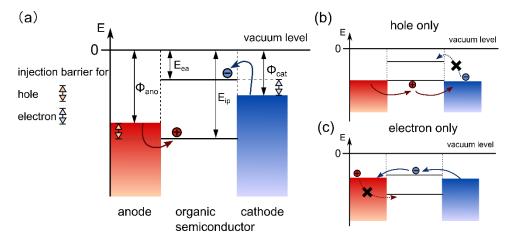

The simplified case for contact discussion is a metal-semiconductor-metal device shown in Fig. 2.3.1 (a) regardless of the band bending. The work function of both electrodes,  $\Phi_{ano}$  for anode and  $\Phi_{cat}$  for cathode, are gained by taking the Fermi energy with respect to the vacuum level  $E_{vac}$ . For ideal interfaces, the injection barrier for holes is given by the energy difference between the work function of the anode  $\Phi_{ano}$  and the ionization potential  $E_{ip}$  of the semiconductor, while the electron injection barrier is the difference between the work function of the anode  $\Phi_{cat}$  and electron affinity  $E_{ea}$  of the semiconductor. The built-in potential is then the difference between the two electrode work functions. Although there are some little correlations as well as different derivations, several theorems state that the ionization energy and electron affinity can be approximated as HOMO and LUMO energy, respectively [55]. The carrier injection can be improved or designed by semiconductor bandgap tuning, electrode selection. Furthermore, devices with different carrier types, like hole-only device (Fig. 2.3.1 (b)) or electron-only device (Fig. 2.3.1 (c)), can be fabricated by blocking one type of carriers injection [56]. The higher the mobility of charge carriers, the more crucial is the height of the injection barrier.

Figure 2.3.1: Energy diagram of the metal-semiconductor-metal device with (a) common alignment of energy levels, and (b) hole only transport or (c) electron only transport by tuning of electrode work function or semiconductor bandgap to prevent one type of carrier injection.

**Injection limited current (ILC)** When the injection barrier is large, the current flow is limited by the number of charges injected at the contact per time and per area. Here, the injection limited current

does not account for the subsequent carrier transport, and the associated injection rate for holes as an example can be given as:

$$\frac{dn_{+}}{dt} = G - k_{tr}n_{+} - \gamma n_{-}n_{+} \tag{2.3.1}$$

where G is the rate of hole injection per unit volume, and  $n_+$ ,  $n_-$  are the hole and electron concentration, respectively. Also,  $\gamma$  is the rate constant for bimolecular recombination and  $k_{tr}$  is the rate constant for monomolecular decay which corresponds to the hole reciprocal transit time as  $k_{tr} = 1/\tau_+$ , of which further depends on the electric field F as:

$$\tau_{+} = \frac{d}{\mu_{+}F} \tag{2.3.2}$$

where *d* is the semiconductor thickness and  $\mu_+$  is the hole mobility. Here, the electric field is constant across the whole semiconductor as F = V/d. Since only hole injection is considered in this case, i.e., the electron injection is comparable small, yielding that  $k_{tr}n_+ \gg \gamma n_-n_+$ , the hole concentration  $n_+$  then can be calculated from the steady-state where  $dn_+/dt = 0$  to be  $n_+ = G/k_{tr}$ , which then, as mentioned above, can distort the drift current (Eq. 2.2.2) as:

$$j = en_{+}\mu_{+}F = e\frac{G}{k_{tr}}F = e\frac{G}{\mu_{+}F}d\mu_{+}F = eGd$$

(2.3.3)

The *Gd* yields the rate of hole injection per unit volume, referred to as *g*. Then the current can then be expressed as j = eg, which has dependence only on the injection rate. The injection limited current (ILC) can be extended to electron injection or injection from both electrodes following the same assumptions above, and the gained current has no relationship with either the electric field or temperature.

**Space charge limited current (SCLC)** When the injection barrier is small, meaning sufficient charge carriers injected from the electrode, the current will be limited by space charge region formed with unlimited injected carriers. Although the condition that the amount of injected charge is greater than the device's transport ability is conventionally associated with Ohmic contact, the current in SCLC case does not obey the predictions from Ohm's law that varies linearly with the electric field F. For a metal-semiconductor-metal architecture in which the semiconductor has a thickness *d*, capacitance per unit area *C*, and dielectric relative permittivity  $\varepsilon_r$ , the charge *Q* of this sandwich-type capacitor (consider the semiconductor as a dielectric layer) gained per unit area is  $Q = CV = \varepsilon_0 \varepsilon_r \frac{V}{d}$ . Assuming that all gained charges will migrate from the injection electrode to the opposite electrode, the resulting current is  $j = Q/\tau_{device}$  where  $\tau_{device}$  is the time it takes the charges to travel through the device. Since the  $\tau_{device}$  can be gained as  $\tau_{device} = \frac{d}{\mu F} = \frac{d^2}{\mu V}$ , yielding the current and electric field. However, the current gained from this simplified calculation ignored the inhomogeneous of the electric field in the semiconductor (treated as dielectric layer), that is  $F(x) = \frac{3V}{2} \frac{V}{d} \sqrt{\frac{x}{d}}$ , and the corresponding charge concentration is  $n(x) = \frac{3\varepsilon_0 \varepsilon_r V}{4ed^2} \sqrt{\frac{d}{x}}$  with an average value of

$n = \frac{3}{2} \varepsilon_0 \varepsilon_r \frac{V}{ed^2}$  [29]. Therefore, a correction factor of 9/8 needs to be added according to the Mott-Gurney equation (Child's law) as [57]:

$$\mathbf{j} = \frac{9}{8}\varepsilon_0\varepsilon_r\frac{\mu F^2}{d} = \frac{9}{8}\varepsilon_0\varepsilon_r\mu\frac{V^2}{d^3}$$

(2.3.4)

Herein, since both the charge carrier concentration (not proven here) as well as the electric field contribute with linear dependencies on the applied voltage, the overall linearity is destroyed. However, the linearity can reflect in the measurable linear current-voltage relation in the semiconductor characterizations.

Two current limitations described above set clear a limits to the injection ability, i.e., the metalsemiconductor contact has either negligible contact resistance or significant contact resistance. However, the contact resistance has an exponential voltage dependence in reality, indicating that with the decrease of the electric field, the reduction of contact resistance is much stronger than the reduction of semiconductor layer resistance. As a consequence, the same device has different injection limitations in different voltage regimes: at low voltage, an injection limited current (ILC) is present, whereas at high voltage, a space charge limited current (SCLC) dominates [58].

#### 2.3.2 Charge injection mechanisms

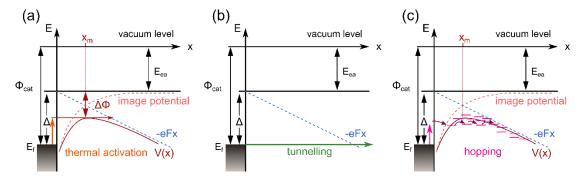

The intrinsic conductivity of an undoped semiconductor is typically low, indicating that, in fact, the intrinsic semiconductor is an insulator. Unlike inorganic semiconductors, which have narrow bandgaps (e.g., crystalline silicon has bandgap value of 1.1 eV with an absorption edge of 1100 nm) and large relative dielectric constants ( $\epsilon_r$ =11) to yield free electrons and holes with negligible Coulomb effects at room temperature, the bandgap of an intrinsic semiconductor is usually larger than 2 eV and the dielectric constant is as small as 3-4 [59]. Therefore, the excess charges generated by optical excitation have comparable large Coulomb attraction in between the hole and electron, resulting Coulomb-bound electron-hole pairs with non-negligible binding energy (normally 0.5-1.0 eV) instead of free charge carrier. Therefore, unless the semiconductor is doped (will be discussed in the following section), the free charge carriers have to be injected from electrodes [60]. To overcome the injection barrier mentioned above in Fig. 2.3.2, either tunneling or thermal activation is needed in principle.

Figure 2.3.2: Schematic of electron injection from the electrode to the semiconductor via (a) Richardson-Schottky thermionic emission, (b) Fowler-Nordheim tunneling, i.e., filed emission, and (c) thermally activated

injection. Here, x is the distance from the electrode while the blue dash line (-eFx) donates potential energy due to the electric field F. Redraw from [29].

**Richardson-Schottky thermionic injection** Modeling the Schottky effect, or also known as field enhanced thermionic emission, by the Richardson equation gives the Richardson-Schottky thermionic injection, in which there is the image-force-induced lowering of the barrier potential for charge carrier injection in the presence of an external electric field. Considering electron injection, the potential barrier leaving for thermal excitation is the difference between the work function of cathode and electron affinity of semiconductor  $\Delta = \phi_{cat} - E_{ea}$  as indicated in Fig. 2.3.2 (a) [61]. When an electron is at a distance *x* from the electrode, a positive image charge will then be induced on the electrode surface, creating attractive force (image force) toward the electrode. This image Coulomb force *K* is between the real electron at the distance *x* and its image charge at the distance *x*, given by:

$$K = -\frac{e^2}{4\pi\varepsilon_0\varepsilon_r(2x)^2} = -\frac{e^2}{16\pi\varepsilon_0\varepsilon_r x^2}$$

(2.3.5)

and image potential  $\Phi_{image}$  can be given as:

$$\phi_{image} = \int_{\infty}^{x} k dx = -\frac{e^2}{16\pi\varepsilon_0\varepsilon_r x}$$

(2.3.6)

shown as a light red dash line in Fig. 2.3.2 (a). When an external field F is applied, the true potential barrier which results from the superposition of the external and the image charge potential is smaller than the initial potential barrier, enabling the electrons being injected from the metal with sufficient thermal energy (Fig. 2.3.2 (a)). The total potential follows:

$$V(x) = (\phi_{cat} - E_{ea}) + \phi_{image} - eFx \qquad (2.3.7)$$

in which involves the potential barrier. By calculating the condition of dV(x)/dx = 0, the minimum of the total potential can be gained at a certain distance  $X_m$  from the interface:

$$X_m = \sqrt{\frac{e}{16\pi\varepsilon_0\varepsilon_r F}}$$

(2.3.8)

at which distance the injection barrier is lowered maximum by  $\Delta \Phi$ :

$$\Delta \phi = \sqrt{\frac{eF}{4\pi\varepsilon_0\varepsilon_r}} = 2FX_m \tag{2.3.9}$$

And the injection current is predicted to be:

$$j_{RS} \propto T^2 \exp(-\frac{\Delta - \Delta \phi}{k_B T})$$

(2.3.10)

with temperature dependence.

Herein, the inelastic scattering is ignored in the potential barrier for kicking out the possible recombination during the injection process, requiring a long intermolecular spacing and appropriate electric field (< 1 MV/cm) [62][63].

**Fowler-Nordheim tunneling injection** As mentioned before, the injection barrier between the electrode and semiconductor is identified with the work function of the metal. With the presence of a strong electric field (~1 MV/cm), electrons can tunnel from the Fermi level of the metal through a triangular barriers into the vacuum as a one-step tunneling process, also known as field emission (Fig. 2.3.2 (b)). Neglecting the Schottky effect, which will be introduced in the next chapter, Fowler and Nordheim predicted the injection current with the filed dependence as [64]:

$$j_{FN}(F) \cong F^2 \exp(-\frac{4\sqrt{2m * \emptyset^3}}{3\hbar eF})$$

(2.3.11)

where  $\hbar$  is the reduced Planck constant. Such field emission is temperature-independent and yields a straight with a slope of proportional to  $\Phi^3$  when plotting  $ln(j_{NF}/F^2)$  versus I/F. However, the Fowler-Nordheim equation ignores the image potential, which is then only applicable when the injection barrier is much higher than an image charge that the injection is into the vacuum, obviously not the case for intrinsic organic semiconductor. Furthermore, for getting rid of the inelastic scattering, electron in organic molecular semiconductor needs to tunnel the distance that is several times of the intermolecular spacing, making it impossible even for molecular crystals.

**Thermally activated injection** In a disordered organic semiconductor, the models of either Richardson-Schottky thermionic injection or Fowler-Nordheim tunneling injection have limited applicability since both of them are driven from a view to crystalline, inorganic semiconductors. Therefore, a model shown in Fig. 2.3.2 (c) is developed by considering the image charge at the electrode, the charge carrier hopping transport, and the energetic disorder in molecules comprehensively. As Gartstein and Conwell state, with an initial thermal activation, an electron at the Fermi level of the electrode can "jump" to the tail state of the density of states (DOS) distribution of transport sites of the organic semiconductor [65][59]. As long as there is a neighboring hopping site with lower energy, the injected carrier at the tail state cannot relax back to the initial site close to the metal, or recombines with its image charge in the electrode, but continue motions by hopping transport as discussed in Sec. 2.2.2.

### 2.4 Doping

To increase the number of free charge carriers as well as to improve the injection efficiency, introducing dopants that act as electron donors or acceptors in the organic semiconductor is a common way. By doing so, the conductivity of a semiconductor, which is the sum of hole (+) and electron (-) conductivity that comes from the product of respective charge carrier density and the mobility as  $\sigma = n_+e\mu_+ + n_-e\mu_-$ , increases. Furthermore, the injection barrier is narrowed after doping, thus more charge carriers can be injected from the electrode and the injection current can be increased.

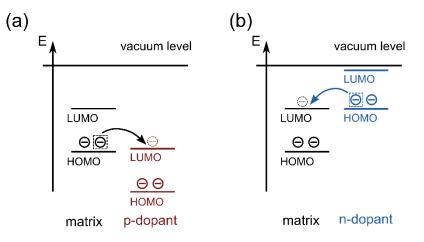

A simple doping mechanism is illustrated in Fig. 2.4.1 with simplified one-electron images. In the intrinsic organic semiconductor (matrix molecules) with filled HOMO and empty LUMO, it behaviors as the host which can either accept an electron or donate one, depends on the band energy levels of the dopant. For p-type doping, the LUMO level of p-dopants with high electron affinity is close to the HOMO of the host matrix molecules. Therefore, an electron from the filled HOMO of

the host can transfer to the empty LUMO of the dopant, creating a free hole in the host, increasing the hole density, and lowering the Fermi level towards the HOMO of the matrix molecules. The p-dopants in this case act as electron acceptors. Similar to the n-type doping with n-dopants that act as electron donors. Since the filled HOMO level of n-dopants is close to the empty LUMO of the matrix molecules, an electron can transfer to the LUMO of the host as a new free charge carrier in the organic semiconductor. The n-dopants are electron donors, leading to an increase of electron density and raising the Fermi level of the host toward its LUMO.

Figure 2.4.1: Schematic of the molecular orbital levels of organic molecules (matric) and dopants for (a) p-type doping and (b) n-type doping.

In this thesis, doping is achieved by co-evaporation of matrix molecules and dopant molecules at the same. The p-dopant is 2,2'-(perfluoronaphthalene-2,6-diylidene)dimalononitrile (F<sub>6</sub>-TCNNQ) while the n-dopant is the alkali metal of Cs [66]. Both experimental and material details will be presented in Chapter 5.

## **Chapter 3**

## **Organic junctions and devices**

This chapter introduces the fundamental concepts of junction and related semiconductor devices in organic electronics, especially in organic light-emitting diode (OLED). Regarding the metalsemiconductor junction: a brief introduction of Ohmic contacts, ideal Schottky contacts, and Schottky contacts with surface states that result in Fermi level pinning is given in Sec. 3.1. Following that is a further investigation, in Sec. 3.2, about metal-oxide-semiconductor capacitor with three different operation conditions and corresponding different capacitance behaviors. Finally in Sec. 3.3, a discussion about p-n junctions, p-i-n junctions as well as OLEDs based on these two concepts is presented with their specific electrical properties.

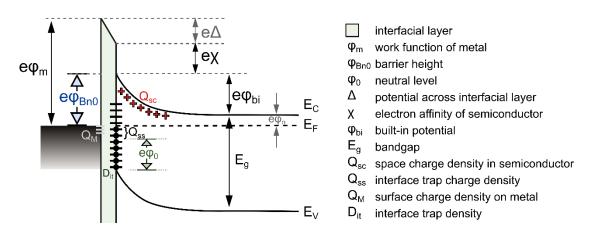

### 3.1 Metal-semiconductor junction

As electrical metal-semiconductor junction is formed when the metal (electrode) makes contact with a semiconductor. Depending on the characteristics of the interface, the metal-semiconductor junction can behave either as an Ohmic contact or a Schottky junction barrier. Both of them have band bending near the interfacial energy levels, but in the opposite shifting directions [67]. For the Ohmic contact, with the injection of charges, the energy levels of the semiconductor molecules will shift to form space charge layer, which creates what is referred to as band bending. The Ohmic contact has strict requirements for the interface energy level (work function of the metal needs to be larger than the Fermi level of the p-type semiconductor, or smaller than the n-type semiconductor) that often requires doped organic semiconductors for organic systems. The Schottky junction is of importance, especially the accompanying barrier which is responsible for controlling the current as well as its capacitance behavior. Although a brief overview of the metal-semiconductor interface and the related different injection mechanisms has been given in Sec. 2.3, a more detailed discussion regarding the thermal equilibrium of Fermi levels and interface states will be held in this section.

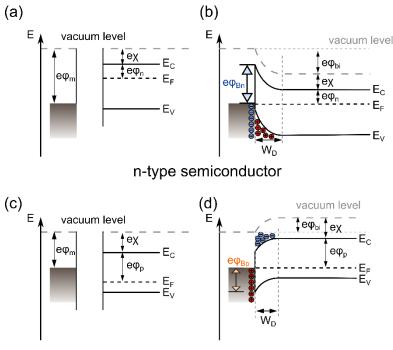

### 3.1.1 Schottky junction

For the ideal Schottky junction without interface states and interface dipoles, the formation process can be illustrated as in Fig. 3.1.1 with an example of a metal with high work function  $\Phi_m$  and an n-type semiconductor with conduction band energy  $E_C$ , valence band energy  $E_V$ , and Fermi energy  $E_F$  [68][69].

p-type semiconductor

Figure 3.1.1: The formation of a Schottky junction with (a), (b) n-type semiconductor and (c), (d) p-type semiconductor. Partly redraw from [69].

Before the contact (Fig. 3.1.1 (a)), the metal has the work function  $e\varphi_m$ , while the semiconductor has the electron affinity of  $E_{ea}$  (=  $e\chi$ ), leaving the energy difference between  $E_c$  and Fermi level to be  $\Delta_n$ (= $e\varphi_n$ ). The potential difference between the work function of the metal ( $\varphi_m$ ) and the semiconductor ( $\chi + \varphi_n$ ) is the contact potential. When the metal and the semiconductor are connected (Fig. 3.1.1 (b)), for example through an external wire connection, electrons will diffuse from the semiconductor into the metal until thermal equilibrium is established with the line up of both Fermi levels. Therefore, the Fermi level of the semiconductor is lowered by an amount equal the value of the contact potential. Since the metal then has excess electrons that are now missing in the semiconductor with a width of  $W_d$ , associated with a built-in field and a resulting built-in potential drop of  $\varphi_{bi}$ . This region is the depletion region which will be discussed later. As mentioned in Sec. 2.3.1, the barrier height is the difference between the work function of the metal and electron affinity of semiconductor, given by:

$$e\varphi_{Bn} = e(\varphi_m - \chi) \tag{3.1.1}$$

However, this simple expression normally cannot be realized experimentally due to the unavoidable interface states, dipoles, or image-force lowering introduced in Sec. 2.3.2. Furthermore, a similar but opposite charge region and band bending direction for Schottky junction with p-type semiconductor is simply shown in Fig. 3.1.1 (c) before contact and (d) with contact.

**Depletion region** When the Schottky junction is formed between the metal and the n-type semiconductor (as the example), the Fermi level of the semiconductor is far below the conduction band level due to the depletion region where there is lack of electrons (excess of equal positive charge). This difference will reduce with the distance from the junction until the n-type semiconductor returns back to charge-neutral condition with  $\Delta n$  (=eqn) as before contact was made.

The band change across the depletion region is the band bending for the Schottky junction. Since the energy relationship in the thermal equilibrium junction is defined, the width of depletion region  $W_d$  under an external applied voltage V can be gained by solving the Poisson equation [29][69]:

$$\frac{d^2\varphi}{dx^2} = -\frac{eN_d}{\varepsilon_0\varepsilon_r} \tag{3.1.2}$$

with the abrupt boundary condition ( $N_d$  is the charged impurities of donor), giving:

$$W_D = \sqrt{\frac{2\varepsilon_0 \varepsilon_r}{eN_d} (\varphi_{bi} - V - \frac{k_B T}{e})}$$

(3.1.3)

where the  $k_BT/e$  term arises from the majority-carrier contribution in addition to the impurity concentration  $N_D$  (here for the n-type semiconductor).

The space charge Q<sub>sc</sub> per unit area of the semiconductor is:

$$Q_{sc} = eN_D W_D = \sqrt{2e\varepsilon_0\varepsilon_r N_D(\varphi_{bi} - V - \frac{k_B T}{e})}$$

(3.1.4)

and the capacitance of depletion region per unit area  $C_D$  can be written as:

$$\frac{1}{C_D^2} = \left(\frac{W_D}{\varepsilon_0 \varepsilon_r}\right)^2 = \frac{2(\varphi_{bi} - V - \frac{k_B T}{e})}{e\varepsilon_0 \varepsilon_r N_D}$$

(3.1.5)

leading to a straight slope for extracting  $\varphi_{bi}$  and thus  $\varphi_{Bn} (\varphi_{bi} = \varphi_{Bn} - \varphi_n)$  by plotting  $1/C_D^2$  versus voltage if  $N_D$  is constant throughout the depletion region.

**Charge transport** Although several injection mechanisms with different current models have been discussed in Sec. 2.3.2, the current conduction mechanism across a Schottky junction is generally governed by the thermionic emission model with image force, yielding [70]

$$j = j_0 (\exp \frac{eV}{k_B T} - 1)$$

(3.1.6)

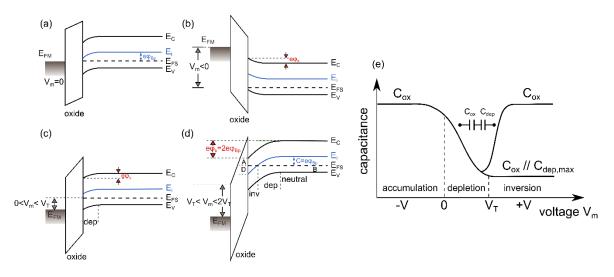

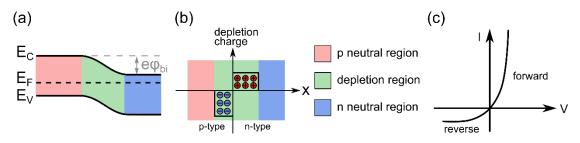

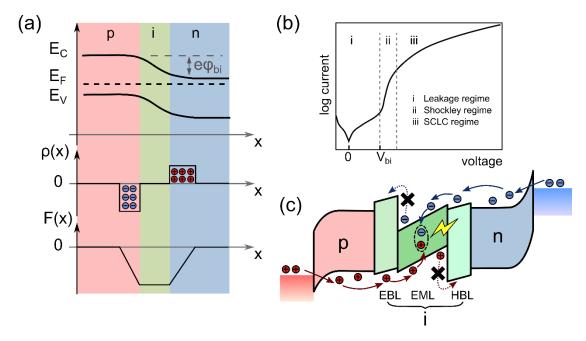

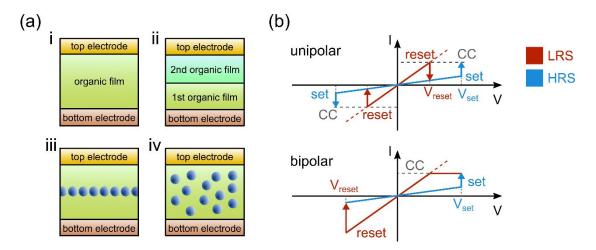

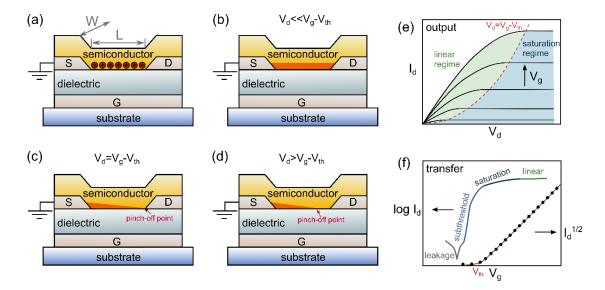

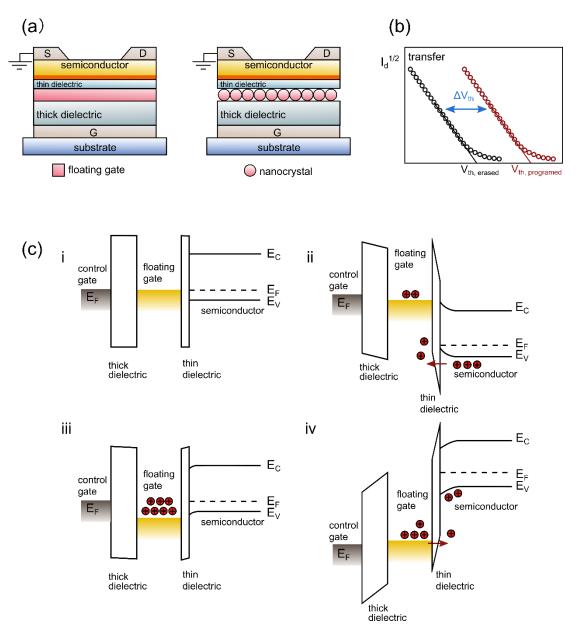

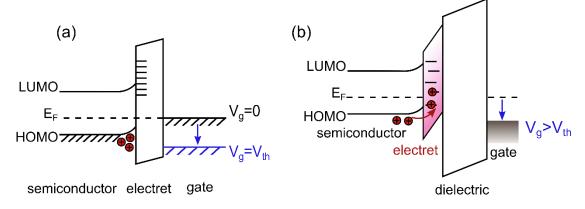

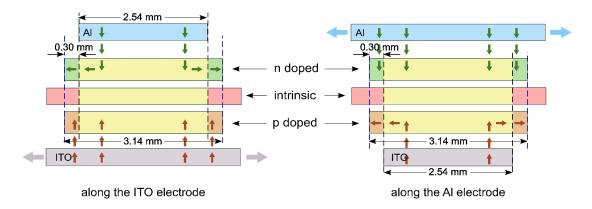

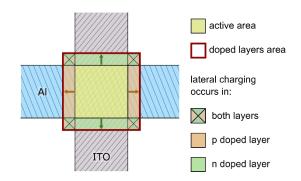

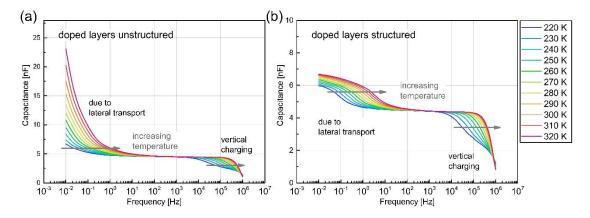

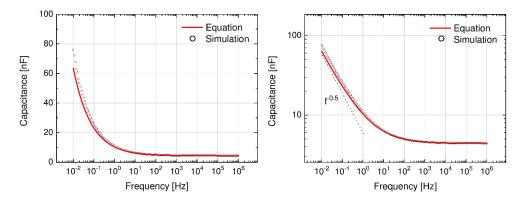

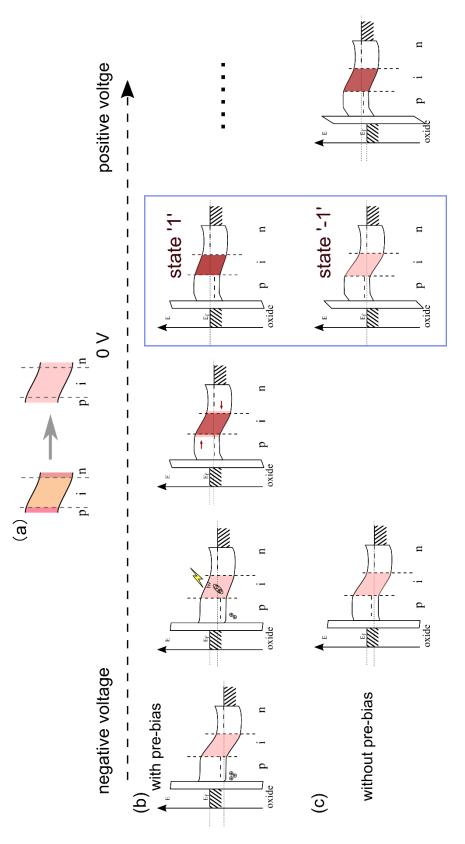

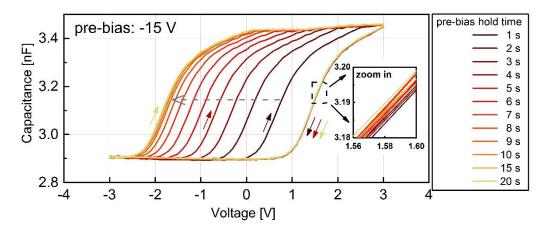

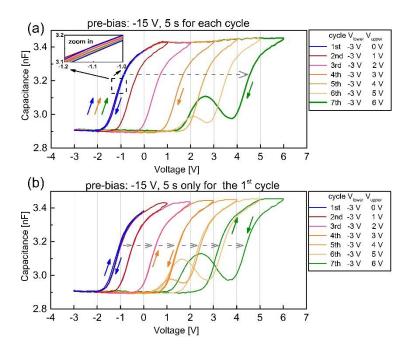

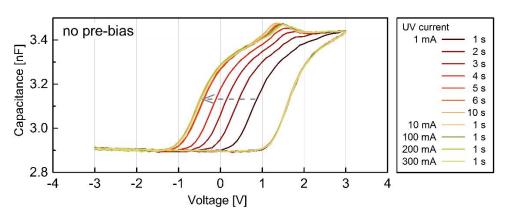

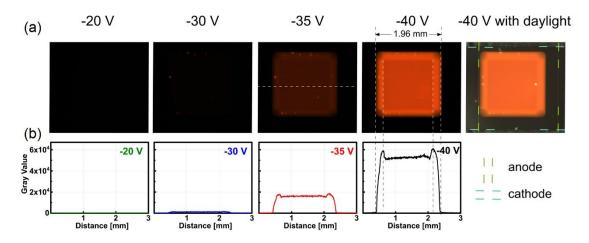

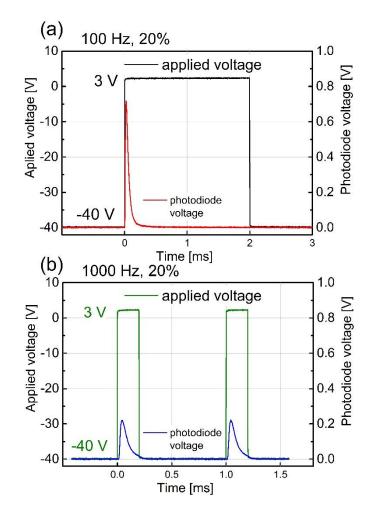

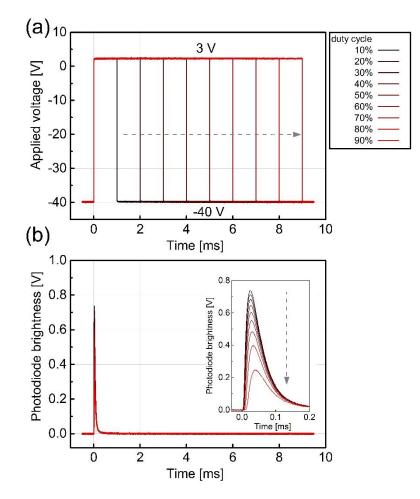

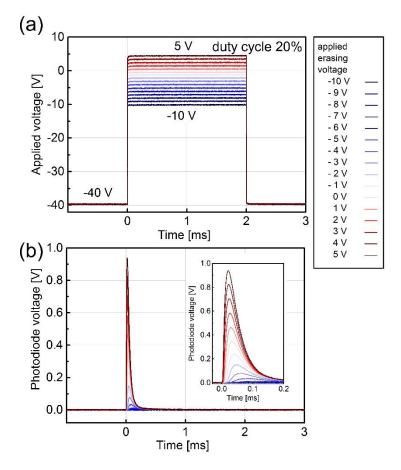

where  $j_0$  is the saturation current.