# Interaction of Hardware Transactional Memory and Microprocessor Microarchitecture

#### Dissertation

to obtain the academic degree Doktor rerum naturalium (Dr. rer. nat.)

presented to Technische Universität Dresden Faculty of Computer Science

by

Stephan Diestelhorst stephan.diestelhorst@gmail.com

born 12th September 1981 in Halle(Saale), Germany

Supervisor: Prof.Christof Fetzer

Defense: 28th March 2019

Cambridge, 9th June 2019

Copyright 2019 Stephan Diestelhorst. All rights reserved.

Cover photo adapted from "AMD Ryzen 5 2600" by Fritzchens Fritz available as Public Domain<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>https://www.flickr.com/photos/130561288@N04/47049179901

# Contents

| Lis | t of I                                          | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | vii                                                                                                                                                                                |  |  |  |  |

|-----|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Lis | List of Tables                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                    |  |  |  |  |

| 1   | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | oduction         Context         Transactional Memory         Thesis         Contributions         Terminology         Outline                                                                                                                                                                                                                                                                                                                                                                    | 1<br>2<br>4<br>5<br>7<br>7                                                                                                                                                         |  |  |  |  |

| 2   |                                                 | 2.1.4OrganisationTransactional Memory Research2.2.1Software Transactional Memory2.2.2Lock Elision and Thread-Level Speculation2.2.3Hardware Transactional Memory2.2.4Transactions as Standard Synchronisation Primitive2.2.5Virtualising Transactional Memory2.2.6Improving Commit Path Performance - Eager Logging Unbounded TM2.2.7Micro-Architecture of Transactional Memory Implementations2.2.8Instruction-Set Design for Hardware Transactional Memory2.2.9Other Concerns: Energy and GPUs  | <b>9</b><br>9<br>10<br>11<br>12<br>12<br>14<br>15<br>16<br>16<br>18<br>18<br>21<br>22<br>23<br>26                                                                                  |  |  |  |  |

|     | 2.3<br>2.4                                      | 2.2.12 Composite Transactional Memory2.2.13 Concepts and Theory of TMIndustry Adoption2.3.1 Early Industry Approaches2.3.2 First Industrial Silicon: Sun Rock and Azul2.3.3 IBM's HTM: A Bouquet of Architectures and Microarchitectures2.3.4 Intel TSX: (Semi-)Transparent Hardware Lock Elision2.3.5 Comparison of Commercial HTMsTransactional Memory Use-Cases2.4.1 Algorithms and Micro-Benchmarks2.4.2 Other Use Cases2.4.3 Language Support2.4.4 Benchmark Suites2.4.5 Application Studies | <ul> <li>30</li> <li>31</li> <li>32</li> <li>32</li> <li>32</li> <li>34</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> <li>39</li> <li>42</li> <li>42</li> <li>47</li> </ul> |  |  |  |  |

|     | 2.5                                             | 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49                                                                                                                                                                                 |  |  |  |  |

|   | 2.6  | 2.5.1 CPU Architecture and Micro-Architecture       49         2.5.2 Simulation       50         Summary       53         2.6.1 HTM Summary       53 |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

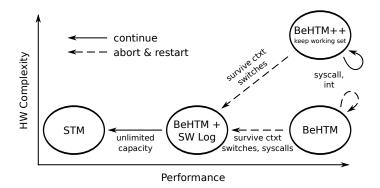

| 3 | Inst | 2.6.2 Computer Architecture and Simulation                                                                                                           |

|   | 3.1  | Introduction                                                                                                                                         |

|   |      | 3.1.1 Architectural Concepts and Functionality of HTM                                                                                                |

|   | 3.2  | HTM Instruction Set Architecture Design                                                                                                              |

|   |      | 3.2.1 ASF 1: A Precursor to Full BeHTM 59                                                                                                            |

|   |      | 3.2.2 ASF 2: AMD's Hardware Transactional Memory Proposal 60                                                                                         |

|   |      | 3.2.3 Conflict Detection and Transaction Aborts                                                                                                      |

|   |      | 3.2.4 Nesting of Transactions                                                                                                                        |

|   |      | 3.2.5 Non-transactional Memory Accesses                                                                                                              |

|   |      | 3.2.6 Non-transactional Access Challenges                                                                                                            |

|   |      | 3.2.7 Limited Register Checkpointing 65                                                                                                              |

|   |      | 3.2.8 Interactions with the Memory Model                                                                                                             |

|   |      | 3.2.9 Instruction Support and Non-Conflict Sources of Aborts                                                                                         |

|   | 3.3  | Language Integration Prototype                                                                                                                       |

|   | 3.4  | Incremental Adaptations of ASF                                                                                                                       |

|   |      | 3.4.1 Inverted Transactional Semantics                                                                                                               |

|   |      | 3.4.2 Signalling Transactional Problems 73                                                                                                           |

|   | 3.5  | Capacity and Architectural Progress                                                                                                                  |

|   | 3.6  | Summary                                                                                                                                              |

| _ |      |                                                                                                                                                      |

| 4 |      | roarchitectural Implementation Details of HTM 77                                                                                                     |

|   | 4.1  | Introduction                                                                                                                                         |

|   |      | 4.1.1 Processor Microarchitecture                                                                                                                    |

|   |      | 4.1.2 Recovery From Out-Of-Order Misspeculation                                                                                                      |

|   |      | 4.1.3 Coherency Protocol Basics                                                                                                                      |

|   | 4.2  | Key Microarchitectural HTM Mechanisms    81                                                                                                          |

|   |      | 4.2.1 Data Versioning                                                                                                                                |

|   |      | 4.2.2 Conflict Detection                                                                                                                             |

|   |      | 4.2.3 Multi-Word Atomic Store Visibility                                                                                                             |

|   |      | 4.2.4 Rollback of Transactional State                                                                                                                |

|   | 4.3  | Basic Implementation Variants    87                                                                                                                  |

|   |      | 4.3.1 Speculation Mechanism Reuse                                                                                                                    |

|   |      | 4.3.2 Cache-based Implementation                                                                                                                     |

|   |      | 4.3.3 LLB-based Implementation                                                                                                                       |

|   | 4.4  | Basic Pipeline and Out-of-Order Core integration    88                                                                                               |

|   |      | 4.4.1 Sequential ASF Semantics                                                                                                                       |

|   |      | 4.4.2 Speculative-region Flow                                                                                                                        |

|   |      | 4.4.3 Misspeculation                                                                                                                                 |

|   |      | 4.4.4 Abort Semantics                                                                                                                                |

|   |      | 4.4.5 Conflict Detection Handshake                                                                                                                   |

|   |      | 4.4.6 Abort Mechanics and Implications                                                                                                               |

|   |      | 4.4.7 Capacity Guarantees                                                                                                                            |

|   | 4.5  | Enhanced Pipeline Integration                                                                                                                        |

|   |      | 4.5.1 Overview                                                                                                                                       |

|   |      | 4.5.2 Extended Transactional Instruction Implementation                                                                                              |

|   |      | 4.5.3 Enhanced Transactional Flows                                                                                                                   |

|   |      | 4.5.4 Early Release of Transactional Data                                                                                                            |

|   | 4.6  | Alternative Microarchitectural Implementation Variants                                                                                               |

|   |      | 4.6.1 AMD Bulldozer Microarchitecture Integration Sketch                                                                                             |

|   |      | 4.6.2 Pipeline-only Implementation                                                                                                                   |

|   | 4.7  | High-level Interaction Between Microarchitecture and HTM 107                                                                                         |

|   |      | 4.7.1 Visible Microarchitecture Artifacts                                                                                                            |

|   | 4.8        | 4.7.2       Progress                                                          | . 110 |

|---|------------|-------------------------------------------------------------------------------|-------|

|   |            |                                                                               |       |

| 5 |            | olications and Evaluation of HTM                                              | 113   |

|   | 5.1        | Introduction                                                                  |       |

|   | 5.2        | Applications of HTM                                                           |       |

|   |            | 5.2.1 Direct HTM Usage                                                        |       |

|   |            | 5.2.2 Lock Elision                                                            |       |

|   |            | 5.2.3 Summary: Challenges of Lock Elision                                     |       |

|   | 5.3        | Evaluation Experiments                                                        |       |

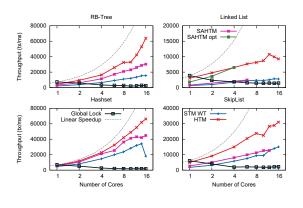

|   |            | 5.3.1 Integer Set Data Structures                                             |       |

|   |            | 5.3.2 STAMP: complex workloads                                                |       |

|   |            | 5.3.3 Memcached: elision and transaction characteristics                      |       |

|   |            | 5.3.4 Evaluation Summary                                                      |       |

|   | 5.4        | Simulator Implementation Details                                              |       |

|   |            | 5.4.1 Characteristics of Cycle-Level Simulator Environments                   | . 133 |

|   |            | 5.4.2 ASF Simulator Implementation                                            | . 139 |

|   |            | 5.4.3 Simplifications                                                         | . 148 |

|   |            | 5.4.4 Simulator Extensions and Complications                                  | . 149 |

|   | 5.5        | Summary                                                                       | . 151 |

|   |            |                                                                               | 4 - 0 |

| 6 |            | ensions and New Use-Cases                                                     | 153   |

|   | 6.1        | Introduction                                                                  |       |

|   | 6.2        | Ad-hoc Communicating Hardware Transactions                                    |       |

|   | 6.3        | Structured Communication: Delegation and Nesting in Best-Effort HTM           |       |

|   |            | 6.3.1 Transactional Channels                                                  |       |

|   |            | 6.3.2 Communication Patterns                                                  |       |

|   |            | 6.3.3 Aborts During Channel Operation                                         |       |

|   | <i>.</i> . | 6.3.4 Use Case: Memory Allocation                                             |       |

|   | 6.4        | Between All and Nothing–Versatile Aborts in Hardware Transactional Memory     |       |

|   |            | 6.4.1 Challenges                                                              |       |

|   |            | 6.4.2 Use-cases of Transactional Resurrection                                 |       |

|   |            | 6.4.3 Working Set Handling                                                    |       |

|   |            | 6.4.4 Evaluation                                                              |       |

|   | 6.5        | Summary                                                                       | . 167 |

| 7 | Out        | look: Semantic Challenges and Further Architectural Improvement Opportunities | 169   |

|   | 7.1        | Introduction                                                                  |       |

|   | 7.2        | Decomposing HTM and Lock Elision Primitives                                   | . 169 |

|   | 7.3        | Safely Accessing Timestamps in Transactions                                   |       |

|   |            | 7.3.1 Background                                                              |       |

|   |            | 7.3.2 Semantics of Time Stamps                                                |       |

|   |            | 7.3.3 Semantic Issues of Time Stamps in Transactions                          |       |

|   |            | 7.3.4 Supporting Time Stamps in Transactions                                  |       |

|   |            | 7.3.5 Outlook                                                                 |       |

|   |            | 7.3.6 Conclusion                                                              |       |

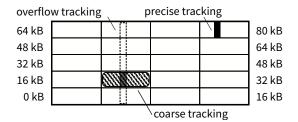

|   | 7.4        | Further HTM Ideas                                                             |       |

|   |            | 7.4.1 Roll-forward Mode                                                       |       |

|   |            | 7.4.2 Nested Abort Handlers                                                   |       |

|   |            | 7.4.3 Two-dimensional Tracking of Large Objects                               |       |

|   |            | 7.4.4 Tracking Large Objects in the TLB / Page Tables                         |       |

|   |            | 7.4.4 Hacking Large Objects in the TLB / Page Tables                          |       |

|   | 7.5        | HTM Product Experiences                                                       |       |

|   | 7.5<br>7.6 | Summary                                                                       |       |

|   | ,          |                                                                               | . 100 |

| 8  | Con   | clusions                                                                                            | 185 |

|----|-------|-----------------------------------------------------------------------------------------------------|-----|

|    | 8.1   | Summary                                                                                             | 185 |

|    | 8.2   | Thesis Evaluation                                                                                   | 186 |

|    | 8.3   | Critical Reflection                                                                                 | 187 |

|    | 8.4   | Current State of the Eco-System                                                                     | 188 |

|    | 8.5   | Post-thesis work                                                                                    | 189 |

| Bi | bliog | raphy                                                                                               | 191 |

| Α  | ASF   | 2.0 Specification                                                                                   | 225 |

|    | A.1   | Introduction                                                                                        | 232 |

|    | A.2   | Terminology                                                                                         | 238 |

|    | A.3   | CPUID Identification                                                                                | 241 |

|    | A.4   | Model-specific registers                                                                            | 243 |

|    | A.5   | Instructions                                                                                        | 245 |

|    | A.6   | Operation in ASF speculative regions                                                                | 254 |

|    | A.7   | ASF usage models                                                                                    | 262 |

| В  | Wor   | kshop Papers                                                                                        | 269 |

|    | B.1   | EPHAM 2008: Hardware Acceleration for Lock-Free Data Structures and Software-Transactio             | nal |

|    |       | Memory                                                                                              | 270 |

|    | B.2   | TRANSACT 2010: Implementing AMD's Advanced Synchronization Facility in an out-of-<br>order x86 core |     |

|    | B.3   | TRANSACT 2010: Compilation of Thoughts about AMD Advanced Synchronization Facility                  | 270 |

|    | D.5   | and First-Generation Hardware Transactional Memory Support                                          | 286 |

|    | B.4   | TRANSACT 2011: From Lightweight Hardware Transactional Memory to Lightweight Lock                   | 200 |

|    | D. 1  | Elision                                                                                             | 293 |

|    | B.5   | WTTM 2010: Sane Semantics of Best-effort Hardware Transactional Memory                              |     |

|    | B.6   | WTTM 2012: Safely Accessing Time Stamps in Transactions                                             |     |

|    | B.7   | TRANSACT 2015: Between All and Nothing–Versatile Aborts in Hardware Transactional                   | 001 |

|    | D.,   | Memory                                                                                              | 308 |

|    |       | memory                                                                                              | 500 |

# List of Figures

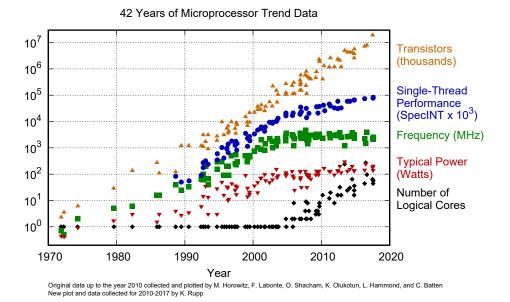

| 1.1  | Microprocessor trends since 1971                               | 2        |

|------|----------------------------------------------------------------|----------|

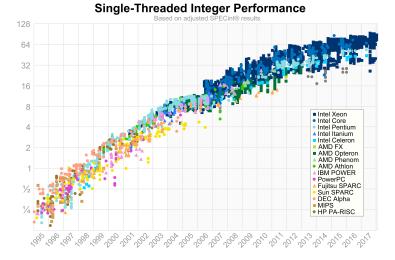

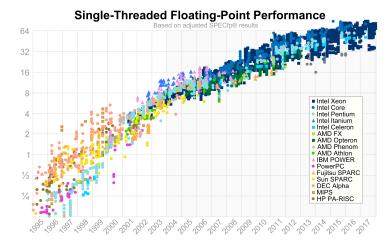

| 1.2  | Historical adjusted SPECint and SPECfp trends                  | 3        |

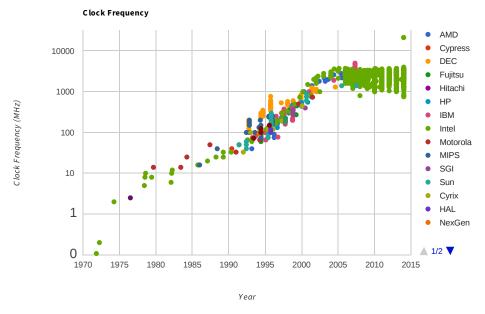

| 2.1  | History of CPU clock frequency scaling                         | 10       |

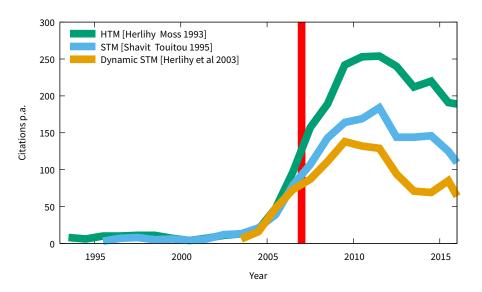

| 2.2  | Citation count of seminal transactional memory papers          | 11       |

| 2.3  | Examples of privatisation and publication of memory            | 13       |

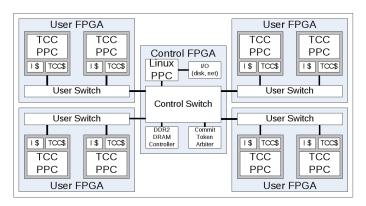

| 2.4  | Block diagram of the ATLAS system that implements TCC          | 17       |

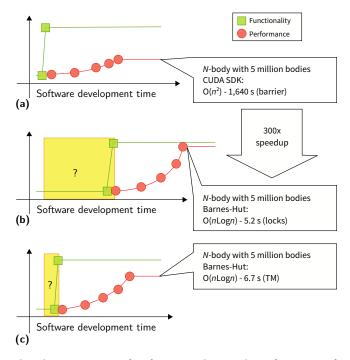

| 2.5  | Development time and performance on GPGPU                      | 24       |

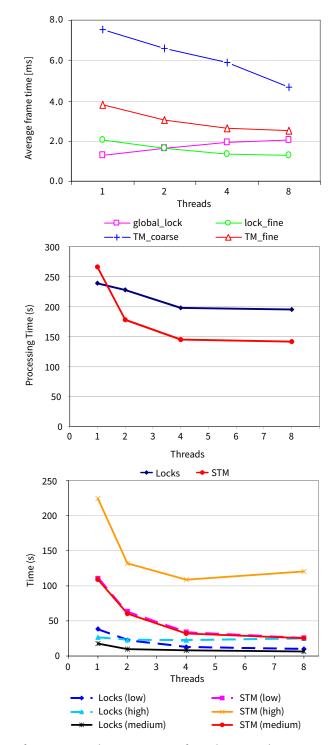

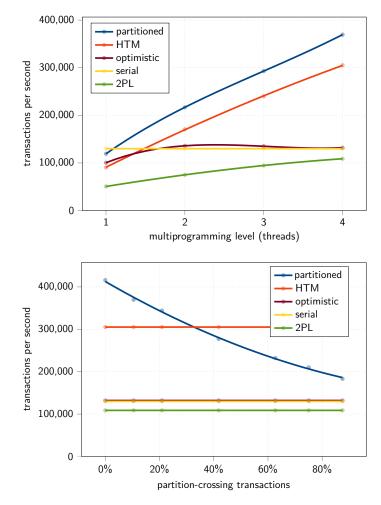

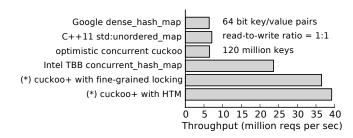

| 2.6  | Performance of various implementations of Quake game logic     | 44       |

| 2.7  | In-memory database performance with locks and HTM              | 47       |

| 3.1  | Composition of two-phase transactions                          | 60       |

| 3.2  | DCAS primitive implemented with ASF                            | 61       |

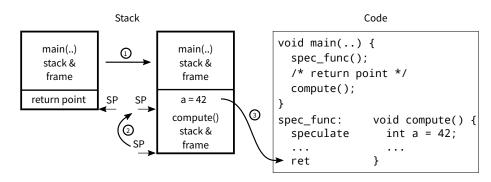

| 3.3  | Complications of non-transactional call stack modifications    | 64       |

| 3.4  | Prototyping ASF wrappers without compiler support              | 69       |

| 3.5  | Wrapper example showing double compare-and-swap                | 70       |

| 3.6  | Compiler output of the DCAS example                            | 70       |

| 3.7  | Unrolled DCAS example                                          | 71       |

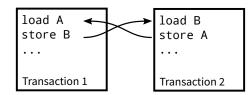

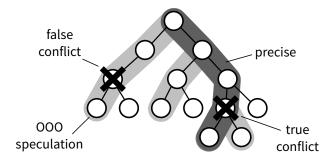

| 3.8  | Transactions with overlapping, conflicting access patterns     | 74       |

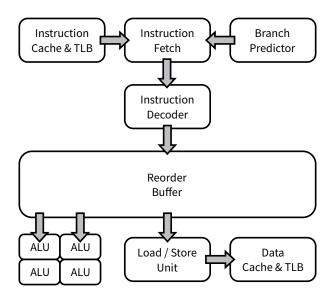

| 4.1  | Abstract pipeline diagram of an out-of-order microprocessor    | 80       |

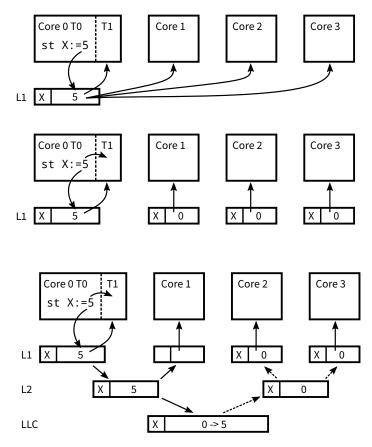

| 4.2  | Processor cores with multiple options for visibility of stores | 85       |

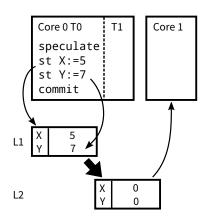

| 4.3  | Transactional stores must move as a unit                       | 86       |

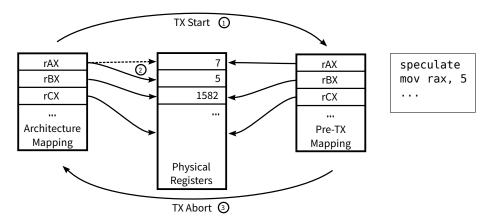

| 4.4  | Creating a backup copy of architectural registers              | 87       |

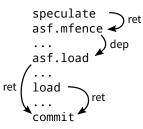

| 4.5  | Ordering ASF instructions with light-weight fences             | 89       |

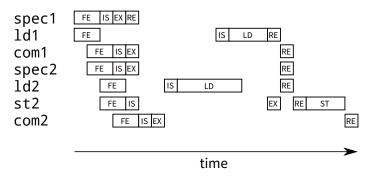

| 4.6  | Short transactions may execute concurrently                    | 90       |

| 4.7  | Two transactions executing in close proximity                  | 91       |

| 4.8  | Increased working set due to branch mis-speculation            | 91       |

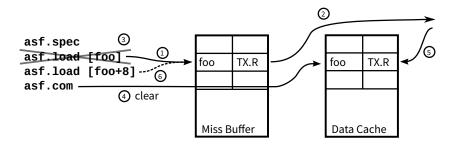

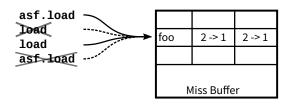

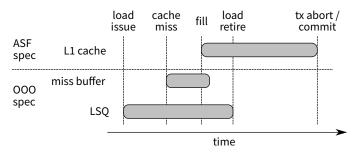

| 4.9  | Squashing ASF instructions during cache misses                 | 92       |

|      | Recomputing the ASF-ness of a miss buffer entry                | 93       |

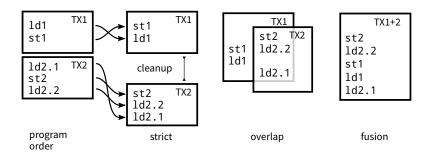

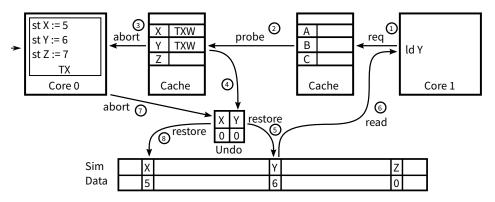

|      | Conflict tracking across mechanisms                            | 93<br>94 |

|      | Setting ASF bits for cache hits / misses                       | 94<br>94 |

|      |                                                                | 94<br>95 |

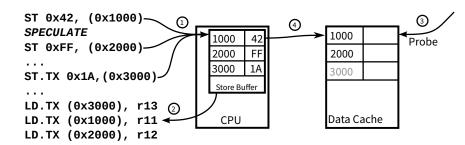

|      | Store-to-load forwarding and conflict detection in caches      |          |

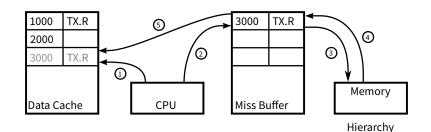

|      | Conflicting memory probes abort an ongoing transaction         | 95       |

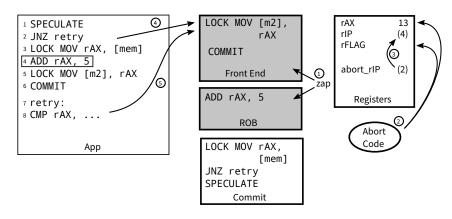

|      | Transaction aborts handled like branch mispredictions          | 96       |

|      | Splitting instructions into simpler $\mu$ ops                  | 97       |

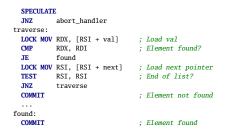

|      | Linked-list traversal showing working set growth               | 97       |

|      |                                                                | 99       |

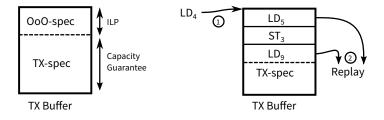

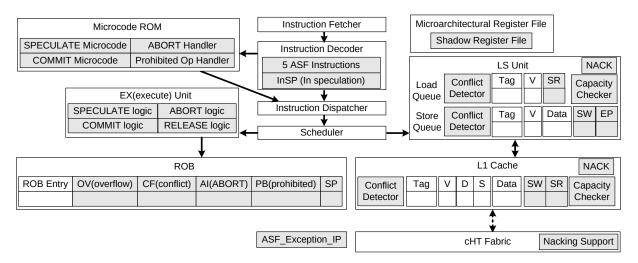

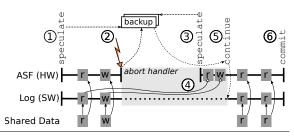

|      | Extending an out-of-order core for transactional memory        |          |

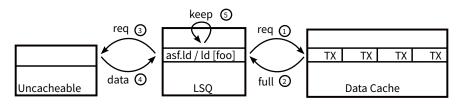

|      | Using the load/store queue as additional storage               |          |

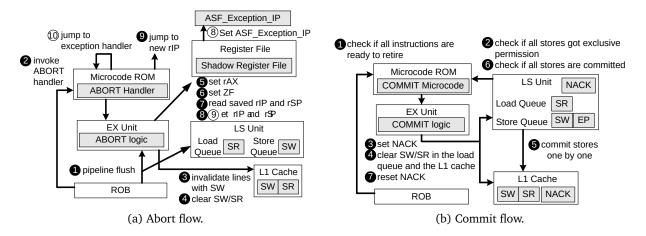

|      | Aborting and committing speculative regions                    |          |

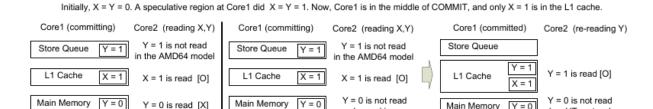

| 4.22 | Non-atomic commits when tracking transactional stores          | 103      |

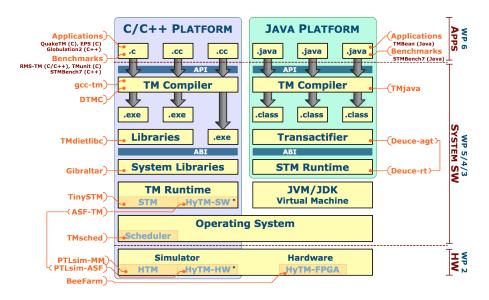

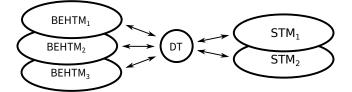

| 5.1  | The VELOX hardware and software stack                          |          |

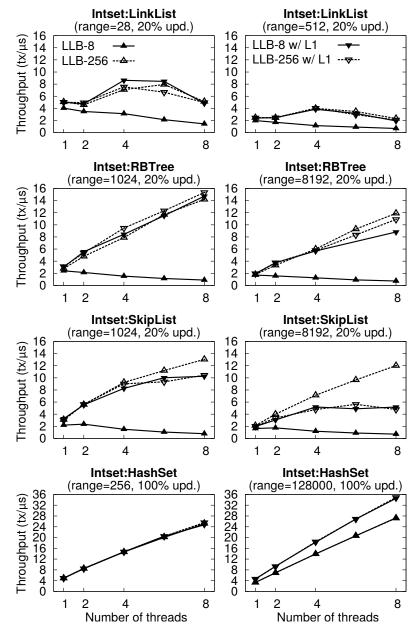

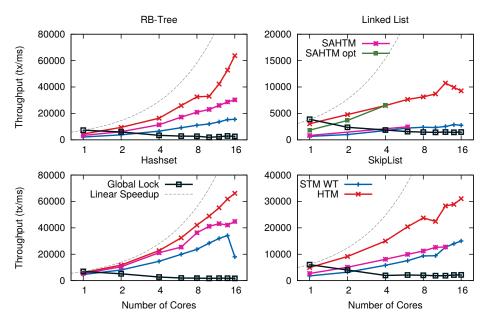

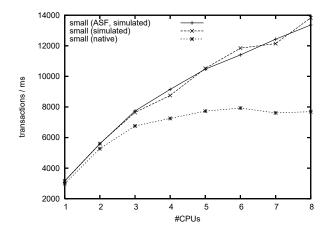

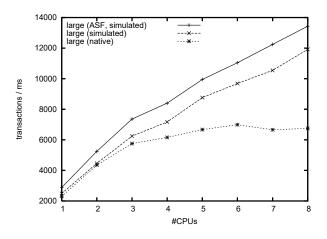

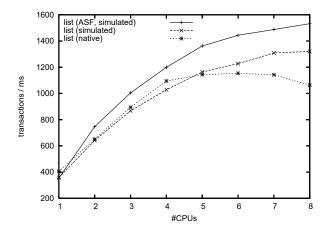

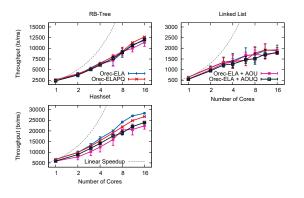

| 5.2  | Scalability of IntegerSet with ASF                             |          |

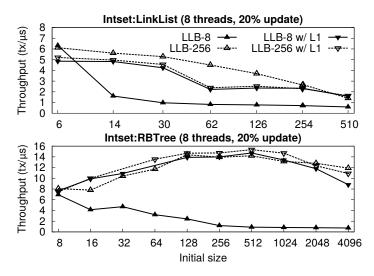

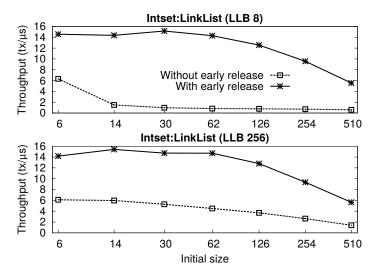

| 53   | Influence of ASF capacity on throughput                        | 123      |

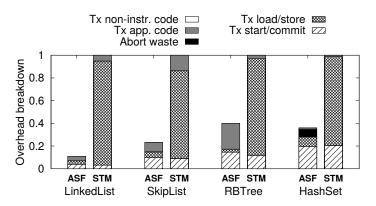

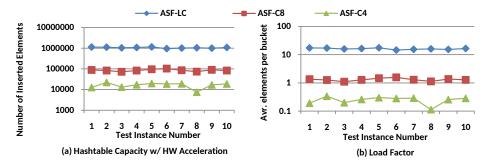

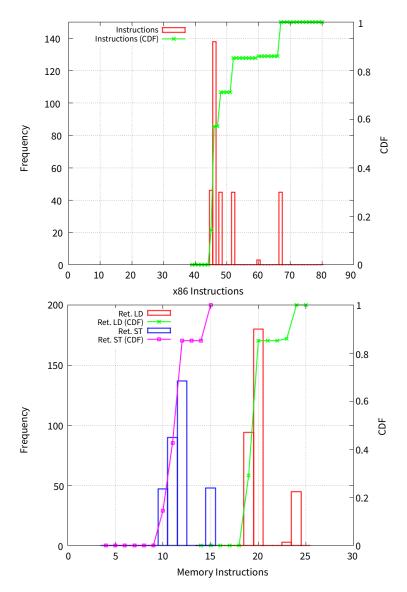

| 5.5Single-thread overhead details for ASF-TM1235.6Performance robustness of different ASF implementations1245.7PTLsim simulation accuracy for STAMP1245.8Scalability of applications with four ASF implementations1255.9Abort rates of applications with four ASF implementations1275.10Scalability of ASF design options1285.11Execution time breakdown of the STAMP applications1285.12Performance of various lock elision mechanisms in memcached1295.13Characteristics of elided critical sections in memcached1305.14Instruction breakdown sections in memcached1315.15Key core-side code used in the PTLsim load path1355.16Functions and flow in the memory system of PTLsim1365.19Path for stores becoming visible in memory in PTLsim1395.20Store behaviour in Marss86 compared to PTLsim1405.21Interface of data versioning and conflict detection in Marss861405.22Interface of the ASF_implementation1425.25Interface of the ASF_MOESILogic class1445.26Marss86 ASF coherence logic for conflict detection1425.27Interface of the ASF_MOESILogic class1466.1Using non-transactional loads and stores to communicate1546.3Sending long messages by chunking1566.4Multiple transactions using a single service thread1566.5TXChannel state transitions156<                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

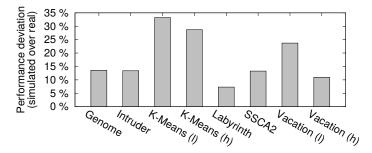

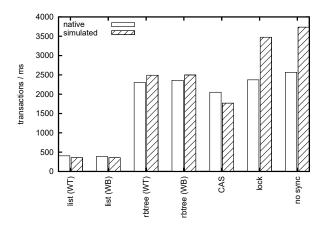

| 5.7PTLsim simulation accuracy for STAMP1245.8Scalability of applications with four ASF implementations1255.9Abort rates of applications with four ASF implementations1275.10Scalability of ASF design options1285.11Execution time breakdown of the STAMP applications1285.12Performance of various lock elision mechanisms in memcached1295.13Characteristics of elided critical sections in memcached1305.14Instruction breakdown sections in memcached1315.15Key core-side code used in the PTLsim load path1355.16Functions and flow in the memory system of PTLsim1365.17Core logic and memory system glue logic used in Marss861375.18Key parts of the redesigned memory system in Marss861385.19Path for stores becoming visible in memory in PTLsim1405.21Graphical overview of the ASF implementation in Marss861405.22Interaction of pipeline and ASF for an aborting transaction1405.23Interface of data versioning and conflict detection in Marss861415.24Pipeline and data versioning layer interaction1425.25Interface of the ASF_MOESILogic class1446.1Using non-transactional loads and stores to communicate1546.2Sending and receiving small messages with ASF1556.3Sending long messages by chunking1566.4Multiple transactions using a single service thread156 </td                                                            |

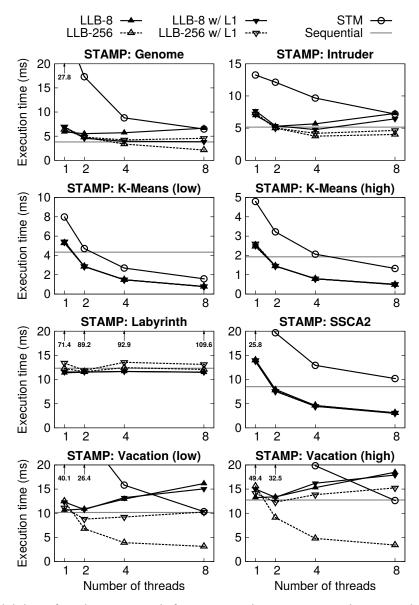

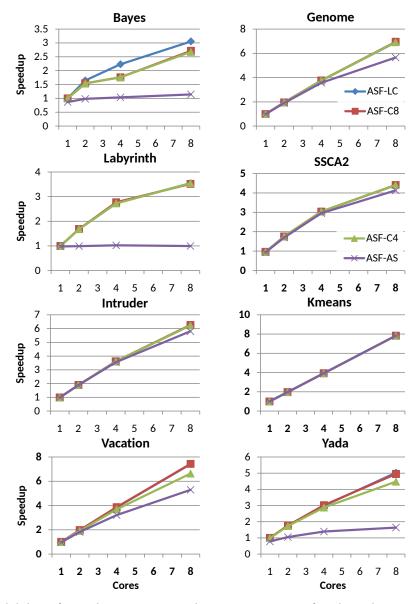

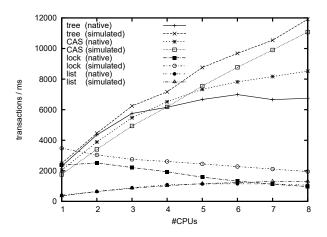

| 5.8       Scalability of applications with four ASF implementations       125         5.9       Abort rates of applications with four ASF implementations       127         5.10       Scalability of ASF design options       128         5.11       Execution time breakdown of the STAMP applications       128         5.12       Performance of various lock elision mechanisms in memcached       129         5.13       Characteristics of elided critical sections in memcached       130         5.14       Instruction breakdown sections in memcached       131         5.15       Key core-side code used in the PTLsim load path       135         5.16       Functions and flow in the memory system of PTLsim       136         5.17       Core logic and memory system glue logic used in Marss86       137         5.18       Key parts of the redesigned memory system in Marss86       138         5.19       Path for stores becoming visible in memory in PTLsim       139         5.20       Store behaviour in Marss86 compared to PTLsim       140         5.21       Graphical overview of the ASF implementation in Marss86       140         5.22       Interface of data versioning and conflict detection in Marss86       141         5.24       Pipeline and data versioning layer interaction       142         5.25 |

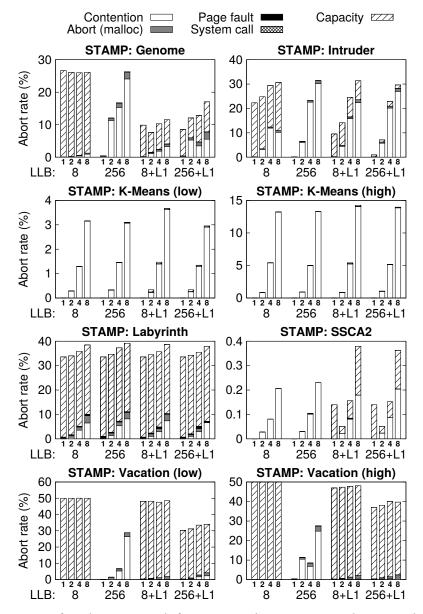

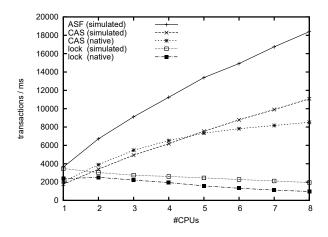

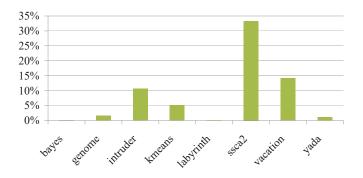

| 5.9Abort rates of applications with four ASF implementations1275.10Scalability of ASF design options1285.11Execution time breakdown of the STAMP applications1285.12Performance of various lock elision mechanisms in memcached1295.13Characteristics of elided critical sections in memcached1305.14Instruction breakdown sections in memcached1315.15Key core-side code used in the PTLsim load path1355.16Functions and flow in the memory system of PTLsim1365.17Core logic and memory system glue logic used in Marss861375.18Key parts of the redesigned memory system in Marss861385.19Path for stores becoming visible in memory in PTLsim1405.21Graphical overview of the ASF implementation in Marss861405.22Interface of data versioning and conflict detection in Marss861415.24Pipeline and data versioning layer interaction1445.25Interface of the ASF_MOESILogic class1445.26Marss86 ASF coherence logic for conflict detection in Marss861445.27Interface of the ASF_MOESILogic class1445.26Marss86 ASF coherence logic for conflict detection1455.27Interface of the ASF_MOESILogic class1466.1Using non-transactional loads and stores to communicate1546.2Sending and receiving small messages with ASF1556.3Sending long messages by chunking1566.4Multi                                                                        |

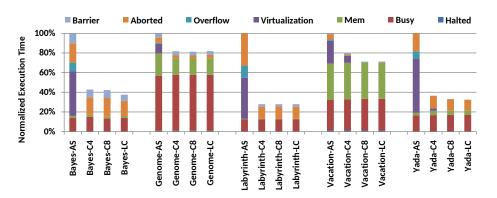

| 5.11 Execution time breakdown of the STAMP applications1285.12 Performance of various lock elision mechanisms in memcached1295.13 Characteristics of elided critical sections in memcached1305.14 Instruction breakdown sections in memcached1315.15 Key core-side code used in the PTLsim load path1355.16 Functions and flow in the memory system of PTLsim1365.17 Core logic and memory system glue logic used in Marss861375.18 Key parts of the redesigned memory system in Marss861385.19 Path for stores becoming visible in memory in PTLsim1395.20 Store behaviour in Marss86 compared to PTLsim1405.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1425.25 Interface of data versioning and conflict detection in Marss861415.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1566.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                      |

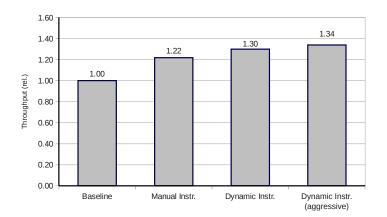

| 5.12 Performance of various lock elision mechanisms in memcached1295.13 Characteristics of elided critical sections in memcached1305.14 Instruction breakdown sections in memcached1315.15 Key core-side code used in the PTLsim load path1355.16 Functions and flow in the memory system of PTLsim1365.17 Core logic and memory system glue logic used in Marss861375.18 Key parts of the redesigned memory system in Marss861385.19 Path for stores becoming visible in memory in PTLsim1405.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                        |

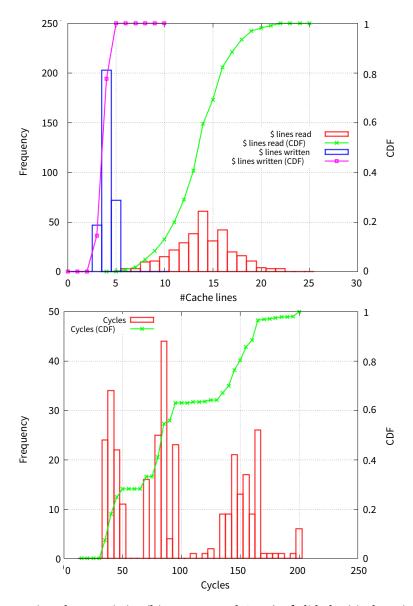

| 5.13 Characteristics of elided critical sections in memcached1305.14 Instruction breakdown sections in memcached1315.15 Key core-side code used in the PTLsim load path1355.16 Functions and flow in the memory system of PTLsim1365.17 Core logic and memory system glue logic used in Marss861375.18 Key parts of the redesigned memory system in Marss861385.19 Path for stores becoming visible in memory in PTLsim1395.20 Store behaviour in Marss86 compared to PTLsim1405.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                      |

| 5.14 Instruction breakdown sections in memcached1315.15 Key core-side code used in the PTLsim load path1355.16 Functions and flow in the memory system of PTLsim1365.17 Core logic and memory system glue logic used in Marss861375.18 Key parts of the redesigned memory system in Marss861385.19 Path for stores becoming visible in memory in PTLsim1395.20 Store behaviour in Marss86 compared to PTLsim1405.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning and conflict detection in Marss861415.24 Pipeline and data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                |

| 5.15 Key core-side code used in the PTLsim load path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.16 Functions and flow in the memory system of PTLsim1365.17 Core logic and memory system glue logic used in Marss861375.18 Key parts of the redesigned memory system in Marss861385.19 Path for stores becoming visible in memory in PTLsim1395.20 Store behaviour in Marss86 compared to PTLsim1405.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning and conflict detection in Marss861415.24 Pipeline and data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.17 Core logic and memory system glue logic used in Marss861375.18 Key parts of the redesigned memory system in Marss861385.19 Path for stores becoming visible in memory in PTLsim1395.20 Store behaviour in Marss86 compared to PTLsim1405.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning and conflict detection in Marss861415.24 Pipeline and data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.18 Key parts of the redesigned memory system in Marss861385.19 Path for stores becoming visible in memory in PTLsim1395.20 Store behaviour in Marss86 compared to PTLsim1405.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning and conflict detection in Marss861415.24 Pipeline and data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.19 Path for stores becoming visible in memory in PTLsim1395.20 Store behaviour in Marss86 compared to PTLsim1405.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning and conflict detection in Marss861415.24 Pipeline and data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.20 Store behaviour in Marss86 compared to PTLsim1405.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning and conflict detection in Marss861415.24 Pipeline and data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

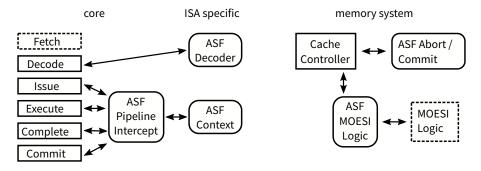

| 5.21 Graphical overview of the ASF implementation in Marss861405.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning and conflict detection in Marss861415.24 Pipeline and data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

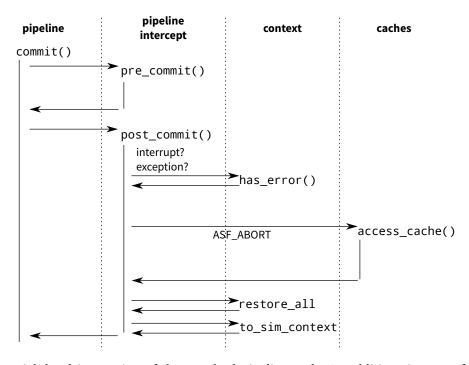

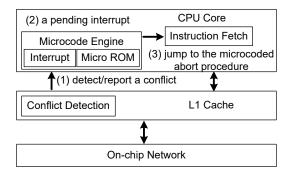

| 5.22 Interaction of pipeline and ASF for an aborting transaction1405.23 Interface of data versioning and conflict detection in Marss861415.24 Pipeline and data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.23 Interface of data versioning and conflict detection in Marss86       141         5.24 Pipeline and data versioning layer interaction       142         5.25 Interface of the ASF_MOESILogic class       144         5.26 Marss86 ASF coherence logic for conflict detection       145         5.27 Interface of the ASF_MOESILogic class       145         6.1 Using non-transactional loads and stores to communicate       154         6.2 Sending and receiving small messages with ASF       155         6.3 Sending long messages by chunking       156         6.4 Multiple transactions using a single service thread       156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

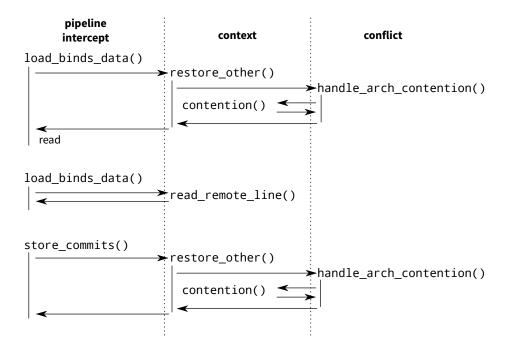

| 5.24 Pipeline and data versioning layer interaction1425.25 Interface of the ASF_MOESILogic class1445.26 Marss86 ASF coherence logic for conflict detection1455.27 Interface of the ASF_MOESILogic class1466.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.25 Interface of the ASF_MOESILogic class       144         5.26 Marss86 ASF coherence logic for conflict detection       145         5.27 Interface of the ASF_MOESILogic class       146         6.1 Using non-transactional loads and stores to communicate       154         6.2 Sending and receiving small messages with ASF       155         6.3 Sending long messages by chunking       156         6.4 Multiple transactions using a single service thread       156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.26 Marss86 ASF coherence logic for conflict detection       145         5.27 Interface of the ASF_MOESILogic class       146         6.1 Using non-transactional loads and stores to communicate       154         6.2 Sending and receiving small messages with ASF       155         6.3 Sending long messages by chunking       156         6.4 Multiple transactions using a single service thread       156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.27 Interface of the ASF_MOESILogic class       146         6.1 Using non-transactional loads and stores to communicate       154         6.2 Sending and receiving small messages with ASF       155         6.3 Sending long messages by chunking       156         6.4 Multiple transactions using a single service thread       156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.1 Using non-transactional loads and stores to communicate1546.2 Sending and receiving small messages with ASF1556.3 Sending long messages by chunking1566.4 Multiple transactions using a single service thread156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>6.2 Sending and receiving small messages with ASF</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>6.3 Sending long messages by chunking</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.4 Multiple transactions using a single service thread                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul><li>6.4 Multiple transactions using a single service thread</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

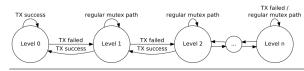

| 6.5 TxChannel state transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

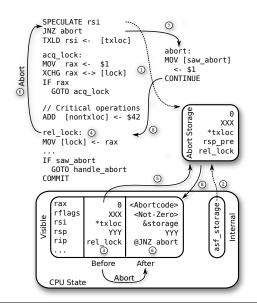

| 6.6 Basic functionality of abort with continuation 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.7 Resurrection and replay of aborted transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

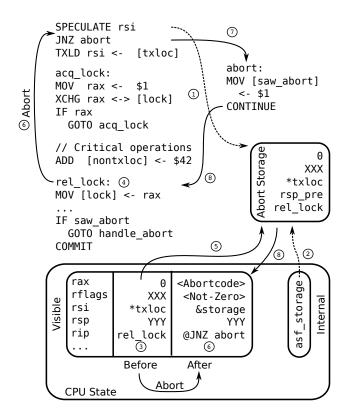

| 6.8 Implementing alert-on-update with ASF 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

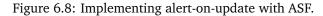

| 6.9 Implementing alert-on-update with ASF, part 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.10 Suspend/resume mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.11 Switching between HTM algorithms and STM 164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

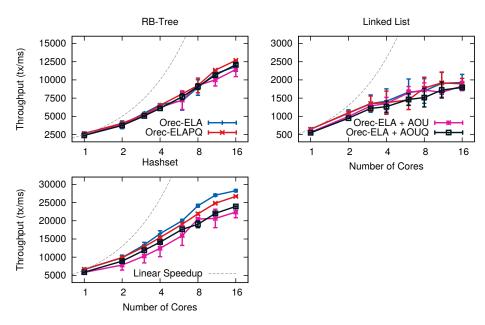

| 6.12 Overheads for software logging and resurrection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.13 Compiler missing optimisation opportunities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.14 Throughput for RSTM OrecELA with AOU 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |