### TECHNISCHE UNIVERSITÄT DRESDEN

# Modellierung von Transistoren mit lokaler Ladungsspeicherung für den Entwurf von Flash-Speichern

#### Rico Srowik

von der Fakultät Elektrotechnik und Informationstechnik der Technischen Universität Dresden

zur Erlangung des akademischen Grades eines

DOKTORINGENIEURS (Dr.-Ing.)

genehmigte Dissertation

Vorsitzender: Prof. Dr.-Ing. habil. U. Frühauf

Gutachter: Prof. Dr.-Ing. habil. R. Schüffny Tag der Einreichung: 22. 03. 2007

Prof. Dr.-Ing. habil. W. Reinhold Tag der Verteidigung: 28. 01. 2008

Prof. Dr.-Ing. T. Mikolajick

Pour Sonia, Kilian et Alena. Je vous aime beaucoup.

#### Kurzfassung

In dieser Arbeit werden Speichertransistoren mit Oxid-Nitrid-Oxid-Speicherschicht und lokaler Ladungsspeicherung untersucht, die zur nichtflüchtigen Speicherung von Informationen genutzt werden. Charakteristisch für diese Transistoren ist, dass an beiden Enden des Transistorkanals innerhalb der Isolationsschicht Informationen in Form von Ladungspaketen unabhängig und getrennt voneinander gespeichert werden.

Für das Auslesen, Programmieren und Löschen der Speichertransistoren werden die physikalischen Hintergründe diskutiert und grundlegende Algorithmen zur Implementierung dieser Operationen auf einer typischen Speicherfeldarchitektur aufgezeigt.

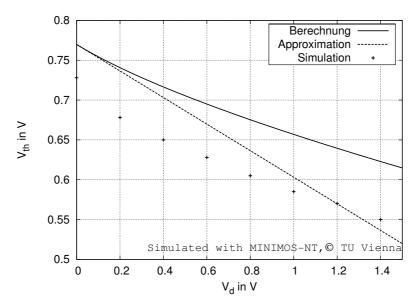

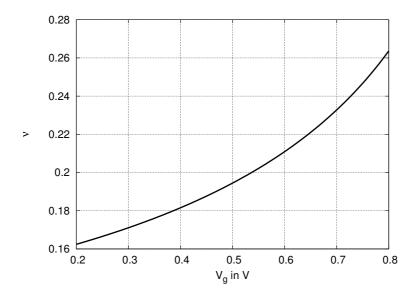

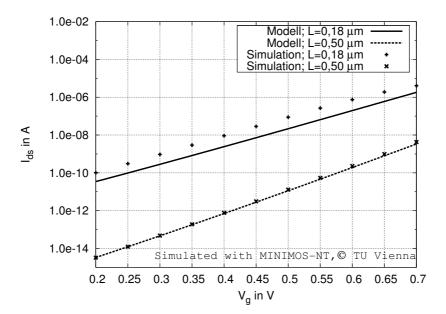

Für Standard-MOS-Transistoren wird ein Kurzkanal-Schwellspannungsmodell abgeleitet und analytisch gelöst. Anhand dieser Modellgleichung werden die bekannten Kurzkanaleffekte betrachtet. Weiterhin wird ein Modell zur Berechnung des Drainstroms von Kurzkanaltransistoren im Subthreshold-Arbeitsbereich abgeleitet und gezeigt, dass sich die Drain-Source-Leckströme bei Kurzkanaltransistoren vergrößern.

Die Erweiterung des Schwellspannungsmodells für Standard-MOS-Transistoren auf den Fall der lokalen Ladungsspeicherung innerhalb der Isolationsschicht erlaubt die Ableitung eines Schwellspannungsmodells für Oxid-Nitrid-Oxid-Transistoren mit lokaler Ladungsspeicherung. Dieses Modell gestattet die qualitative und quantitative Diskussion der Erhöhung der Schwellspannung durch die lokale Injektion von Ladungsträgern beim Programmiervorgang. Weiterhin ist es mit diesem Modell möglich, die Trennung der an beiden Kanalenden des Transistors gespeicherten Informationen beim Auslesevorgang qualitativ zu erklären und diese Bittrennung in Abhängigkeit von der Drainspannung zu berechnen. Für Langkanalspeichertransistoren wird eine analytische Näherungslösung des Schwellspannungsmodells angegeben, während das Kurzkanalverhalten durch die numerische Lösung der Modellgleichung bestimmt werden kann.

Für Langkanalspeichertransistoren wird ein Subthreshold-Modell zur Berechnung des Drainstroms abgeleitet. Dieses Modell zeigt, dass sich die Leckströme von programmierten Speichertransistoren im Vergleich zu Standard-MOS-Transistoren gleicher Schwellspannung vergrößern. Die Ursache dieses Effekts, die Verringerung der Subthreshold-Steigung von Transistoren im programmierten Zustand, wird analysiert.

Für einige praktische Beispiele wird die Anwendung der hergeleiteten Modellgleichungen beim Entwurf von Flash-Speichern demonstriert.

#### **Abstract**

In this work, memory transistors with an oxide-nitride-oxide trapping-layer and local charge storage, which are used for non-volatile information storage, are examined. Characteristic for these transistors is an independent and separated storage of information by charge packages, located at both sides of the transistor channel, in the insulation layer.

The physical backgrounds for reading, programming and erasing the memory transistors are discussed, and basic algorithms are shown for implementing these operations on a typical memory array architecture.

For standard MOS-transistors a short channel threshold model is derived and solved analytically. By using these model equations, the known short channel effects are considered. Further, a model for calculating the drain current of short channel transistors in the subthreshold operation region is derived. This model is used to show the increase of drain-source leakage currents in short channel transistors.

By extending the standard MOS-transistor threshold voltage model for local charge storage in the insulation layers, the derivation of a threshold voltage model for oxide-nitride-oxide transistors with local charge storage is enabled. This model permits the quantitative and qualitative discussion of the increase in threshold voltage caused by local injection of charges during programming. Furthermore, with this model, the separation of the information, which are stored at both sides of the transistor channel, in the read-out operation is explained qualitatively, and the bit separation is calculated dependent on the drain voltage. For long channel memory transistors an analytical approximation of the threshold voltage model is given, whereas the short channel behaviour can be determined by solving the model equation numerically.

For long channel memory transistors, a subthreshold model for calculating the drain current is derived. This model shows the increase in leakage current of programmed memory transistors in comparision to standard MOS-transistors. The root cause of this effect, the reduced subthreshold swing of transistors in the programmed state, is analysed.

The application of the derived model equations for the development of flash memories is demonstrated with some practical examples.

# Inhaltsverzeichnis

| Ve | rzeicl                                 | hnis de                             | r verwendeten Symbole                                      | XI |  |  |

|----|----------------------------------------|-------------------------------------|------------------------------------------------------------|----|--|--|

| 1  | Moti                                   | vation                              |                                                            | 1  |  |  |

| 2  | Ladı                                   | Ladungsspeicherung in ONO-Schichten |                                                            |    |  |  |

|    | 2.1                                    |                                     | lüchtige Speicher                                          | 3  |  |  |

|    | 2.2                                    | ONO-                                | Transistoren mit lokaler Ladungsspeicherung                | 6  |  |  |

|    |                                        | 2.2.1                               | Auslesen der Speicherzelle                                 | 7  |  |  |

|    |                                        | 2.2.2                               | Programmierung der Speicherzelle                           | 8  |  |  |

|    |                                        | 2.2.3                               | Löschen der Speicherzelle                                  | 11 |  |  |

|    | 2.3                                    | Aufba                               | u eines Speicherfelds                                      | 13 |  |  |

|    | 2.4                                    | Algori                              | thmen                                                      | 15 |  |  |

|    |                                        | 2.4.1                               | Lesealgorithmus                                            | 16 |  |  |

|    |                                        | 2.4.2                               | Programmieralgorithmus                                     | 18 |  |  |

|    |                                        | 2.4.3                               | Löschalgorithmus                                           | 20 |  |  |

|    | 2.5                                    | Multil                              | evel-Speicher                                              | 20 |  |  |

| 3  | Schwellspannung von MOS-Transistoren 2 |                                     |                                                            |    |  |  |

|    | 3.1                                    | -                                   | lagen zur Modellierung der Schwellspannung                 | 23 |  |  |

|    |                                        | 3.1.1                               | Bändermodell                                               | 23 |  |  |

|    |                                        | 3.1.2                               | Definition der Schwellspannung                             | 25 |  |  |

|    | 3.2                                    | Elektro                             | ostatisches Potential                                      | 26 |  |  |

|    |                                        | 3.2.1                               | Herleitung der Differentialgleichung des Potentialverlaufs | 26 |  |  |

|    |                                        | 3.2.2                               | Lösung der Differentialgleichung des Potentialverlaufs     | 34 |  |  |

|    |                                        | 3.2.3                               | Diskussion des Potentialverlaufs                           | 35 |  |  |

|    | 3.3                                    | Schwe                               | ellspannungsmodell                                         | 39 |  |  |

|    |                                        | 3.3.1                               | Kurzkanaleffekt                                            | 39 |  |  |

|    |                                        | 3.3.2                               | Drain Induced Barrier Lowering                             | 41 |  |  |

|    | 3.4                                    | Subthr                              | reshold-Verhalten                                          | 42 |  |  |

|    |                                        | 3.4.1                               | Subthreshold-Transferkennlinie                             | 43 |  |  |

|    |                                        | 3.4.2                               | Subthreshold-Steigung                                      | 48 |  |  |

| 4  | Sch                                    | wellspa                             | nnung von ONO-Speichertransistoren                         | 50 |  |  |

|    | 4.1                                    | Model                               | l der Flachbandspannung                                    | 50 |  |  |

|    | 4.2                                    |                                     | ächenpotential                                             | 56 |  |  |

|     |       | 4.2.1   | Differentialgleichung des Potentialverlaufs                  | 56  |

|-----|-------|---------|--------------------------------------------------------------|-----|

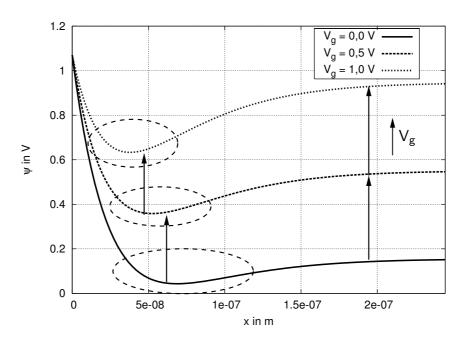

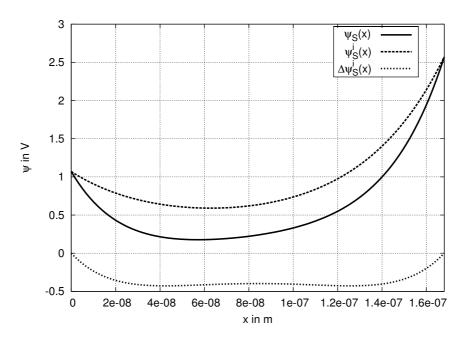

|     |       | 4.2.2   | Diskussion des Potentialverlaufs des Langkanaltransistors    | 60  |

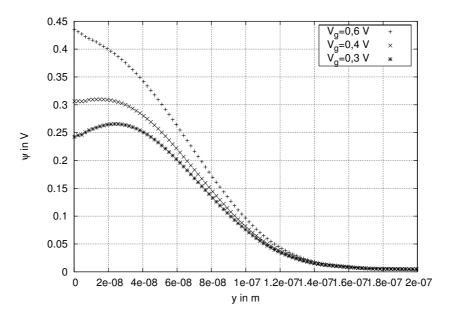

|     |       | 4.2.3   | Diskussion des Potentialverlaufs eines Kurzkanaltransistors  | 67  |

|     |       | 4.2.4   | Grenzen und Erweiterungsmöglichkeiten des Potentialmodells . | 69  |

|     | 4.3   |         | ellspannungsmodell                                           | 72  |

|     |       | 4.3.1   | Programmierung des Langkanaltransistors                      | 72  |

|     |       | 4.3.2   | Nachbarbitunterdrückung bei Langkanaltransistoren            | 75  |

|     |       | 4.3.3   | Programmierung eines Kurzkanaltransistors                    | 82  |

|     |       | 4.3.4   | Kurzkanalverhalten                                           | 84  |

|     |       | 4.3.5   | Nachbarbiteffekt und Bittrennung bei Kurzkanaltransistoren   | 85  |

|     | 4.4   |         | reshold-Langkanalmodell                                      | 88  |

|     |       | 4.4.1   | Subthreshold-Transferkennlinie                               | 88  |

|     |       | 4.4.2   | Subthreshold-Steigung                                        | 90  |

|     |       | 4.4.3   | Grenzen und Erweiterungen des Subthreshold-Modells           | 92  |

| 5   | Anw   | endun   | g beim Entwurf von Flash-Speichern                           | 95  |

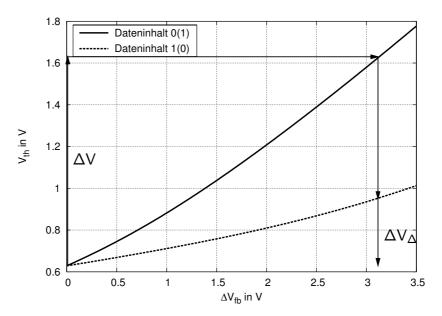

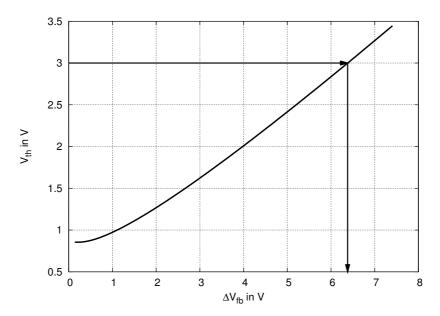

|     | 5.1   | Dimer   | nsionierung der Drainspannung                                | 95  |

|     | 5.2   | Verrin  | gerung des Lesefensters                                      | 97  |

|     | 5.3   |         | täre Subthreshold-Ströme im Lesevorgang                      | 99  |

|     | 5.4   | Subth   | reshold-Leckstrom von stark programmierten Transistoren      | 101 |

| 6   | Zusa  | ammen   | fassung                                                      | 104 |

| Lit | eratu | rverzei | chnis                                                        | 106 |

| Α   | Tran  | sistorn | nodelle für die Bauelementesimulation                        | 114 |

|     | A.1   | Langk   | anal-MOS-Transistor                                          | 114 |

|     | A.2   | Kurzk   | anal-MOS-Transistor                                          | 119 |

|     | A.3   | Langk   | anal-ONO-Transistor                                          | 124 |

|     | A.4   | Kurzk   | anal-ONO-Transistor                                          | 129 |

| В   | MIN   | IMOS-N  | IT-Steuerdateien                                             | 134 |

| С   | Num   | nerisch | e Lösung des Schwellspannungsmodells                         | 136 |

# Verzeichnis der verwendeten Symbole

*A*\* Effektive Richardson-Konstante

$C_{ox}$  Kapazitätsbelag des Gateoxids einer MOS-Struktur;  $C_{ox} = \varepsilon_{ox}/t_{ox}$

$\vec{E}$  Elektrische Feldstärke

$E_{x,y}$  x- bzw. y-Komponente der elektrischen Feldstärke

*i* Elektrische Stromdichte

$j_{x,y}$  x- bzw. y-Komponente der elektrischen Stromdichte

k Boltzmannkonstante;  $k = 1{,}381 \cdot 10^{-23} \,\text{As/K}$

L Effektive Transistorlänge

*l<sub>c</sub>* Charakteristische Länge für Kurzkanaleffekte

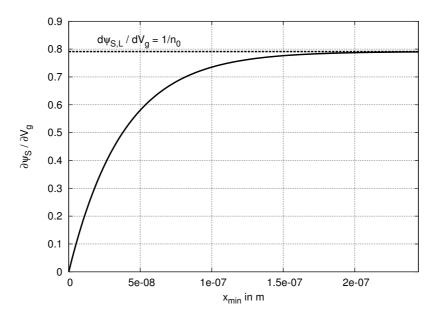

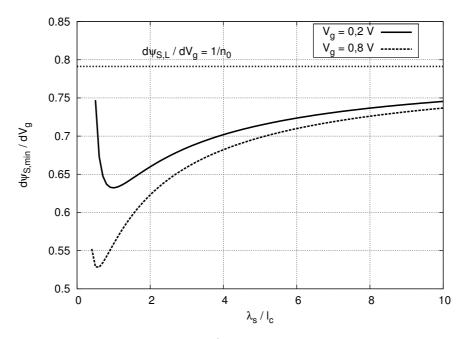

$n_0$  Kenngröße  $(dψ_S/dV_g)^{-1}$

$n_i$  Eigenleitungsdichte von Silizium;  $n_i = 1.5 \cdot 10^{10} \,\mathrm{cm}^{-3}$  (300 K)

$N_A$  Akzeptordichte

$N_A^-$  Akzeptordichte, ionisiert

$N_D$  Donatordichte

$N_D^+$  Donatordichte, ionisiert

*q* Betrag der Elementarladung eines Elektrons;  $q = 1,602 \cdot 10^{-19} \,\text{As}$

Q Elektrische Ladung

Q' Elektrische Linienladungsdichte

$Q_{inj}^{"*}$  Ladungsdichte der in das Nitrid injizierten Ladungen  $Q_{ar}^{"}$  Ladungsdichte im Gateoxid einer MOS-Struktur

$Q_{ss}''$  Zwischenschichtladungsdichte der Oxid-Halbleiter-Grenzfläche

SS Subthreshold-Steigung

Temperatur

$t_{one}^*$  Effektive Dicke des ONO-Stapels

$t_{ox}$  Oxiddicke von Standard-MOS-Transistoren

$t_{dep}$  Tiefe der Raumladungszone in MOS-Transistoren;

Verarmungslänge

$t_{dep,L}$  Tiefe der Raumladungszone in Langkanal-MOS-Transistoren

$t_j$  Tiefe der Source-/ Drain-Gebiete  $U_T$  Temperaturspannung;  $U_T = kT/q$

V Externes Potential

$V_{ab}$  Spannung zwischen den Kontakten a und b

$V_{bi}$  Diffusionsspannung  $V_{fb}$  Flachbandspannung

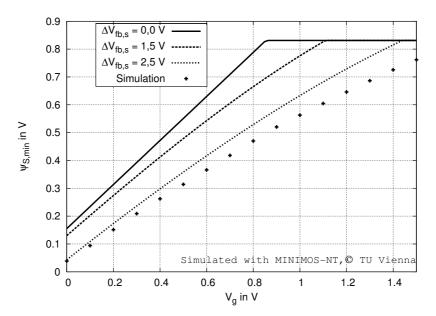

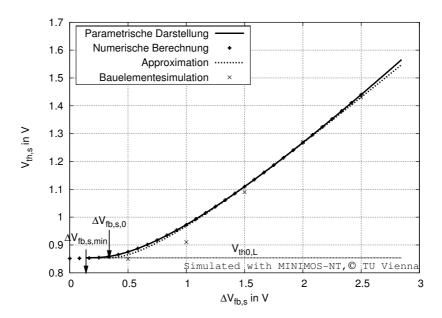

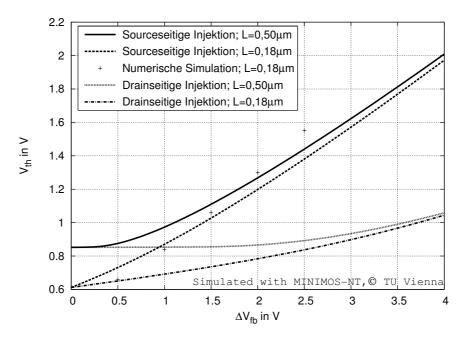

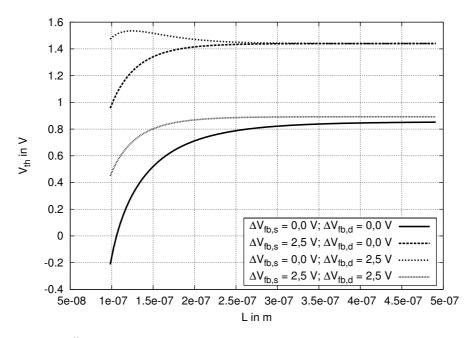

$\Delta V_{fb,s(d)}$  Maximalwert der source- (drain-) seitigen Verschiebung der

Flachbandspannung durch die Programmierung des

ONO-Speichertransistors; Programmierniveau; Injektionsniveau

$\Delta V_{fb,s(d),min}$  Minimalwert von  $\Delta V_{fb,s(d)}$ , der notwendig ist, um ein lokales

Minimum im Potentialverlauf auszubilden

$\Delta V_{fb,s(d),0}$  Minimalwert von  $\Delta V_{fb,s(d)}$ , ab dem eine Verschiebung der

Schwellspannung eines ONO-Speichertransistors stattfindet;

Definiert für die quadratische Näherung der

Schwellspannungsgleichung

$V_{fb,0}$  Flachbandspannung des initialen ONO-Speichertransistors

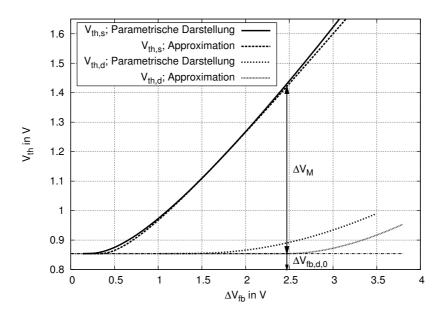

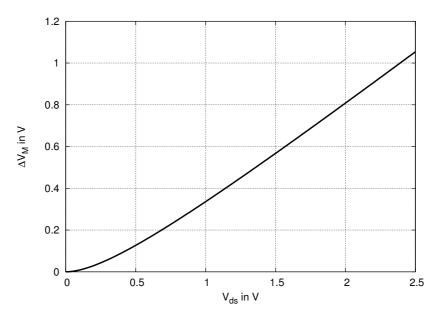

$\Delta V_M$  Unterschied der Langkanalschwellspannung eines

unprogrammierten Transistors zur maximalen

Rückwärts-Schwellspannung ohne Nachbarbiteffekt; Bittrennung

$V_{ox}$  Spannung über dem Gateisolator

$V_{th}$  Schwellspannung

$V_{th,fwd}$  Schwellspannung in der Vorwärts-Lese-Betriebsart

$V_{th,L}$  Langkanalschwellspannung

$V'_{th,L}$  Extrapolierte Langkanalschwellspannung  $V'_{th0,L}$  Extrapolierte Schwellspannung eines langen

ONO-Speichertransistors im initialen Zustand

$V_{th,rev}$  Schwellspannung in der Rückwärts-Lese-Betriebsart

$V_{th.s(d)}$  Schwellspannung eines ONO-Speichertransistors, die sich durch die

Verwendung des source- (drain-) seitigen lokalen Minimums des

Potentialverlaufs ergibt

$V_V$  Breite der Schwellspannungsverteilung

$V_{\Delta}$  Abstand der Schwellspannungsverteilung der programmierten und

der gelöschten Bits eines Speicherfelds; Lesefenster

W<sub>c</sub> Energie des Leitungsbands

$W_{EA}$  Austrittsarbeit  $W_F$  Fermienergie  $W_g$  Bandabstand

$W_i$  Energie des Eigenleitungsniveaus  $W_m$  Aktivierungsenergie des Metallgates  $W_s$  Aktivierungsenergie des Siliziumsubstrats

$W_{\nu}$  Energie des Valenzbands

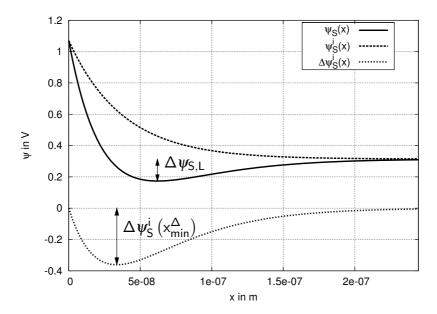

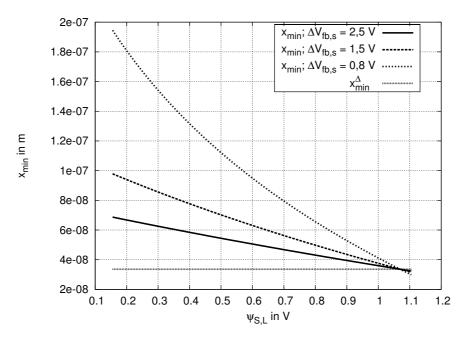

$x_{min}^{\Delta}$  Lage des Minimalwerts der Potentialverschiebung  $\Delta \psi_{S}^{i}$

γ Substratsteuerfaktor; Bodyeffekt-Koeffizient

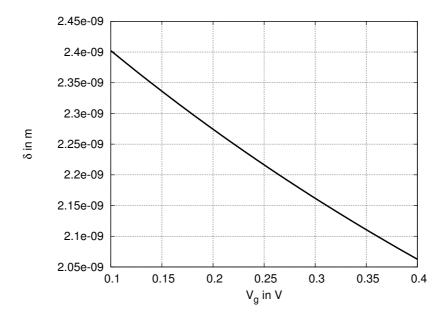

$\delta$  Effektive Kanalweite

$\varepsilon_{nit}$  Absolute Dielektrizitätskonstante des Nitrids  $\varepsilon_{ox}$  Absolute Dielektrizitätskonstante des Gateoxids  $\varepsilon_{si}$  Absolute Dielektrizitätskonstante von Silizium

$\eta$  Fittingparameter

$\lambda_{s,d}$  Ausdehnung der lokalen Änderungen der Flachbandspannung

Λ Mittlere freie Weglänge eines Ladungsträgers

μ Beweglichkeit

$\overline{\mu}$  mittlere Beweglichkeit  $\rho$  Raumladungsdichte

$\rho_{inj}$  Raumladungsdichte der in das Nitrid injizierten Ladungen

$\rho_{inj}^{*}$  Effektive Raumladungsdichte der in das Nitrid injizierten Ladungen

unter Berücksichtigung der lateralen Komponente des elektrischen

Felds im Nitrid

*φ* Makropotential

$\phi$  Elektrostatisches Potential im Halbleiter, bezogen auf das

Ferminiveau im Halbleiterinneren

$\Phi_{MS}$  Metall-Halbleiter-Kontaktspannung

$\psi$  Elektrostatisches Potential im Halbleiter, bezogen auf

Eigenleitungsniveau im Halbleiterinneren

$\psi_0$  Oberflächenpotential bei Beginn der starken Inversion;  $\psi_0 = V_s + V_{bi}$

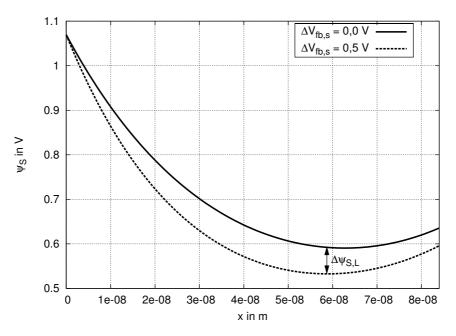

$\psi_S$  Oberflächenpotential des Halbleiters

$\psi_S^i$  Initiales Oberflächenpotential eines ONO-Transistors  $\Delta \psi_S^i$  Verschiebung des initialen Oberflächenpotentials eines

ONO-Transistors durch die injizierten Ladungen

$\Delta \psi_S$  Unterschied zum Oberflächenpotential eines langen Transistors

$\Delta \psi_{S,L}$  Unterschied zum Oberflächenpotential eines langen,

unprogrammierten ONO-Transistors

$\Psi_{FB}$  Fermipotential des Substrates

## 1 Motivation

Als nichtflüchtige Speicher (non-volatile memories) werden Halbleiterspeicher bezeichnet, in denen die gespeicherte Information auch nach dem Abschalten der Stromzufuhr erhalten bleibt. Für diese Speicherklasse gibt es einen weiten Anwendungsbereich. Gerade in jüngster Vergangenheit ist die Nachfrage nach nichtflüchtigen Speichern durch neuartige Anwendungen, wie USB-Speicherstifte, SD- oder Compact-Flash-Speicherkarten oder tragbare Musikabspielgeräte, innerhalb kürzester Zeit stark angestiegen. Aufgrund dieser starken Nachfrage bauen die Halbleiterhersteller zurzeit ihre Produktionskapazitäten aus. Mit dem Ausbau der Produktionskapazitäten und der Massenproduktion der Speicherchips geht aber auch eine Verschärfung des Wettbewerbs unter den Herstellern einher. Der Wettbewerbsdruck zwingt die Halbleiterhersteller dazu, Speichertechnologien einzuführen, die die Entwicklung von Produkten mit dem geringstmöglichen Preis pro gespeicherter Information erlauben.

Die Suche nach Speicherprinzipien mit hoher Speicherdichte führte zur Wiederentdeckung der Transistoren mit Oxid-Nitrid-Oxid-Speicherschicht (sogenannter *SONOS-Speicher*) in Verbindung mit der Entwicklung des Prinzips der lokalen Ladungsspeicherung, das darauf beruht, dass in jedem Transistor an beiden Kanalenden Informationen unabhängig voneinander gespeichert werden können. Dieses Prinzip wurde von der Firma Saifun unter der Bezeichnung NROM<sup>TM</sup>-Technologie entwickelt und an verschiedene Halbleiterhersteller lizensiert. Auf dem NROM<sup>TM</sup>-Prinzip basierende Produkte werden zum Beispiel unter den Bezeichnungen Twin Flash<sup>TM</sup> (Qimonda), NBit<sup>TM</sup> (Macronix), Mirrorbit<sup>TM</sup> (Spansion) oder micro flash (Tower Semiconductor) angeboten. Weitere Firmen, die diese Speichertechnologie lizensiert haben, sind unter anderem Sony, NEC und SMIC. Die NROM<sup>TM</sup>-Technologie ist also mit Massenprodukten auf dem Markt der nichtflüchtigen Speicher vertreten.

Obwohl die Technologie der lokalen Ladungsspeicherung bereits in kommerziellen Produkten angewendet wird, sind die physikalischen Hintergründe der Ladungsspeicherung, der Zuverlässigkeit und Alterung, des Datenhaltevermögens, der Wiederbeschreibbarkeit und des Strom-Spannungs-Verhaltens der Speichertransistoren noch unzureichend erforscht. Modelle, die die zugehörigen physikalischen Prozesse beschreiben, sind derzeit Gegenstand intensiver Forschungen und kaum für eine Anwendung in der Produktentwicklung verfügbar.

Typischerweise beginnt der System- und Schaltungsentwurf von Demonstratorsystemen, die die Ausbeutefähigkeit einer neuen Technologie nachweisen sollen, und von nachfolgenden kommerziellen Einführungsprodukten jedoch schon, wenn sich die zugehörige Technologiegeneration noch in einer frühen Phase ihrer Entwicklung befindet.

Trotzdem müssen bereits in dieser frühen Entwurfsphase viele wichtige Entscheidungen getroffen werden, wie zum Beispiel die Auswahl der Speicherfeldarchitektur oder die Auswahl der Schaltungskonzepte. Zusätzlich werden den System- und Schaltungsentwicklern bereits in der Konzeptphase verlässliche Abschätzungen zu Produktkenngrößen wie Schreib-, Lese- und Löschgeschwindigkeiten und den zugehörigen Verlustleistungen abverlangt. Fehlentscheidungen in der Konzeptauswahl oder Auswirkungen von ungenauen Abschätzungen der Produktparameter sind in späteren Entwurfsphasen kaum noch korrigierbar.

Die System- und Schaltungsentwickler benötigen deshalb Modelle, mit denen die elektrischen Eigenschaften der Speichertransistoren schon mit Hilfe weniger bekannter Technologieparameter abgeschätzt werden können. Diese Technologieparameter können dabei zum Teil durch Extrapolation aus vorherigen Technologiegenerationen gewonnen werden. Die Verwendung von physikalischen Modellen erlaubt es dem Designer, wichtige Systemkenngrößen, wie die Arbeitspunkte der Speichertransistoren oder eine eventuelle gegenseitige Beeinflussung der beiden in einem Transistor gespeicherten Informationen, zu einem sehr frühen Zeitpunkt des Entwurfsprozesses zu bestimmen und damit gegebenenfalls Einfluss auf die Entwicklung des Speicherbauelements zu nehmen.

Die wichtigste Kenngröße von nichtflüchtigen Speichertransistoren ist die Transistorschwellspannung, da die Höhe dieser Schwellspannung die gespeicherte Information repräsentiert. Außerdem ist ein Schwellspannungsmodell Voraussetzung für die Beschreibung der Strom-Spannungs-Kennlinie der Speichertransistoren. Aus diesem Grund wird in dieser Arbeit ein physikalisches Schwellspannungsmodell für Oxid-Nitrid-Oxid-Speichertransistoren mit lokaler Ladungsspeicherung entwickelt. Besondere Beachtung soll dabei der Anwendung dieses Modells für den Systementwurf von Flash-Speichern geschenkt werden.

In der folgenden Arbeit wird zunächst in das Gebiet der nichtflüchtigen Speicher eingeführt. Dabei wird besonders auf Speichertransistoren mit Oxid-Nitrid-Oxid-Speicherschicht und lokaler Ladungsspeicherung eingegangen. Anhand dieses Speicherprinzips werden die physikalischen Mechanismen, die das Lesen, Programmieren und Löschen der Speicherzellen erlauben, erläutert und der Aufbau von typischen Speicherfeldern beschrieben. Im nächsten Kapitel wird ein Modell zur Berechnung der Schwellspannung von Standard-MOS-Transistoren abgeleitet und ein Modell der Strom-Spannungs-Kennlinie im Subthreshold-Arbeitsbereich der Transistoren erstellt. Anschließend wird das Schwellspannungsmodell auf Speichertransistoren mit lokaler Ladungsspeicherung erweitert und es werden Schlussfolgerungen zum Programmierverhalten und zu eventuellen Beeinflussungen der Schwellspannung eines Bits durch die gespeicherte Ladung des Nachbarbits gezogen. Weiterhin wird die Strom-Spannungs-Kennlinie im Subthreshold-Bereich für programmierte Langkanalspeichertransistoren abgeleitet und diskutiert. Anhand einiger praktischer Beispiele wird die Anwendung der Modelle beim System- und Schaltungsentwurf gezeigt.

# 2 Ladungsspeicherung in ONO-Schichten

In diesem Kapitel erfolgt zunächst eine Einteilung der nichtflüchtigen Speicher nach dem Aufbau der Speichertransistoren. Für die Unterart der SONOS-Speicher mit lokaler Ladungsspeicherung werden anschließend die Programmierung, das Auslesen und das Löschen in ihren physikalischen Mechanismen und in der technischen Realisierung diskutiert. Im Anschluss wird die Zusammenschaltung einzelner Speicherzellen zu großen Speicherfeldern und die Ausführung von Programmier-, Lese- und Löschalgorithmen gezeigt. Den Abschluss bildet ein Ausblick auf die Multilevel-Speicherung.

# 2.1 Nichtflüchtige Speicher

Im Laufe der Entwicklung der Halbleiterspeicher wurden verschiedene physikalische Prinzipien zur nichtflüchtigen Speicherung von Informationen implementiert. Alle diese Verfahren beruhen darauf, dass in einer MOS-Transistorstruktur elektrische Ladungen in eine Speicherschicht, die sich zwischen dem Gate und dem Substrat befindet, eingebracht werden und dass das Abfließen dieser Ladungen mit Hilfe isolierender Schichten verhindert wird. Wie in Abschnitt 3.1 gezeigt werden wird, verändert die so gespeicherte Ladung die Schwellspannung des Transistors. Da die Schwellspannung den Drainstrom beeinflusst, kann man durch Messung des Drainstroms auf die Schwellspannung rückschließen und damit die gespeicherte Information auslesen.

Im Allgemeinen werden bei der sogenannten Programmierung des Transistors Elektronen in die Speicherschicht eingebracht, wodurch die Schwellspannung ansteigt. Es ist üblich, dem Zustand der erhöhten Schwellspannung den logischen Pegel "0" zuzuordnen. Werden die gespeicherten Ladungen entfernt und der niedrige Schwellspannungswert eingestellt, spricht man vom Löschen des Transistors. Die niedrige Schwellspannung hat im Allgemeinen den logischen Wert "1".

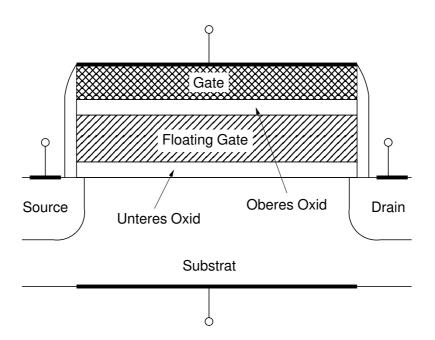

Entsprechend ihrem Aufbau werden nichtflüchtige Speicher in zwei Hauptklassen unterteilt [BB98]. Die Floating-Gate-Transistoren besitzen, wie in Abb. 2.2 gezeigt wird, ein zusätzliches, isoliertes Gate. Dieses "schwebende" (floating) Gate besteht für gewöhnlich aus leitfähigem Polysilizium. Das Floating Gate ist von isolierenden Schichten aus Siliziumoxid umgeben. Im Allgemeinen besitzen Floating-Gate-Transistoren ein zusätzliches Steuergate (Control Gate).

Die ersten funktionsfähigen Floating-Gate-Speichertransistoren nutzten für die Programmierung die Injektion von hochenergetischen Elektronen, die durch einen Lawinendurchbruch erzeugt wurden (*Floating gate Avalanche MOS transistor* - FAMOS) [FB74]. Die derzeit am weitesten verbreiteten *FLOating gate Thin OXid*- (FLOTOX) Transisto-

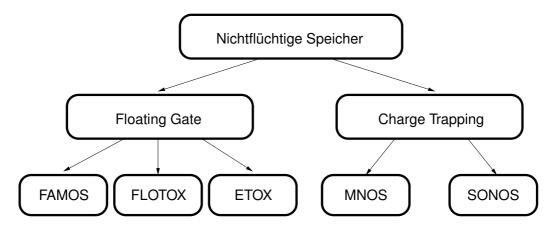

Abbildung 2.1: Einteilung der nichtflüchtigen Speicher nach deren Aufbau

Abbildung 2.2: Allgemeiner Aufbau eines Floating-Gate-Transistors

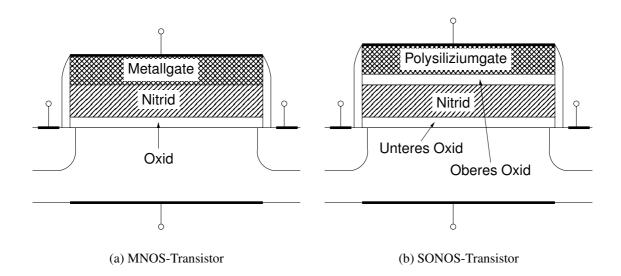

**Abbildung 2.3:** Gegenüberstellung des Aufbaus von MNOS- und SONOS-Speichertransistoren

ren und *EPROM Tunnel OXid*- (ETOX<sup>TM</sup>) Transistoren werden jedoch gewöhnlicherweise durch Fowler-Nordheim- (FN-) Tunnelung des unteren, dünnen Oxids programmiert und gelöscht. In einigen Floating-Gate-Speichern werden auch hochenergetische Kanalelektronen für den Programmiervorgang verwendet. Dieser physikalische Mechanismus wird in Abschnitt 2.2.2 diskutiert.

Floating-Gate-Speicher sind die gebräuchlichsten nichtflüchtigen Speicher und dominieren gegenwärtig den Markt. Floating-Gate-Transistoren sind technisch so weit entwickelt, dass sogar mehrere Schwellspannungsniveaus programmiert und über eine lange Datenhaltezeit stabil ausgelesen werden können. Diese Multibit-Speicherung erlaubt eine weitere Erhöhung der effektiven Speicherdichte.

Die zweite Hauptklasse der nichtflüchtigen Speicher sind die Charge-Trapping-Speicher. Bei dieser Speicherart wird die injizierte Ladung in einer elektrisch nichtleitenden Schicht, meist in Siliziumnitrid (Si<sub>3</sub>Ni<sub>4</sub>), gespeichert. In dieser Speicherschicht oder an deren Nitrid-Oxid-Grenzschicht befinden sich sogenannte Haftstellen (*Traps*), die mit Ladungsträgern besetzt werden können und die diese Ladungsträger dann, unter entsprechenden Bedingungen, wieder emittieren. In der ursprünglichen Form waren diese Transistoren als Metall-Nitrid-Oxid-Silizium (MNOS-) Stapel aufgebaut [FB70]. Da jedoch festgestellt wurde, dass diese Transistoren die eingefangenen Ladungen über den Metall-Nitrid-Übergang nach und nach verlieren können, wurden zur Erhöhung der Datenhaltezeit eine weitere Oxidschicht zwischen dem Nitrid und dem Gateanschluss eingefügt und diese Transistoren mit einem Polysilizium-Gate ausgestattet. Es ergibt sich eine Silizium-Oxid-Nitrid-Oxid-Silizium- (SONOS-) Schichtenfolge. Diese beiden Arten der Charge-Trapping-Speicher sind in Abb. 2.3 einander gegenübergestellt.

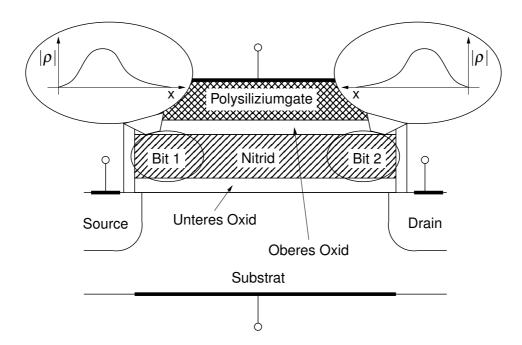

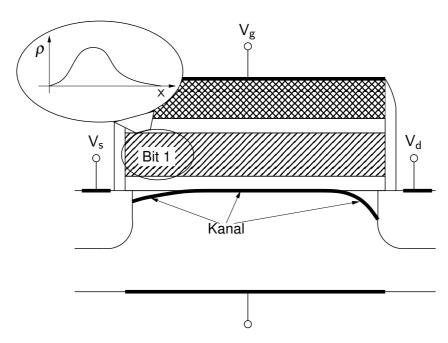

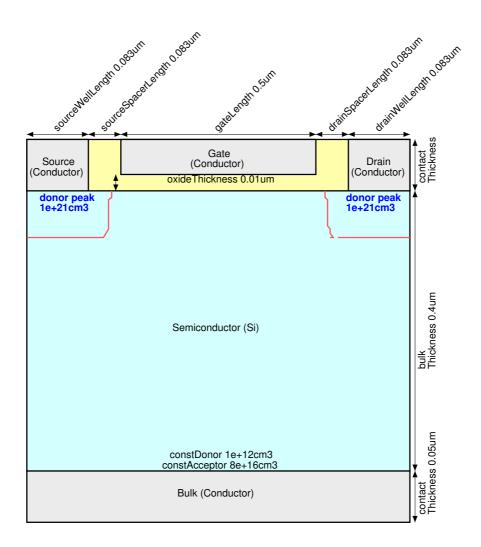

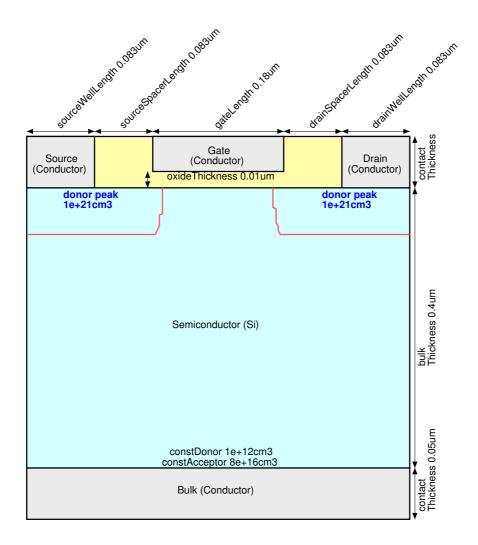

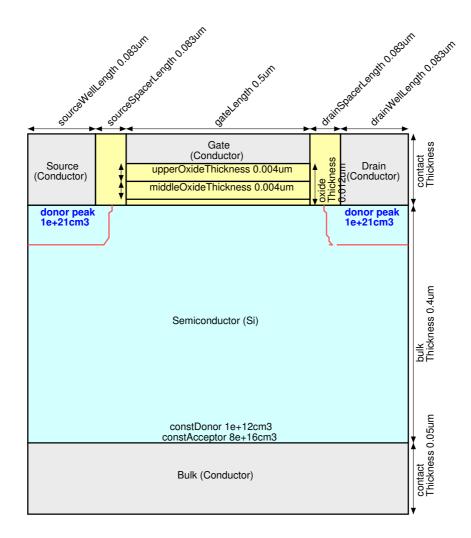

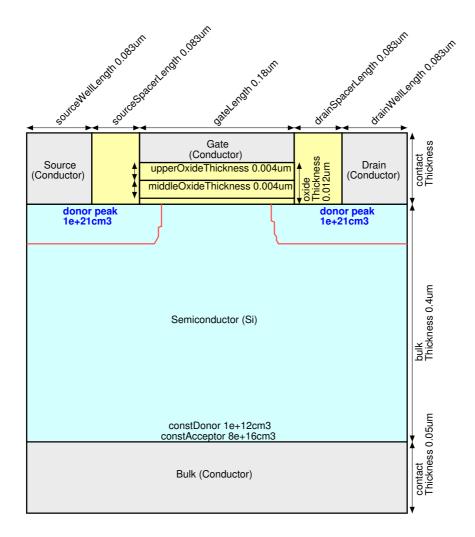

Abbildung 2.4: Aufbau eines SONOS-Transistors mit lokaler Ladungsspeicherung

In den MNOS-Speichern wurden bei der Programmierung die Elektronen durch Fowler-Nordheim- (FN-) -Tunnelung aus dem Substrat in das Nitrid eingebracht. Für das Löschen wurde das FN-Tunneln von Löchern aus dem Substrat in das Nitrid bzw. der Elektronen aus dem Nitrid in das Gate verwendet [LS72]. SONOS-Speicher wenden ebenfalls häufig FN-Tunnelung für die Programmierung an, teilweise werden aber auch hochenergetische Kanalelektronen verwendet [CCS<sup>+</sup>98]. Für das Löschen sind ebenfalls verschiedene Mechanismen verbreitet, wie zum Beispiel das FN-Tunneln von Löchern bzw. Elektronen oder die Injektion von hochenergetischen Löchern aus dem Substrat.

## 2.2 ONO-Transistoren mit lokaler Ladungsspeicherung

Auf der Suche nach Speicherprinzipien, die eine hohe Informationsdichte und damit einen niedrigen Preis pro gespeichertem Bit erlauben, entwickelte Boaz Eitan einen speziellen SONOS-Speichertransistor, der sich dadurch auszeichnet, dass in jedem Transistor zwei Bits gespeichert werden können [EPB<sup>+</sup>99] [EPB<sup>+</sup>00].

Wie in Abb. 2.4 gezeigt wird, besitzt diese Transistorart den üblichen SONOS-Schichtenaufbau. Im Unterschied zu den gewöhnlichen SONOS-Speichertransistoren werden die injizierten Ladungen aber nicht homogen in lateraler Richtung im Nitrid gespeichert. Vielmehr befinden sich in diesen Speichertransistoren die Ladungspakete, die die beiden gespeicherten Bits repräsentieren, räumlich voneinander getrennt über dem source- bzw. drainseitigen Kanalende in der Nitrid-Speicherschicht.

Dieses neuartige Speicherprinzip gewinnt derzeit stark an Beachtung und wird auch schon für kommerzielle Massenprodukte eingesetzt [MDS<sup>+</sup>02] [SEB<sup>+</sup>04] [KIM<sup>+</sup>05] [LAC<sup>+</sup>04] [TZW<sup>+</sup>06] [FKR<sup>+</sup>06] [CPL<sup>+</sup>06]. Im Folgenden soll sich auf diese SONOS-Speicher mit lokaler Ladungsspeicherung konzentriert werden.

### 2.2.1 Auslesen der Speicherzelle

Wie in den letzten Abschnitten erwähnt wurde, wird durch das Programmieren eine hohe Schwellspannung und durch das Löschen eine niedrige Schwellspannung des Speichertransistors eingestellt. Beim Lesen soll der Schwellspannungszustand festgestellt werden und eine Zuordnung zu einem logischen Wert stattfinden.

Bei der Leseoperation wird ausgenutzt, dass der Drain-Source-Strom eines MOS-Transistors unter anderem von der Schwellspannung abhängt. An den Speichertransistor wird eine Drainspannung von  $1\dots 2V$  und eine Gatespannung von  $\sim 4V$  angelegt [LAC<sup>+</sup>04] [SEB<sup>+</sup>04] [KIM<sup>+</sup>05]. Das Source wird auf einem Potential von < 0.2V gehalten.

Der Drain-Source-Strom wird gewöhnlich gemessen, indem er in einen äquivalenten Spannungswert umgesetzt wird. Diese Umsetzung kann durch einen ohmschen Widerstand (*DC-Sensing*) oder durch die Integration des Stroms auf einer Kapazität (*AC-Sensing*) erfolgen. Weiterhin gibt es die beiden schaltungstechnischen Möglichkeiten, den Strom im Drain-Zweig (*Drain-Side-Sensing*) oder im Source-Zweig (*Source-Side-Sensing*) zu messen. Der gemessene Strom wird dann mit einem Referenzstrom verglichen. Ist der Messstrom größer als der Referenzwert und die Schwellspannung des Speichertransistors also gering, wird ein gelöschter Zustand detektiert und dem ausgelesenen Bit folglich der logische Wert "1" zugeordet. Ist der Messstrom im umgekehrten Fall kleiner als der Referenzstrom, wird der logische Wert "0" ausgegeben. Die Strommessung und Detektion des logischen Werts findet im Leseverstärker (*Sense Amplifier*) statt.

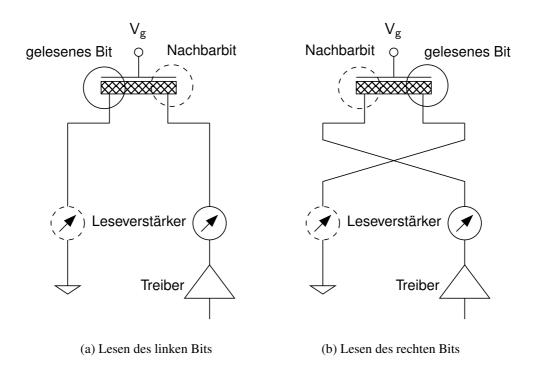

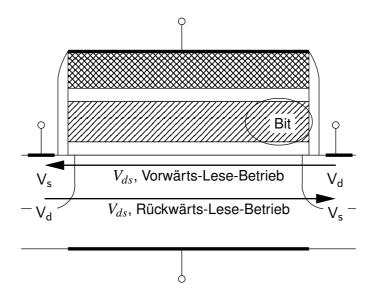

Bei ONO-Transistoren mit lokaler Ladungsspeicherung sind Informationen an beiden Kanalenden gespeichert. Beim Lesen wird die Information desjenigen Bits ausgewertet, das sich an der Sourceseite befindet, also auf dem niedrigeren Potential liegt. Das andere, sogenannte *Nachbarbit*, liegt auf der Drainseite auf einem hohen Potential und seine Auswirkung auf den Messstrom wird somit im Idealfall unterdrückt. Sollen beide Bits nacheinander gelesen werden, müssen also die beiden Kanalkontakte nacheinander die Rolle des Drain- und Sourceanschlusses übernehmen (Abb. 2.5).

Beim Auslesen des interessierenden Bits kann das Nachbarbit das Messergebnis störend beeinflussen. Aus diesem Grund wird in Abschnitt 4.3.2 der physikalische Hintergrund der Nachbarbitunterdrückung untersucht und ein Modell zur Quantifizierung der Nachbarbitunterdrückung hergeleitet.

**Abbildung 2.5:** Auslesen einer ONO-Speicherzelle

### 2.2.2 Programmierung der Speicherzelle

Wie auch einige andere nichtflüchtige Speicher werden die ONO-Speicher mit lokaler Ladungsspeicherung durch hochenergetische ("heiße") Kanalelektronen programmiert (*Channel Hot Electrons* – CHE).

Zur Erzeugung dieser heißen Elektronen wird an den Transistor eine Drain-Source-Spannung von zum Beispiel  $\sim 5\,\mathrm{V}$  angelegt. Die Gate-Source-Spannung liegt etwa bei  $\sim 9\,\mathrm{V}$  [KIM $^+05$ ]. Da der Transistor folglich im Bereich der starken Inversion betrieben wird, bildet sich an der Substratoberfläche ein leitfähiger Elektronenkanal aus.

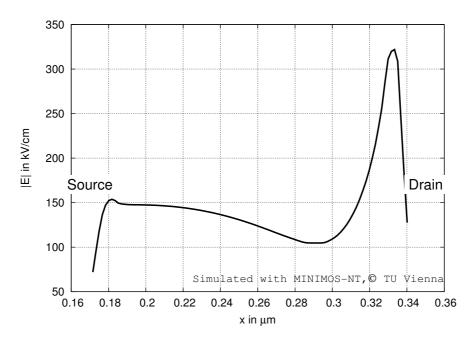

In Abb. 2.6 ist ein typischer Feldstärkeverlauf entlang des Elektronenkanals eines MOS-Transistors gezeigt. Charakteristisch ist der starke Anstieg der elektrischen Feldstärke in einem schmalen Bereich am drainseitigen Kanalende. Die Elektronen werden entsprechend auf ihrem Weg vom Source-Anschluss zum Drain in diesem Bereich stark in Drainrichtung beschleunigt und nehmen dabei Energie auf. Durch stochastische Interaktionen mit Phononen, Stoßionisation oder Interaktionen der Ladungsträger untereinander kommt es dabei zu zufälligen Energie- und Richtungsänderungen der Ladungsträger.

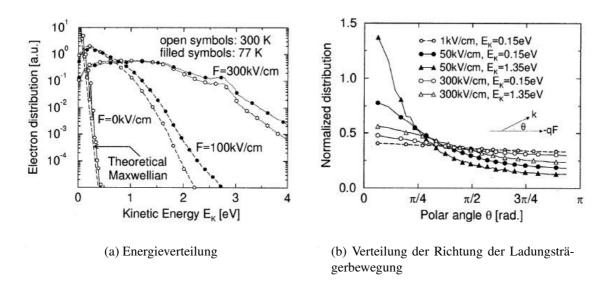

In Abb. 2.7 ist eine Simulation der sich einstellenden Energie- und Richtungsverteilung aus [SF99] gezeigt. Es ist erkennbar, dass bei hohen Feldstärken durch die Beschleunigungs- und Stoßprozesse die Verteilung der Energien der Population der Kanalelektronen im Vergleich zur Maxwell-Verteilung des thermodynamischen Gleichge-

**Abbildung 2.6:** Typischer Verlauf der Feldstärke im Kanal eines SONOS-Transistors bei der Programmierung mit heißen Kanalelektronen

**Abbildung 2.7:** Verteilungen der Energien und Richtungsvektoren der Kanalelektronen bei verschiedenen Feldstärken aus [SF99] (S. 183, Abb. 4.17); Mit freundlicher Genehmigung von Springer Science and Business Media © 1999 Springer/Kluwer Academic Publishers

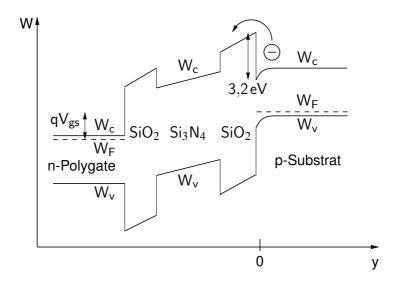

Abbildung 2.8: Bändermodell eines ONO-Transistors bei der Programmierung mit heißen Kanalelektronen

wichts wesentlich breiter wird. Das bedeutet, dass die Wahrscheinlichkeit dafür steigt, dass ein Elektron eine hohe Energie aus dem elektrischen Feld und gegebenenfalls aus Interaktionen gewonnen hat. Gleichzeitig ändert sich die Richtungsverteilung bei hohen Feldstärken derart, dass die Kanalelektronen fast homogen in alle Richtungen gestreut werden.

Diejenigen Elektronen der Population der Kanalelektronen, die in Richtung des ONO-Stapels gestreut werden und die mindestens eine Energie von 3,2eV besitzen [BB98], können, wie in Abb. 2.8 gezeigt wird, die Si-SiO<sub>2</sub>-Barriere überwinden und durch das SiO<sub>2</sub> in die Nitridschicht gelangen und dort Haftstellen besetzen [Mel06].

Aufgrund der schmalen Feldstärkespitze werden die Elektronen trotz Streuung auch primär nur in einem kleinen Bereich in der Nähe des Draingebiets in das Nitrid injiziert. Damit findet die Injektion nur lokal am drainseitigen Kanalende statt. Werden die Rollen der Kanalkontakte als Source- bzw. Drainanschluss getauscht, können auch am anderen Kanalende lokal Ladungen in das Nitrid eingebracht werden und dadurch die beiden Bits getrennt voneinander an den beiden Kanalenden gespeichert werden.

Nicht unerwähnt soll bleiben, dass die Elektronen oder Löcher, die in das Substrat oder entgegen der Feldrichtung gestreut werden, bei hinreichend hoher Energie durch Stoßionisation weitere Elektronen-Löcher-Paare erzeugen können. Die Elektronen können dann unter Umständen relativ weit entfernt vom Draingebiet ebenfalls in das Nitrid injiziert werden. Diese Injektion von sogenannten Sekundärelektronen ist unerwünscht und wird nach Möglichkeit weitestgehend unterdrückt.

Aus diesen Ausführungen kann auch auf einen Nachteil der Verwendung von heißen Kanalelektronen geschlossen werden: Es wird nur ein Teil der Elektronen, nämlich die Elektronen mit genügend hoher Energie **und** mit Streurichtung zum ONO-Isolator für

**Abbildung 2.9:** Ausbildung einer Verarmungszone im Draingebiet eines ONO-Transistors beim Löschvorgang

die Injektion benutzt. Die anderen Kanalelektronen tragen nur zum Drainstrom bei und führen damit zu einem hohen Leistungsbedarf bzw. zu einer geringen Programmiereffizienz.

#### 2.2.3 Löschen der Speicherzelle

Der dominierende physikalische Effekt beim Löschen einer NROM-Speicherzelle ist nach [LPE04] das Löschen mit heißen Löchern. Dabei werden zuerst Elektronen-Loch-Paare erzeugt und dann wird den Löchern Energie zugeführt, so dass einige Löcher in das Nitrid injiziert werden können.

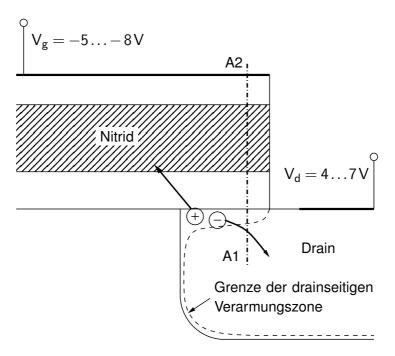

Um die Löschbedingung einzustellen, wird am Gate ein negatives Potential von ungefähr -5...-8 V angelegt. Am Drain liegt eine positive Drainspannung von 4...7 V an, während das Source im Allgemeinen unbeschaltet (floating) oder auf einem niedrigen Potential gehalten wird [KIM<sup>+</sup>05]. Wie in Abb. 2.9 dargestellt wurde, bildet sich in der Drain-Gate-Überlappungszone an der Oberfläche des n-Draingebiets aufgrund der hohen Drain-Gate-Spannung und der durch die Programmierung eingebrachten negativen Raumladung eine Verarmungszone aus.

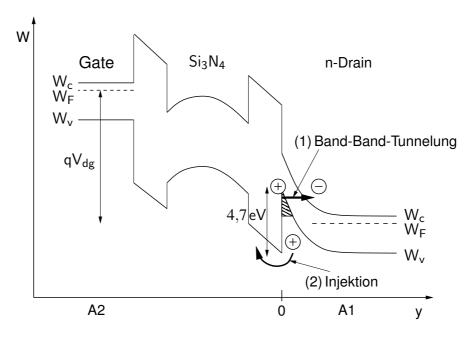

In Abb. 2.10 wurde entlang der in Abb. 2.9 eingetragenen Schnittlinie durch die Verarmungszone A1–A2 das Bänderdiagramm aufgetragen. Dabei wird ersichtlich, dass aufgrund der hohen Spannungen die Bänder in der Verarmungszone sehr stark verbogen sind. Ist die Bandverbiegung der Valenzbandkante aber größer als der Bandabstand, wie

**Abbildung 2.10:** Bändermodell der ONO-Speicherzelle im Löschbetrieb; (1) Erzeugung der Löcher durch Band-Band-Tunnelung, (2) Injektion heißer Löcher in das Nitrid

im schraffiert markierten Bereich der Abbildung gezeigt wird, können bei hohen Feldstärken die Valenzelektronen in das Leitungsband tunneln. Folglich werden Elektronen-Loch-Paare erzeugt. Dieser physikalische Vorgang wird als Band-Band-Tunnelung bezeichnet [CL87][CCC<sup>+</sup>87].

Die generierten Elektronen bewegen sich zum Drainanschluss, während die Löcher durch die hohe Drain-Gate- bzw. Drain-Source-Spannung in Richtung der Silizium-Oxid-Grenzfläche und des Sourceanschlusses beschleunigt werden. Analog zu den beschriebenen Vorgängen bei der Programmierung können zufällig einige Löcher eine Energie, die größer als 4,7eV ist, erlangen [BB98], so dass sie, falls sie in Richtung des ONO-Stapels gestreut werden, die Energiebarriere der Silizium-Oxid-Grenzfläche überwinden können. Diese Löcher können dann Haftstellen im Nitrid besetzen und die negative Ladung der bei der Programmierung injizierten Elektronen kompensieren.

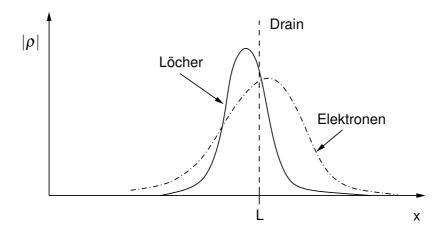

Aufgrund der unterschiedlichen Feldverteilungen und der Verschiedenartigkeiten der physikalischen Mechanismen der Ladungsträgergeneration und -beschleunigung beim Löschvorgang im Vergleich zur Programmierung sind die lateralen Verteilungen der im Nitrid eingefangenen Löcher und Elektronen unterschiedlich, insbesondere befinden sich ihre Schwerpunkte an verschiedenen lateralen Positionen [ISS02]. Da die Ladungsträger eine sehr geringe Beweglichkeit innerhalb des Nitrids besitzen, findet keine kurzfristige Rekombination der Ladungsträger statt. Das Löschen eines programmierten ONO-Transistors beruht vielmehr auf der elektrischen Neutralisation der Löcher- und Elektronenpakete. Nach den Modellen [LSDBE02] [Jan03] [JES+04] führt eine langsame

**Abbildung 2.11:** Löschen und Programmieren erzeugt unterschiedliche Verteilungen der Löcher bzw. Elektronen.

laterale Umverteilung und der Ausgleich der Elektronen -und Löcherpopulationen allerdings zu einem allmählichen Absinken der Schwellspannung der programmierten Bits. Dieser Vorgang begrenzt die Datenhaltezeit der programmierten Speicherzellen (*Speicherverlust - Retention Loss*). <sup>1</sup>

Ein ONO-Speichertransistor, der noch nicht programmiert oder gelöscht wurde, wird als Transistor im *initialen Zustand* oder *initialer Transistor* bezeichnet. Aufgrund der nicht übereinstimmenden Verteilungen der Löcher und Elektronen wird ein zunächst initialer ONO-Transistor nach erfolgter Programmierung und anschließendem Löschen nicht wieder exakt in den initialen Zustand zurückversetzt. Im Folgenden werden deshalb, wo notwendig, der initiale und der gelöschte Zustand unterschieden.

# 2.3 Aufbau eines Speicherfelds

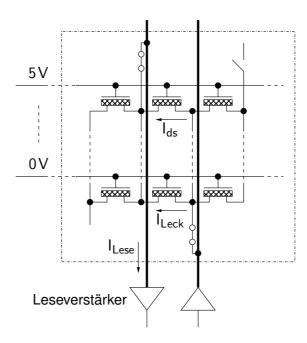

Nachdem der Aufbau und die Funktionsweise der ONO-Speicherzelle beschrieben wurden, wird nun auf den Aufbau eines Speicherfelds (*Array*) eingegangen. Dabei wird sich auf die für Speichertransistoren mit lokaler Ladungsspeicherung typische Architektur des *Virtual Ground Arrays* beschränkt.

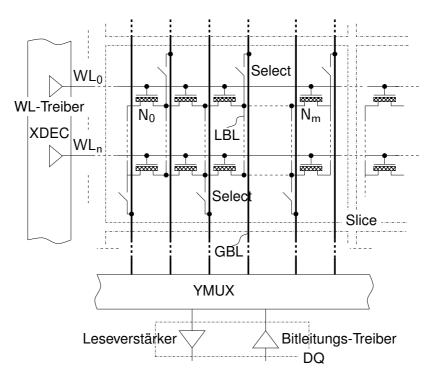

In Abb. 2.12 ist dargestellt, dass in dieser Arraystruktur einige der Speichertransistoren an ihren Gateanschlüssen mittels der sogenannten Wortleitung (WL) horizontal verbunden sind. Eine Anzahl von m+1 Speichertransistoren, zum Beispiel m=32 oder m=65 (inkl. Fehlerkorrekturbits), sind dabei jeweils durch die Verbindung ihrer Kanalkontakte in Serie geschaltet. Diese Transistoren bilden dabei typischerweise eine strukturelle und logische Einheit, die sogenannte Speicherseite oder Page. Speicherseiten, die hinterein-

<sup>&</sup>lt;sup>1</sup>Andere Ansätze sehen als Ursache des Speicherverlusts einen Elektronenverlust durch das untere Oxid [THS06].

**Abbildung 2.12:** Aufbau eines Speicherfelds; Die Transistoren innerhalbes eines Slices sind als *Virtual Ground Array* verschaltet.

ander entlang einer Wortleitung angeordnet sind, werden für gewöhnlich durch Isolation der Kanalkontakte der Endtransistoren elektrisch voneinander getrennt.

Die untereinander liegenden Speicherseiten von n+1 Wortleitungen, zum Beispiel n=255 oder n=511, sind durch *Lokale Bitleitungen* (LBL) miteinander verbunden. Die  $(m+1)\times(n+1)$  Speichertransistoren bilden eine weitere strukturelle Einheit, die sogenannte *Slice*. Die Lokalen Bitleitungen der Slice können durch Schaltertransistoren (Select Transistors) von den *Globalen Bitleitungen* elektrisch getrennt werden. Dadurch beeinflussen hohe Drainspannungen, die beim Programmieren und Löschen auf einer Globalen Bitleitung auftreten, nicht diejenigen Slices, auf die bei diesen Operationen nicht zugegriffen wird. Charakteristische Störungen, sogenannte *Bitleitungsstörungen*, werden unterdrückt. Die Globalen Bitleitungen verbinden die Slices untereinander in vertikaler Richtung.

In Flash-Speichern werden beim Löschen ganze Slices oder große Untergruppen der Slices gleichzeitig gelöscht. Diese Blöcke haben in Abhängigkeit von der Speichergröße bei Daten-Flash-Speichern zum Beispiel eine Größe von 128 Kbyte. Dadurch unterscheiden sich die Flash-Speicher von den EEPROMs, in denen Bits einzeln gelöscht werden können.

Der Y-Multiplexer (YMUX) wählt in Abhängigkeit von der Speicheradresse des Bits, auf das im Array zugegriffen werden soll, zwei Globale Bitleitungen aus, die die für

**Abbildung 2.13:** Typische Häufigkeitsverteilung der Schwellspannungen in einem Speicherfeld und typische Verschiebungen innerhalb der Verteilung durch Raum-Temperatur-Drift (1) und Speicherverluste (Retention Loss) (2)

die jeweilige Betriebsart des Arrays notwendigen Source- und Drainspannungen übertragen. Dafür werden die entsprechenden Bitleitungen mit dem Bitleitungs-Treiber und im Lesebetrieb mit dem Leseverstärker verbunden.

Die Auswahl der Speicherseite geschieht im X-Dekoder (XDEC). Im X-Dekoder sorgen die Wortleitungs-Treiber dafür, dass die aktivierte Wortleitung mit der betriebsartspezifischen Gatespannung beschaltet wird, während die nichtadressierten, inaktiven Wortleitungen durch entsprechende Gatepotentiale deaktiviert werden.

Die Baugruppe, die den Bitleitungs-Treiber und Leseverstärker enthält, wird häufig vereinfachend als *DQ* bezeichnet. Um den Datendurchsatz zu erhöhen, werden Speichertransistoren in mehreren Slices gleichzeitig gelesen, programmiert oder gelöscht. Ein Flash-Speichersystem hat deshalb für gewöhnlich eine größere Anzahl von DQs und damit eine Vielzahl von Bitleitungs-Treibern und Leseverstärkern, die parallel betrieben werden.

# 2.4 Algorithmen

Die Lese-, Programmier- oder Löschoperationen auf dem beschriebenen Speicherfeld erfordern komplexe Algorithmen. Ziel der Algorithmen ist, dass die Daten so in das Speicherfeld eingeschrieben werden, dass der Dateninhalt jederzeit zuverlässig gelesen werden kann und dass bei Bedarf eine Veränderung der Daten durch Löschen und Neuprogrammierung möglich ist.

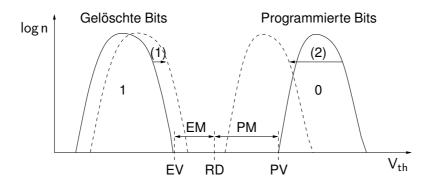

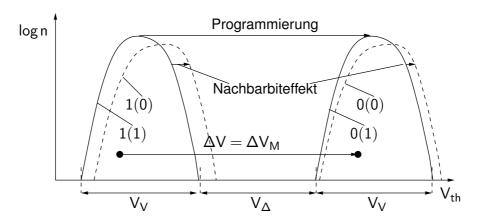

Aufgrund der physikalischen Prozesse mit den beschriebenen stochastischen Komponenten, die bei der Programmierung und dem Löschen angewendet werden, sowie aufgrund anderer systematischer und zufälliger Abweichungen sind die Schwellspannungen der Speicherzellen, die zu einem logischen Pegel gehören, in ihrer Häufigkeit um einen Zentralwert zufällig verteilt. Ein typisches Beispiel dieser Häufigkeitsverteilung wird in Abb. 2.13 gezeigt. Neben den Verteilungen unmittelbar nach dem Programmieren und

dem Löschen sind auch die typischen Verschiebungen der Schwellspannungsverteilungen nach langer Datenhaltezeit qualitativ dargestellt: Die Schwellspannung der gelöschten Bits steigt durch die sogenannte *Raum-Temperatur-Drift* kurz nach dem Löschen leicht an [BPE02], während die Schwellspannung der programmierten Bits im Vergleich dazu durch den Speicherverlust (Retention Loss) stärker absinkt [Jan03].

Bei der Leseoperation muss nun sicher entschieden werden können, zu welcher Verteilung und damit zu welchem logischen Pegel ein gelesenes Bit gehört. Um diese Sicherheit während der gesamten Datenhaltezeit und unter dem Einfluss verschiedenster Störungen garantieren zu können, werden Sicherheitsabstände (*Margins*) zwischen den Verteilungen eingefügt. Der Lese-Referenzwert *RD* muss so gewählt werden, dass er zwischen den beiden Verteilungen liegt. Der Abstand der Lesereferenz zum höchsten Schwellspannungswert der Verteilung der gelöschten Bits *EV* wird als *Erase Margin* (EM) bezeichnet und bestimmt die Sicherheit, mit der logische "1"-Werte gelesen werden können. Der Abstand der Lese-Referenz zum niedrigsten Schwellspannungswert der Population der programmierten Bits *PV* wird *Program Margin* (PM) genannt und bestimmt die Sicherheit des Erkennens einer gespeicherten logischen "0". Typische Werte für den Erase Margin und den Program Margin sind 500 mV bzw. 1100 mV [SLCE06].

Zur Ausführung der komplexen Algorithmen, die die Erzeugung einer solchermaßen "sicheren" Verteilung der Schwellspannung erlauben, sind in Flash-Systemen entweder Finite-State-Maschines oder programmgesteuerte Mikrocontroller implementiert. Die Grundzüge dieser Algorithmen werden im Folgenden erläutert.

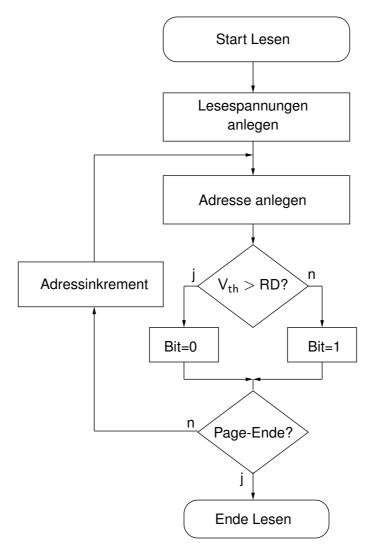

### 2.4.1 Lesealgorithmus

Das Auslesen einer Speicherseite des Speicherfelds beginnt, wie in Abb. 2.14 dargestellt, mit dem Einstellen der notwendigen Wortleitungs- und Bitleitungsspannung für den Lesebetrieb. Zu diesem Zweck werden im Schaltkreis die entsprechenden Ladungspumpen und Spannungsregler eingeschaltet. Durch das Anlegen der Speicheradresse wird mittels der X-Dekoder-, YMUX- und Select-Transistoren die zu aktivierende Speicherseite und der auszulesende Speichertransistor, meist zunächst der erste Transistor der Speicherseite, ausgewählt. Dabei wird der YMUX derart angesteuert, dass das auszulesende Bit mit dem niedrigeren Potential verbunden wird, also an der Sourceseite des Speichertransistors anliegt. Wie in Abschnitt 2.2.1 beschrieben wurde, erfolgt nun das Auslesen des Transistors im Leseverstärker durch einen Vergleich mit dem Lese-Referenzwert *RD*.<sup>2</sup>

Das Auslesen der Speicherseite erfolgt parallel in einer Vielzahl von DQs. Die gelesenen Bits aller DQs können, wie in Code-Flash-Speichern üblich, sofort über die Datenausgänge ausgegeben werden oder, wie bei Daten-Flash-Speichern verbreitet, in einem Pufferspeicher gesammelt werden.

Als nächster Schritt wird die neue Adresse angelegt, typischerweise durch das Inkre-

<sup>&</sup>lt;sup>2</sup>Obwohl technisch eigentlich ein Vergleich mit einem Referenzstrom erfolgt, werden die Referenzwerte meist als äquivalente Schwellspannungswerte angegeben.

**Abbildung 2.14:** Algorithmus für das Auslesen einer Speicherseite (Page); RD ist die Lese-Referenzspannung.

mentieren der aktuellen Adresse. Dadurch wird innerhalb der Speicherseite das nächste Bit und gegebenenfalls der nächste Speichertransistor ausgewählt. Der Vergleich mit der Lese-Referenz, die Ausgabe bzw. Zwischenspeicherung der DQ-Daten und das Adressinkrement wiederholen sich, bis die komplette Speicherseite ausgelesen ist. Als Ergebnis stehen bei Daten-Flash-Speichern nun die Daten der Speicherseite in den Pufferspeichern für die Ausgabe über die Datenleitungen des Schaltkreises zur Verfügung.

Es soll darauf hingewiesen werden, dass der Vergleich im Leseverstärker auch gegen andere Referenzwerte als den Lese-Referenzwert *RD* erfolgen kann. Diese Option wird in den nachfolgend beschriebenen Programmier- und Löschalgorithmen verwendet.

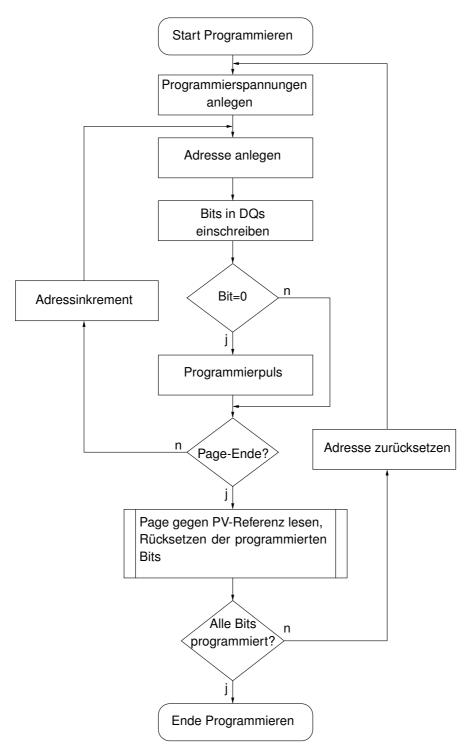

#### 2.4.2 Programmieralgorithmus

Zur Vorbereitung der Speicherseiten-Programmierung werden die Daten der zu programmierenden Speicherseite in einen Pufferspeicher eingeschrieben. Zu Beginn des Programmieralgorithmus werden die Ladungspumpen und Spannungsregulatoren eingeschaltet und auf die notwendigen Wortleitungs- und Bitleitungsspannungen eingestellt. Durch Anlegen der Speicheradresse wird der betreffende Speichertransistor, gewöhnlich der erste Transistor der adressierten Speicherseite, mit Hilfe der X- und Y-Dekoder und der Select-Transistoren ausgewählt. Das zu programmierende Bit liegt auf der Drainseite des Transistors. Aus dem Pufferspeicher werden die Datenwerte der parallel programmierten, adressierten Bits gelesen und in die zugehörigen DQs eingeschrieben. Soll in einer DQ ein Bit programmiert werden, ist sein korrespondierender logischer Datenwert üblicherweise "0". In diesem Fall wird an den Transistor ein Drainspannungspuls von  $\sim 5 \,\mathrm{V}$  und  $\sim 200 \,\mathrm{ns}$  Dauer angelegt [MDS<sup>+</sup>02]. Anschließend wird die Adresse inkrementiert, dadurch das nächste Bit ausgewählt und, nach dem Schreiben des zugehörigen Datenwerts aus dem Pufferspeicher in die DQ, gegebenenfalls programmiert. Dieser Vorgang wiederholt sich bis zum letzten zu programmierenden Datenwort, meist bis zum Ende der Speicherseite.

Nachdem nun ein erster Programmierzyklus abgearbeitet wurde, wird die komplette Speicherseite, wie in Abschnitt 2.4.1 beschrieben, ausgelesen (*Program-Verify*). Im Unterschied zum normalen Speicherseiten-Lesealgorithmus wird aber mit einer anderen Referenz, der Program-Verify-Referenz *PV*, verglichen. Mit Hilfe dieses Vergleichs wird festgestellt, ob die Schwellspannung eines zu programmierenden Bits bereits einen vorgeschriebenen Minimalwert überschritten hat. Ist der PV-Schwellspannungswert überschritten, kann der zum Bit korrespondierende Datenwert im Pufferspeicher auf den logischen Wert "1" gesetzt werden, da in diesem Fall keine weiteren Programmierpulse für das Bit generiert werden. Anderenfalls bleibt der logische Datenwert des Bits im Pufferspeicher unverändert.

Nachdem die Adresse auf das erste zu programmierende Bit der Speicherseite zurückgesetzt wurde, wird die Programmier-Lese-Sequenz wiederholt ausgeführt bis im Endergebnis jedes der zu programmierenden Bits der Speicherseite das geforderte PV-Niveau überschritten hat.

**Abbildung 2.15:** Algorithmus für das Programmieren einer Speicherseite (Page); PV ist die Program-Verify-Referenzspannung.

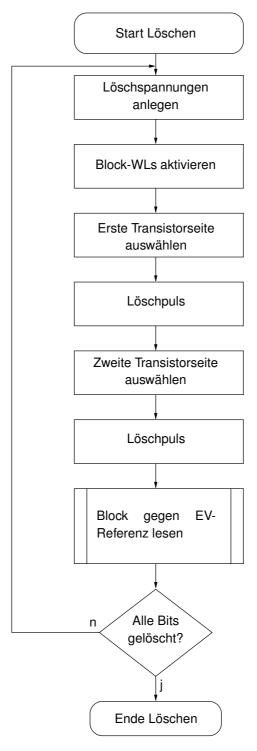

### 2.4.3 Löschalgorithmus

Ähnlich zu den Lese- und Programmieralgorithmen werden beim Löschen zuerst die Ladungspumpen und Spannungsregler eingeschaltet und auf die negative Wortleitungs- und positive Bitleitungsspannung eingestellt. Alle zum Block gehörenden Wortleitungen werden aktiviert und mit der Wortleitungsspannung beschaltet. Die beiden Bits des Speichertransistors werden in zwei aufeinander folgenden Schritten gelöscht, wobei die jeweils zu löschenden Bits an den Drainseiten der Transistoren anliegen und parallel mit dem Bitleitungstreiber verbunden werden, während die anderen Seiten der Transistoren im Allgemeinen unbeschaltet bleiben. Durch einen drainseitigen Löschpuls von 4...7V und einer Dauer von ungefähr  $\sim 250\,\mu\mathrm{s}$  wird die erste Gruppe von Bits gelöscht und nach Vertauschung von Source und Drain die zweite Gruppe [BPE02].

Anschließend wird der ganze Block gelesen und mit einer Erase-Verify-Referenz *EV* verglichen. Bei diesem Lesevorgang ist allerdings nicht der konkrete Dateninhalt relevant, sondern nur, ob mindestens ein Bit des Blocks eine Schwellspannung hat, die größer als die EV-Referenz ist. Ist dies der Fall, erhält der komplette Block einen weiteren doppelseitigen Löschpuls. Das Löschen ist beendet, wenn alle Bits des Blocks eine Schwellspannung unterhalb der EV-Referenzschwellspannung haben.

## 2.5 Multilevel-Speicher

Um die Speicherdichte immer weiter zu erhöhen, wird aktiv an der Entwicklung der Multilevel-Speicher auf der Basis der ONO-Speichertransistoren mit lokaler Ladungsspeicherung gearbeitet. Bei dieser Technologie können auf jeder Seite der Speichertransistoren mehrere Bits gespeichert werden [PLS<sup>+</sup>06].

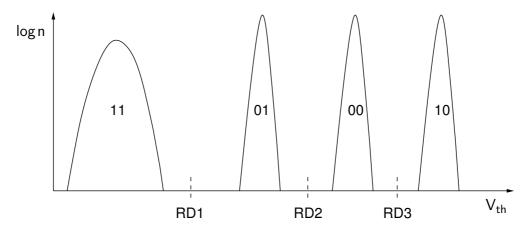

In Abb. 2.17 wird eine typische Häufigkeitsverteilung der Schwellspannungen eines Multilevel-Produkts gezeigt [PLS<sup>+</sup>06][SLCE06], in dem pro Transistorseite zwei Bits gespeichert sind. Aufgrund der beiden gespeicherten Bits sind vier Populationen in den Häufigkeitsverteilungen der Schwellspannungen zu erkennen. Jeder Population ist eine Bitkombination zugeordnet. Weil beim Auslesen zwischen den Populationen unterschieden werden muss, sind drei Lese-Referenzwerte RD1...RD3 vorhanden.

Da also bei Multilevel-Speichern die Anzahl der Schwellspannungspopulationen exponentiell mit der Bitzahl steigt, die maximalen Schwellspannungswerte aber nicht beliebig gesteigert werden können, müssen die Schwellspannungsverteilungen schmaler werden und/oder die Sicherheitsabstände zwischen den Verteilungen sinken.

Um bei der Programmierung derartig schmale Verteilungen zu erhalten, werden Algorithmen eingesetzt, die zunächst aggressiv mit großen Schwellspannungsinkrementen die Zielschwellspannung grob einstellen und dann mit kleineren Schwellspannungsinkrementen eine Feinjustage der Zielschwellspannung erlauben [PLS<sup>+</sup>06].

Beim Lesen werden Fehlererkennungsmechanismen eingesetzt. Wird zum Beispiel ein Lesefehler durch eine verschobene Schwellspannungsverteilung erkannt, wird versucht,

**Abbildung 2.16:** Algorithmus für das Löschen eines Blocks; EV ist die Erase-Verify-Referenzspannung.

**Abbildung 2.17:** Typische Häufigkeitsverteilung der Schwellspannungen in einem Multilevel-Speicher

die Lese-Referenz so nachzuführen, dass sie sich wieder optimal in der Lücke zwischen den Verteilungen befindet [PLS<sup>+</sup>06].

Trotz dieser fortschrittlichen Mechanismen ist die genaue Kenntnis der physikalischen Mechanismen, die eine Verteilungsverbreiterung oder Verteilungsverschiebung bewirken, unerlässlich und deshalb sind einige dieser Effekte Gegenstand dieser Arbeit.

# 3 Schwellspannung von MOS-Transistoren

In diesem Abschnitt werden die halbleiterphysikalischen Modellierungsmethoden zur Berechnung der Schwellspannung von konventionellen kurzkanaligen MOS-Transistoren und die dazugehörigen mathematischen Lösungsmethoden vorgestellt und bewertet. Ausgehend von dieser Untersuchung wird ein Modell zur Berechnung der Schwellspannung von Standard-MOS-Transistoren mit kurzen Kanallängen eingeführt und Schlussfolgerungen diskutiert.

## 3.1 Grundlagen zur Modellierung der Schwellspannung

#### 3.1.1 Bändermodell

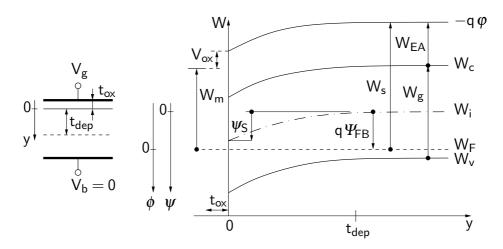

Das Bändermodell ist eine Veranschaulichung der Energie der Halbleiterelektronen. In Abb. 3.1 wird das Bändermodell einer Metall-Oxid-Halbleiter-Struktur (MOS-Struktur) gezeigt. Der Halbleiter sei p-dotiert, so dass sich die Fermienergie  $W_F$  unterhalb der Eigenleitungsenergie  $W_i$  befindet. Der Halbleiter sei in x-Richtung unendlich ausgedehnt, um Randeffekte auszuschließen. Der Halbleiter befinde sich im thermodynamischen Gleichgewicht, es gelte  $V_{gb}=0$ .

Im Bändermodell Abb. 3.1 sind der Verlauf des Eigenleitungsniveaus  $W_i$ , der Energien der Leitungs- und Valenzbänder  $W_c$  bzw.  $W_v$ , des Ferminiveaus und des Makropotentials  $\varphi$  entlang eines Schnittes parallel zur y-Achse dargestellt.

Aufgrund des Unterschieds der Austrittsarbeiten der Elektronen aus dem Metall  $W_m$  und dem Halbleiter  $W_s$  sowie aufgrund von Ladungen an der Grenzfläche Oxid-Halbleiter  $Q_{ss}''$  oder von Ladungen im Isolator  $Q_{ox}''$  verschieben sich die Energieniveaus im Halbleiter an der Grenzfläche zum Oxid so weit, bis sich über dem Gateisolator eine Spannung  $V_{ox}$  einstellt, bei der die Gesamtladungsbilanz des Halbleiters ausgeglichen ist. Weit im Inneren des Halbleiters sind die energetischen Verhältnisse aber weiter ungestört, so dass sich im Allgemeinen eine Verbiegung der Bänder an der Halbleiteroberfläche, selbst bei  $V_{gb}=0$ , ergibt. Diese Bandverbiegung kann kompensiert werden, indem eine entsprechende Gate-Bulk-Spannung, die Flachbandspannung  $V_{fb}$ , extern angelegt wird. Unter Einfluss dieser Bandverbiegung entsteht im Halbleiter, auch im thermodynamischen Gleichgewicht, eine Raumladungszone.

Den potentiellen Energien des Bändermodells können auch elekrostatische Potentiale zugeordnet werden. Ebenso wie bei den potentiellen Energien, ist die Lage des Bezugsniveaus der Potentiale beliebig. Wir definieren das Potential  $\psi$  auf das Eigenleitungsniveau und das Potential  $\phi$  auf das Ferminiveau im Halbleiterinneren bezogen, woraus sich für

Abbildung 3.1: Bändermodel einer MOS-Struktur mit p-Substrat

p-Halbleiter die Folgerung  $\Psi_{FB} > 0$  ergibt. Es gilt:

$$\psi, \phi = -\frac{W}{q} + \text{const.} \tag{3.1}$$

Die Flachbandspannung berechnet sich mit diesen Vorgaben unter Bezugnahme auf Abb. 3.1 zu [Pau72]:

$$V_{fb} = \underbrace{\left(-\Psi_{FB} - \frac{W_g}{2q} - \frac{W_{EA}}{q} + \frac{W_m}{q}\right)}_{\Phi_{MS}} - \frac{Q_{ss}''}{C_{ox}} - \frac{Q_{ox}''}{C_{ox}}.$$

(3.2)

Die Dichte der Ladungsträger n bzw. p ist mit dem Potential im thermodynamischen Gleichgewicht verknüpft über:

$$n = n_{0p} \exp\left(\frac{\Psi}{U_T}\right), \tag{3.3}$$

$$p = p_{0p} \exp\left(-\frac{\Psi}{U_T}\right), \tag{3.4}$$

wobei  $n_{0p}$  und  $p_{0p}$  die Gleichgewichtsdichten der Elektronen bzw. Löcher tief im p-Halbleitersubstrat bezeichnen und  $n_{0p} p_{0p} = n_i^2$  gilt.

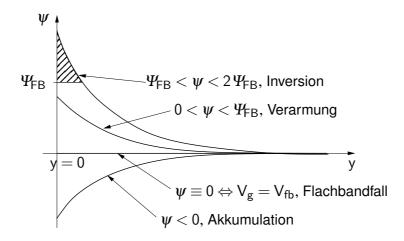

In Abb. 3.2 wird der Verlauf des Potentials  $\psi$  für die verschiedenen Betriebsarten eines p-Halbleiters dargestellt. Wir unterscheiden:

- 1. **Akkumulation:** Das Potential ist negativ. Dadurch werden in der Raumladungszone mehr Majoritätsladungsträger als im Halbleiterinneren ausgebildet.

- 2. **Flachbandfall:** Das Potential ist überall gleich Null. Dieser Flachbandfall wird mit  $V_{gb} = V_{fb}$  eingestellt.

Abbildung 3.2: Betriebsfälle einer MOS-Struktur mit p-Substrat

- 3. **Verarmung:** Das Potential ist positiv, erreicht aber nicht das Ferminiveau  $\Psi_{FB}$ . In diesem Fall überwiegt in der Raumladungszone immer noch die gleiche Ladungsträgerart wie innerhalb des Halbleiters, allerdings mit niedrigerer Dichte als dort.

- 4. **Inversion:** Das Potential ist größer als  $\Psi_{FB}$ . Es gibt in diesem Gebiet eine höhere Dichte der Minoritätsladungsträger des Halbleiterinneren als der entsprechenden Majoritätsladungen. Bei einem p-Halbleiter überwiegen also in dem Inversionsgebiet die Elektronen. Sind sie in genügender Dichte vorhanden, kann in nMOS-Transistoren ein Stromtransport einsetzen.

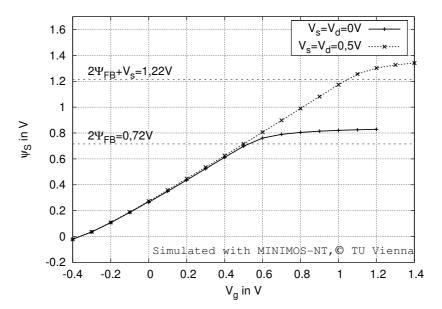

#### 3.1.2 Definition der Schwellspannung

Bildet sich eine Inversionsschicht aus, nimmt die Dichte der die Inversionsschicht bildenden Ladungsträger gemäß Gl. (3.4) exponentiell mit dem Halbleiterpotential zu. Wie in Abb. 3.3 gezeigt, erreicht das Potential einen Sättigungswert, wenn sich im MOS-Transistor die Inversionsschicht ausbildet. Wie in [Tsi99] diskutiert wurde und in Abb. 3.3 erkennbar ist, liegt dieser Sättigungswert nährungsweise, bis auf einige Vielfache der Thermospannung  $U_T$ , beim doppelten Wert des Ferminiveaus des Substrates  $\Psi_{FB}$ .

Es ist üblich, die Schwellspannung Source-referenziert zu definieren. Wir berechnen die Schwellspannung also als die Gate-Source-Spannung, die notwendig ist, um den Sättigungswert in Abb. 3.3 zu erreichen. Trotz der erwähnten nur annähernden Bestimmung des Sättigungswerts ist es üblich, die Schwellspannung  $V_{th}$  wie folgt zu definieren:

$$\psi_0 := 2\Psi_{FB} + V_s, \tag{3.5}$$

$$V_{th} := (V_g - V_s)\big|_{\psi_{S,min} = \psi_0} . \tag{3.6}$$

**Abbildung 3.3:** Simulation des Oberflächenpotentials  $\psi_S$  in Abhängigkeit vom Gatepotential  $V_g$  für  $V_s = 0V$  und  $V_s = 0.5V$  für einen Langkanaltransistor

Dabei wird weiterhin von der Annahme ausgegangen, dass sich die maximale Bandverbiegung im Halbleiter an der Oxid-Halbleiter-Grenzfläche einstellt und sich damit im Allgemeinen der Inversionskanal an der Halbleiteroberfläche ausbildet. <sup>1</sup> Aus diesem Grund wird die Definition der Schwellspannung gemäß Gl. (3.6) auf das Oberflächenpotential  $\psi_S \equiv \psi(y=0)$  bezogen [Tsi99][Pau72][ML86].

Zur Ermittlung der Schwellspannung muss also zunächst der Verlauf des Oberflächenpotentials  $\psi_S(x)$  bekannt sein. Als zweiter Schritt wird danach das Minimum des Oberflächenpotentials  $\psi_{S,min}$  berechnet und dieses zur Bestimmung der Schwellspannung des Transistors benutzt.

### 3.2 Elektrostatisches Potential

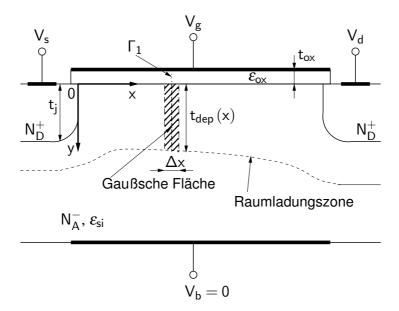

## 3.2.1 Herleitung der Differentialgleichung des Potentialverlaufs

In Abb. 3.4 wird ein Schnittbild eines MOS-Transistors gezeigt. Zur Ermittlung der Schwellspannung dieser Anordnung muss zunächst das elektrostatische Potential berechnet werden. Der Potentialverlauf in Halbleitern wird durch die Poissongleichung beschrieben:

$$\operatorname{div} \operatorname{grad} \psi = -\frac{\rho}{\varepsilon}. \tag{3.7}$$

<sup>&</sup>lt;sup>1</sup>Die Gültigkeit dieser Annahme wird für den Spezialfall der ONO-Transistoren im Abschnitt 4.2.4 eingehender untersucht.

**Abbildung 3.4:** Schnittbild eines MOS-Transistors

Unter Annahme eines p-dotierten Silizium-Halbleiters, einer Störstellenerschöpfung und einer Verarmung in der Raumladungszone unterhalb des Gates  $(p, n \ll N_A)$  läßt sich die Gleichung Gl. (3.7) für das Raumladungsgebiet  $0 \le y < t_{dep}$  folgendermaßen vereinfachen:

$$\frac{\partial^2 \psi}{\partial x^2} + \frac{\partial^2 \psi}{\partial y^2} = \frac{q N_A}{\varepsilon_{si}}.$$

(3.8)

Neben numerischen Lösungsverfahren (zum Beispiel in [GD80]) werden bei einer analytischen Lösung der Poissongleichung verschiedene halbleiterphysikalische Modellierungsmethoden und angepasste mathematische Lösungsmethoden angewendet.

Bei den Charge-Sharing-Ansätzen wird die Poissongleichung meist für Langkanaltransistoren, für die die Annahme  $\partial \psi/\partial x = 0$  gilt, gelöst. Der Einfluss von Source- bzw. Drain-Gebieten in Kurzkanaltransistoren wird bei diesen Verfahren durch eine Reduktion der effektiven Bulkladung  $qN_A$  berücksichtigt. Dazu werden die ortsfesten Ladungen in den Raumladungszonen in der Nähe von Source bzw. Drain entweder den Source-/Drain-Gebieten oder dem Bulk-Gebiet zugeordnet. Diese Zuordnung der Ladungen geschieht dabei im Allgemeinen durch eine willkürliche geometrische Aufteilung. Da sich die effektive Bulkladung durch diese teilweise Zuordnung der Ladungen zu Source bzw. Drain verringert, wird in den Charge-Sharing-Ansätzen mit Hilfe eines Reduktionsfaktors die berechnete Langkanal-Schwellspannung korrigiert [Yau74][Lee73][AS82] [Tay78]. Diese Modelle erwiesen sich für die Modellierung von kurzen Transistoren als zu ungenau [RM82].

Andere Verfahren nutzen zur Lösung der Differentialgleichung Gl. (3.8) eine Separation der Gleichung in homogenen und inhomogenen Anteil durch entsprechende An-

satzfunktionen und lösen die sich ergebenden partiellen Differentialgleichungen [RM82] [KB86]. Trennung der Variablen kann ebenfalls als ein direktes Lösungsverfahren für Gl. (3.8) verwendet werden [PK84]. Greensche Funktionen werden in [LW87] angewendet. Alle diese mathematischen Verfahren führen ebenso wie die Analyseverfahren in [PSM85][ADM95] [FTW98] auf komplizierte unendliche Reihen als Lösungsfunktion und sind somit nur schwer weiterführend mathematisch behandelbar.

Eine weitere Klasse von Lösungsverfahren nutzt Methoden der Variationsrechnung zur Lösung von Gl. (3.8) und erhält damit ebenfalls sehr komplexe Lösungen [PM89].

Eine Methode zur Transformation der zweidimensionalen Form der Poissongleichung in eine eindimensionale Form wird von [SMP88] verwendet. Dazu wird ein quadratischer Verlauf des Oberflächenpotentials vorausgesetzt und ein nichtlineares Koordinatensystem eingeführt, dass die Poissongleichung in beschränkten Bereichen nahe den Achsen dieses Koordinatensystems in eine einfachere, eindimensionale Form überführt. Zur Lösung der sich ergebenden Gleichungen werden allerdings aufwendige iterative Verfahren benötigt.

Sehr erfolgreich wurden quasi-zweidimensionale Lösungsverfahren angewendet, bei denen die partielle Differentialgleichung durch geeignete Annahmen oder Ansatzfunktionen auf eine oder mehrere gewöhnliche Differentialgleichungen abgebildet wird, welche dann im Allgemeinen einfacher lösbar sind. Diese Verfahren führen dabei häufig auf relativ einfache, analytische Lösungen, die einer weiteren mathematischen Behandlung zugänglich sind, wobei die Lösungen sehr gut mit numerischen Simulationen korrelieren [TA79][CT91][FS93][LHH<sup>+</sup>93]. Aus diesem Grund basiert die folgende Herleitung auf diesem Verfahren. Der Herleitungsweg entspricht dabei im Wesentlichen [CT91].

Zur Lösung der Poissongleichung wählen wir unter Bezugnahme auf Abb. 3.4 die folgenden Randbedingungen:

$$\psi(0,y) = V_{bi} + V_s; \qquad 0 \le y < t_i,$$

(3.9a)

$$\psi(L, y) = V_{bi} + V_d; \qquad 0 \le y < t_i,$$

(3.9b)

$$\psi(0,y) = V_{bi} + V_{d}; \qquad 0 \le y < t_{j},$$

$$\psi(L,y) = V_{bi} + V_{d}; \qquad 0 \le y < t_{j},$$

$$\frac{\partial \psi(x,y)}{\partial y} \Big|_{y=t_{dep}} = 0,$$

(3.9c)

$$\psi\left(x, t_{dep}\right) = 0. \tag{3.9d}$$

Dabei bezeichnet  $V_{bi}$  die Diffusionsspannung  $V_{bi} = U_T \ln (N_A N_D / n_i^2)$ ,  $t_j$  ist die Tiefe der Source- bzw. Drain-Gebiete und L ist die Transistorlänge.

Zunächst integrieren wir die Poissongleichung Gl. (3.8) zweimal formal über y:

$$\psi(x,y) = \frac{qN_A}{2\varepsilon_{si}}y^2 + C_1y + C_2 - \int_0^y \int_0^{y_1} \frac{\partial^2 \psi(x,y_2)}{\partial x^2} dy_2 dy_1.$$

(3.10)

Aus der Randbedingung Gl. (3.9c) ergibt sich:

$$C_1 = -\frac{qN_A}{\varepsilon_{si}} t_{dep} + \int_0^{t_{dep}} \frac{\partial^2 \psi(x, y_1)}{\partial x^2} dy_1.$$

(3.11)

Eingesetzt in Gl. (3.10) und unter Anwendung der Randbedingung Gl. (3.9d) erhalten wir:

$$C_{2} = \frac{qN_{A}}{2\varepsilon_{si}}t_{dep}^{2} - t_{dep} \int_{0}^{t_{dep}} \frac{\partial^{2}\psi(x, y_{1})}{\partial x^{2}} dy_{1} + \int_{0}^{t_{dep}} \int_{0}^{y_{1}} \frac{\partial^{2}\psi(x, y_{2})}{\partial x^{2}} dy_{2} dy_{1}.$$

(3.12)

Damit ergibt sich schließlich für  $0 \le y < t_{dep}$ :

$$\psi(x,y) = \frac{qN_A}{2\varepsilon_{si}} (t_{dep} - y)^2 - (t_{dep} - y) \int_0^{t_{dep}} \frac{\partial^2 \psi(x, y_1)}{\partial x^2} dy_1 +

+ \int_0^{t_{dep}} \int_0^{y_1} \frac{\partial^2 \psi(x, y_2)}{\partial x^2} dy_2 dy_1 - \int_0^y \int_0^{y_1} \frac{\partial^2 \psi(x, y_2)}{\partial x^2} dy_2 dy_1.$$

(3.13)

Eine Betrachtung der Gl. (3.13) lässt erkennen, dass man die Gleichung für Langkanaltransistoren aufgrund von  $\partial^2 \psi / \partial x^2 = 0$  auf den bekannten Langkanal-Potentialverlauf

$$\psi(x,y) = \psi(y) = \frac{qN_A}{2\varepsilon_{si}} (t_{dep} - y)^2$$

(3.14)

reduzieren kann.

Neben der Funktion  $\partial^2 \psi(x,y)/\partial x^2$  benötigt man zur Lösung dieser Gleichung die Tiefe der Raumladungszone  $t_{dep}=t_{dep}(x)$ . Für die Bestimmung von  $t_{dep}(x)$  betrachten wir die schraffierte Fläche in Abb. 3.4. Wenden wir das Gaußsche Gesetz auf diese Fläche an und beachten wir dabei, dass sich aufgrund der oben gemachten Näherungen nur Akzeptorladungen in der Gaußschen Fläche befinden, so kann man für kleine  $\Delta x$  formulieren:

$$Q' = -qN_A \Delta x \, t_{dep} = \varepsilon_{si} \int_0^{t_{dep}} E_x(x + \Delta x, y_1) \, dy_1 - \varepsilon_{si} \int_0^{t_{dep}} E_x(x, y_1) \, dy_1 +$$

$$+ \varepsilon_{si} E_y(x, t_{dep}) \, \Delta x - \varepsilon_{si} E_y(x, 0) \, \Delta x.$$

(3.15)

Dabei bezeichnen  $E_x$  und  $E_y$  die x-Komponente bzw. y-Komponente des elektrischen Feldes  $\vec{E}(x,y)$  und es gilt  $E_x = -\partial \psi/\partial x$  und  $E_y = -\partial \psi/\partial y$ . Es ergibt sich damit für  $\Delta x \to 0$  und unter Beachtung der Randbedingung Gl. (3.9c):

$$\frac{qN_A t_{dep}}{\varepsilon_{si}} = \int_0^{t_{dep}} \frac{\partial^2 \psi(x, y_1)}{\partial x^2} dy_1 + E_y(x, 0).$$

(3.16)

Für die Oxid-Halbleiter-Grenzfläche bei y = 0 gilt aufgrund des Gaußschen Gesetzes:

$$\varepsilon_{si} E_{v}(x,0) = \varepsilon_{ox} E_{ox} + Q_{ss}^{"}, \qquad (3.17)$$

wobei die Feldstärke  $E_{ox}$  konstant innerhalb des Oxids ist und eine Integration dieser Feldstärke entlang des Wegs  $\Gamma_1$  aus Abb. 3.4 ergibt:

$$\int_{\Gamma_1} E_{ox} \, dy = E_{ox} t_{ox} = V_g - \Phi_{MS} - \psi(x, 0) . \tag{3.18}$$

Aus Gl. (3.16) – Gl. (3.18) erhält man schließlich zusammen mit Gl. (3.13) das folgende allgemeine Gleichungssystem zur Berechnung des Potentialverlaufs:

$$\frac{qN_A t_{dep}}{\varepsilon_{si}} = \int_0^{t_{dep}} \frac{\partial^2 \psi(x, y_1)}{\partial x^2} dy_1 + \frac{\varepsilon_{ox}}{\varepsilon_{si}} \cdot \frac{V_g - V_{fb} - \psi(x, 0)}{t_{ox}}, \qquad (3.19a)$$

$$\psi(x, y) = \frac{qN_A}{2\varepsilon_{si}} (t_{dep} - y)^2 - (t_{dep} - y) \int_0^{t_{dep}} \frac{\partial^2 \psi(x, y_1)}{\partial x^2} dy_1 + \int_0^{t_{dep}} \int_0^{y_1} \frac{\partial^2 \psi(x, y_2)}{\partial x^2} dy_2 dy_1 - \int_0^{y} \int_0^{y_1} \frac{\partial^2 \psi(x, y_2)}{\partial x^2} dy_2 dy_1, \qquad (3.19b)$$

wobei die Flachbandspannung  $V_{fb}$  der Definition aus Gl. (3.2) entspricht.

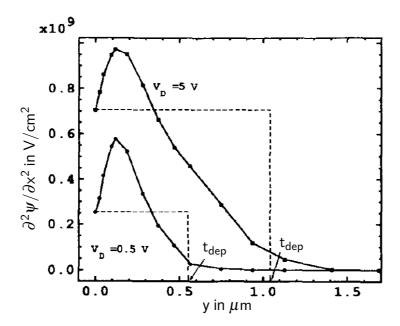

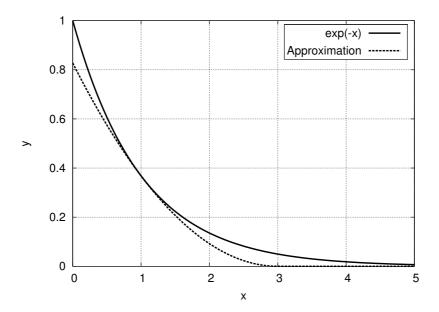

Ein Vergleich von Gl. (3.19a) und Gl. (3.19b) lässt erkennen, dass beide Ausdrücke über  $\partial^2 \psi(x,y)/\partial x^2$  und  $t_{dep}=t_{dep}(x)$  gekoppelt sind. Zur Lösung dieses Systems ist es zweckmäßig, eine Ansatzfunktion für  $\partial^2 \psi(x,y)/\partial x^2$  zu finden, die es erlaubt, die Gleichungen weiterführend mathematisch zu behandeln, gleichzeitig aber Modellierungsergebnisse liefert, die mit numerischen Simulationsergebnissen gut korrelieren. In [CT91] wurde dazu der Ansatz:

$$\frac{\partial^2 \psi(x,y)}{\partial x^2} = \frac{\partial^2 \psi(x,0)}{\partial x^2} = \frac{\mathrm{d}^2 \psi_S(x)}{\mathrm{d}x^2}$$

(3.20)

gewählt. Das bedeutet, dass angenommen wird, dass sich die Krümmung des Potentialverlaufs in x-Richtung über die gesamte Tiefe der Raumladungszone nur wenig ändert und dass sie mit der Krümmung an Oxid-Halbleiter-Grenzfläche übereinstimmt. Obwohl sich diese Wahl nicht streng rechtfertigen lässt und Abb. 3.5 zeigt, dass die Krümmung doch entlang der y-Richtung variiert, kann man ebenfalls in dieser Abbildung erkennen, dass der Mittelwert des Krümmungsverlaufs über die gesamte Tiefe der Raumladungszone gut mit dem entsprechenden Mittelwert der Ansatzfunktion übereinstimmt. Das Einfach-Integral in Gl. (3.19b) und das Integral in Gl. (3.19a) entsprechen aber genau diesem Mittelwert. Insofern können diese Integrale gut angenähert werden. Die

**Abbildung 3.5:** Verlauf von  $\partial^2 \psi / \partial x^2$  und Approximation für verschiedene Drain-Spannungen [CT91]; Mit freundlicher Genehmigung © 1991 IEEE

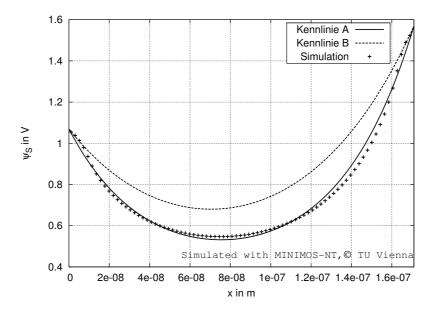

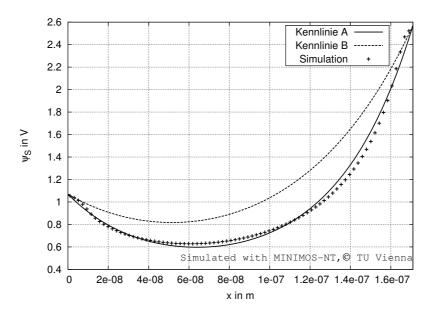

Doppelintegrale in Gl. (3.19b) werden aber durch den gewählten Ansatz weniger gut repräsentiert. Die sich aus dem Ansatz ergebende Lösung muss deshalb unbedingt mit numerischen Simulationsergebnissen verglichen werden.

Anzumerken ist, dass auch in der Modellbildung nach [FS93] und [LHH<sup>+</sup>93] der Mittelwert der Krümmung des Potentials über die Tiefe der Raumladungszone mit dem Krümmungswert des Oberflächenpotentials gleichgesetzt und zur Berechnung des Oberflächenpotentials verwendet wird. Die Ansätze nach [CT91], [LHH<sup>+</sup>93] und [FS93] führen deshalb im Weiteren auf strukturell ähnliche Gleichungen.

Der Vorteil der Ansatzfunktion Gl. (3.20) liegt darin, dass die Krümmung des Potentialverlaufs **nicht** mehr von der Koordinate y abhängig ist und dass damit die Integrale einfach gelöst werden können. Es ergibt sich aus Gl. (3.19a) und Gl. (3.19b) folgendes Gleichungssystem:

$$\frac{\mathrm{d}^2 \psi_S(x)}{\mathrm{d}x^2} + \frac{2}{(t_{dep} - y)^2} \cdot \psi(x, y) = \frac{q N_A}{\varepsilon_{si}}$$

(3.21a)

$$\frac{\mathrm{d}^{2}\psi_{S}(x)}{\mathrm{d}x^{2}} + \frac{\varepsilon_{ox}}{\varepsilon_{si}} \cdot \frac{V_{g} - V_{fb} - \psi_{S}(x)}{t_{ox} t_{dep}} = \frac{q N_{A}}{\varepsilon_{si}}.$$

(3.21b)

Um dieses Gleichungssystem zu lösen, berechnen wir das Oberflächenpotential, also das Potential für y = 0. Aus den erwähnten Gründen ist dieser Potentialverlauf auch für die weiterführende Schwellspannungsmodellierung maßgebend. Mit y = 0 und  $\psi_S(x) = 0$

$\psi(x,0)$  vereinfacht sich das Gleichungssystem zu:

$$\frac{\mathrm{d}^{2}\psi_{S}(x)}{\mathrm{d}x^{2}} + \frac{2}{t_{dep}^{2}} \cdot \psi_{S}(x) = \frac{qN_{A}}{\varepsilon_{si}}$$

$$\frac{\mathrm{d}^{2}\psi_{S}(x)}{\mathrm{d}x^{2}} + \frac{\varepsilon_{ox}}{\varepsilon_{si}} \cdot \frac{V_{g} - V_{fb} - \psi_{S}(x)}{t_{ox} t_{dep}} = \frac{qN_{A}}{\varepsilon_{si}}.$$

(3.22a)

$$\frac{\mathrm{d}^{2}\psi_{S}(x)}{\mathrm{d}x^{2}} + \frac{\varepsilon_{ox}}{\varepsilon_{si}} \cdot \frac{V_{g} - V_{fb} - \psi_{S}(x)}{t_{ox} t_{dep}} = \frac{q N_{A}}{\varepsilon_{si}}.$$

(3.22b)

Ein Vergleich dieses Gleichungssystems mit den Herleitungen in [LHH<sup>+</sup>93] und [FS93] zeigt, dass in beiden Arbeiten ebenfalls zur Berechung des Potentialverlaufs Gl. (3.22b) verwendet wird. Der Unterschied zu diesen beiden Vorgehensweisen liegt in der unterschiedlichen Modellierung der Tiefe der Raumladungszone  $t_{dep}(x)$ .

In [LHH $^+$ 93] wird für den Parameter  $t_{dep}$  die Verarmungslänge von Langkanaltransistoren bei konstantem Oberflächenpotential von  $\psi_S = 2 \Psi_{FB} + V_{sb}$  verwendet. Damit wird  $t_{dep}$  als unabhängig von x modelliert. Da diese Näherung nur sehr ungenau ist, wird ein Fittingparameter  $\eta$  eingeführt.

In [FS93] wird die Verarmungslänge  $t_{dep}$  ebenfalls aus einer Langkanalbetrachtung abgeleitet. Allerdings wird die Abhängigkeit von  $\psi_S(x)$  und damit die Ortsveränderlichkeit von  $t_{dep}$  im Rahmen einer linearen Näherung berücksichtigt.

Im vorhergehenden Gleichungssystem kann die Verarmungslänge aus Gl. (3.22a) hergeleitet werden:

$$t_{dep} = \sqrt{\frac{2 \,\varepsilon_{si} \,\psi_{S}}{q N_{A}}} \cdot \frac{1}{\sqrt{1 - \frac{\varepsilon_{si}}{q N_{A}} \frac{\mathrm{d}^{2} \psi_{s}}{\mathrm{d}x^{2}}}},$$

$$= t_{dep,L} \cdot \frac{1}{\sqrt{1 - \frac{\varepsilon_{si}}{q N_{A}} \frac{\mathrm{d}^{2} \psi_{s}}{\mathrm{d}x^{2}}}},$$

$$(3.23)$$

$$= t_{dep,L} \cdot \frac{1}{\sqrt{1 - \frac{\varepsilon_{si}}{q N_A} \frac{d^2 \psi_s}{dx^2}}},$$

(3.24)

wobei  $t_{dep,L}$  die Verarmungslänge von Langkanaltransistoren darstellt. Eine Beschreibung des Oberflächenpotentials gemäß Gl. (3.22a) und Gl. (3.22b) modelliert also sowohl die Spannungsabhängigkeit von  $t_{dep}$ , als auch die Auswirkung von Kurzkanaleffekten auf die Verarmungslänge und stellt damit eine Erweiterung der Ansätze von [FS93] und [LHH<sup>+</sup>93] dar.

Durch Einsetzen von Gl. (3.24) in Gl. (3.22b) und durch anschließende Umstellung erhält man folgende Differentialgleichung:

$$\frac{\varepsilon_{ox}}{t_{ox}} \left( V_g - V_{fb} - \psi_S \right) = q N_A \sqrt{1 - \frac{\varepsilon_{si}}{q N_A} \frac{\mathrm{d}^2 \psi_s}{\mathrm{d} x^2}} \cdot t_{dep,L} \left( \psi_S \right). \tag{3.25}$$

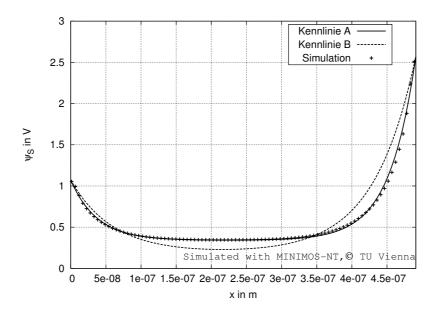

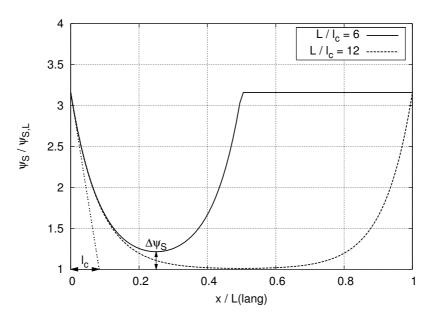

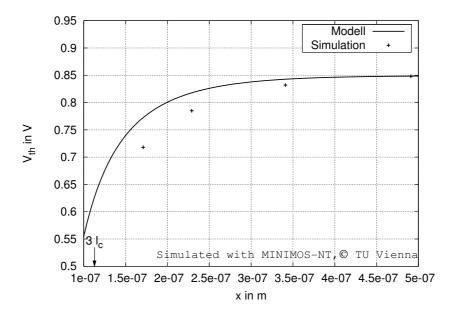

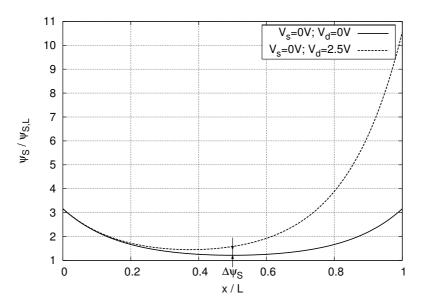

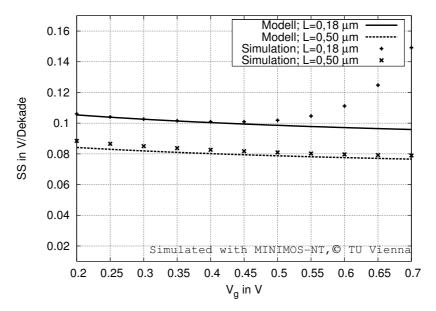

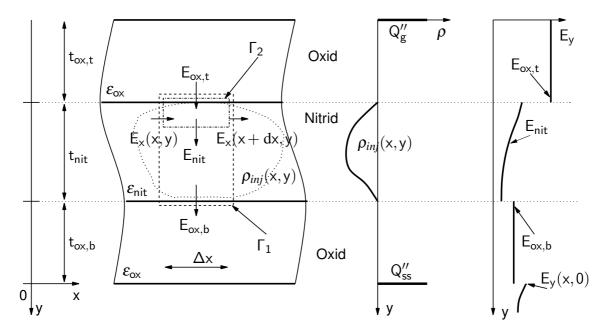

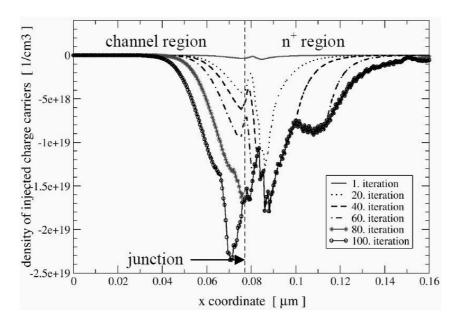

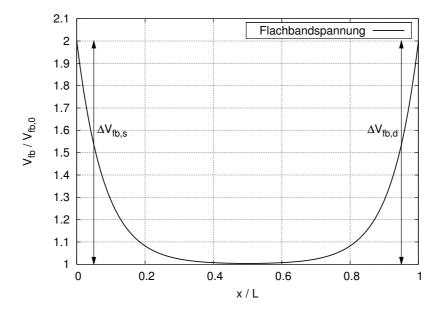

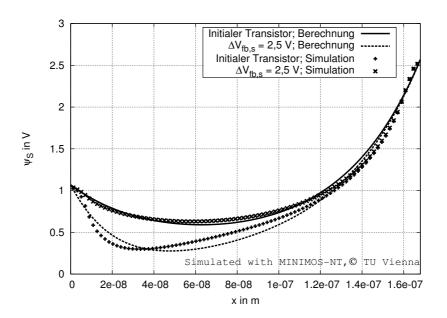

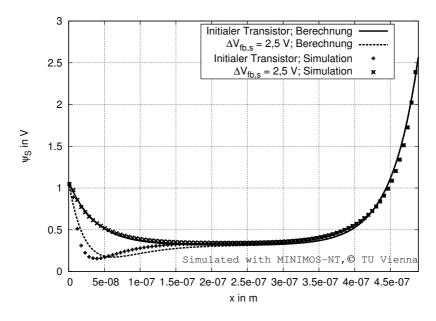

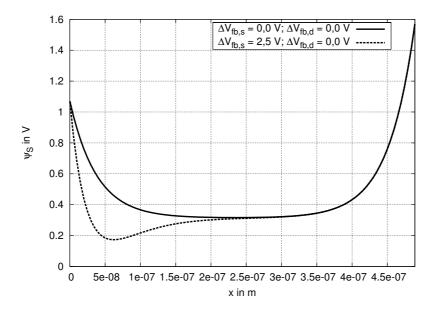

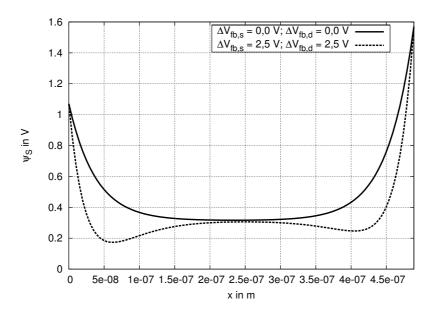

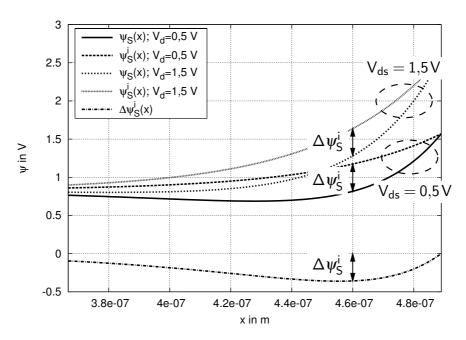

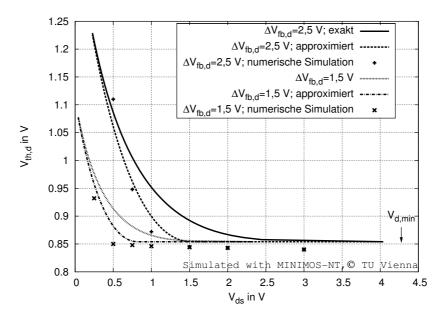

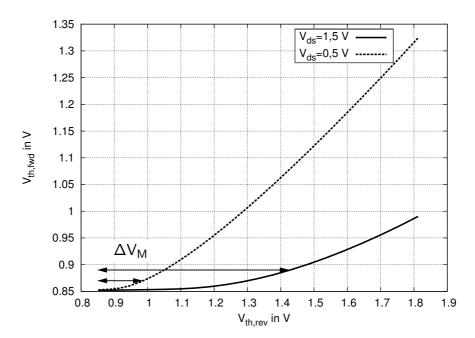

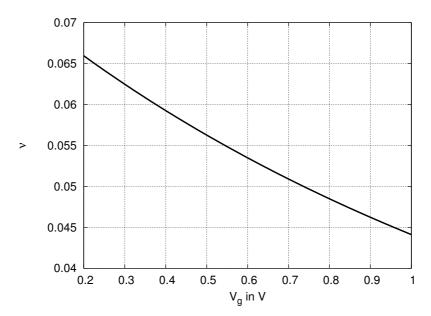

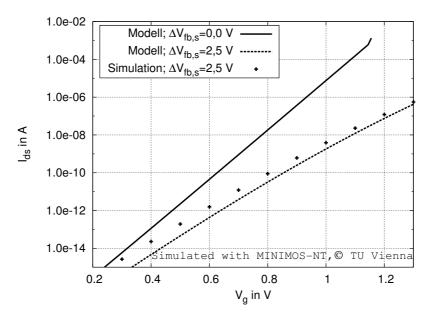

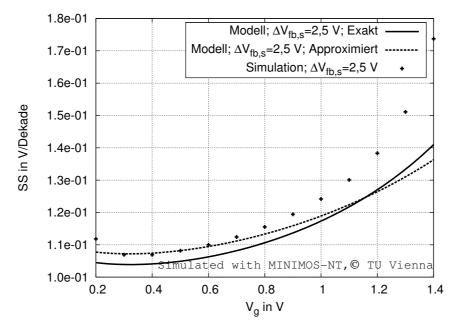

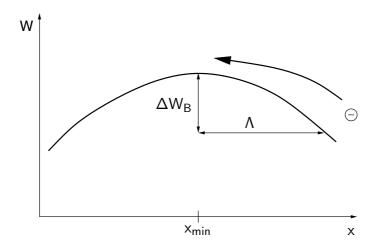

[CT91] verzichtet auf die Lösung dieser Differentialgleichung und auf eine damit verbundene Diskussion der Folgerungen. Da hier jedoch eine weiterführende Analyse durchgeführt werden soll, wird Gl. (3.25) in dieser Arbeit näherungsweise gelöst. Dazu wird Gl. (3.25) um  $d^2\psi_s/dx^2 = 0$  und  $\psi_S = \psi_{S0}$  linearisiert. Man erhält: